|

|

引言) s0 w+ n1 O6 Z; H

在半导体技术持续发展的背景下,高性能计算(HPC)应用的需求正在快速增长。本文探讨台积电创新的新一代系统级芯片集成(SoIC)平台,通过先进的三维堆叠技术推进摩尔定律的发展[1]。* ?; q! }/ o6 T) d1 u

m0ecpq0q1ft640338747.png

4 X0 A! Z' ~# {# T2 U M

3 L! u& l7 |1 t' x, r4 u; c# }1

4 w) N6 C% I* q* [% YSoIC架构及工艺流程

; C% \1 q8 o& h' _7 a A6 ~ g台积电新一代SoIC技术的基础在于独特的芯片堆叠方法。该技术通过SoIC键合将顶层芯片连接到下方的晶圆或芯片,两个芯片的器件面相对。这种配置实现了异构配对,可以将先进制程的计算芯片通过SoIC键合放置在包含存储器或外围电路的成熟制程底层芯片上。; L) J; H* @% v# T& S

0aqmsyt0qxq640338847.png

$ x+ O0 P+ K% E9 F) ^5 M图1:台积电新一代SoIC技术的工艺流程图,展示了从SoC工艺到最终TSV显露的关键步骤。

8 V& U1 t+ G; m

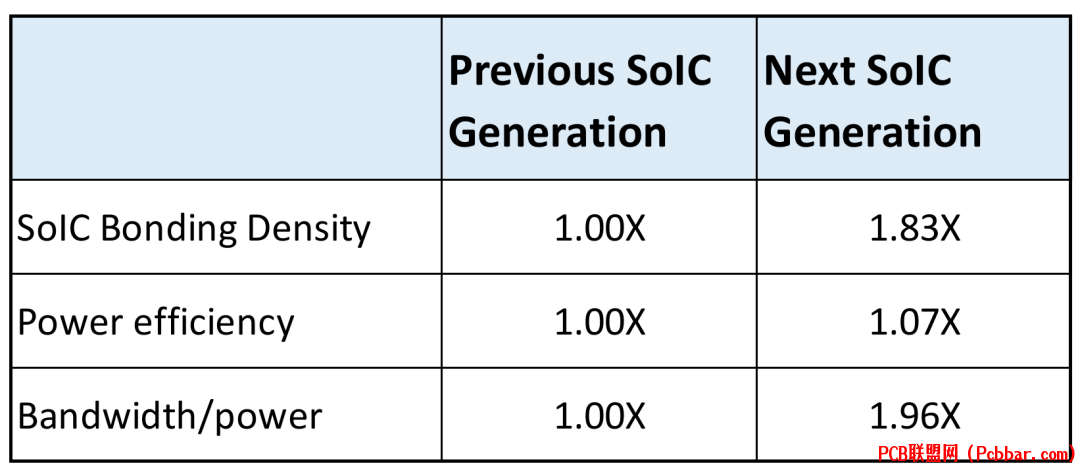

3 L) v Y/ P) B与前代技术相比,新一代SoIC技术在性能方面取得了显著提升: O% C, E% }% F. \7 s

jiamfhgdfic640338947.png

2 ?3 R) G/ D, Y m; R

2 ?3 R) G/ D, Y m; R

表I:性能对比显示SoIC键合密度(1.83倍)、功耗效率(1.07倍)和带宽/功耗比(1.96倍)均有明显提升。+ v# K- V& C+ a( J; h

U1 P7 a: t) Z# A

24 m/ a! b2 j2 m8 G5 k5 P7 r

先进制造工艺与可靠性特征

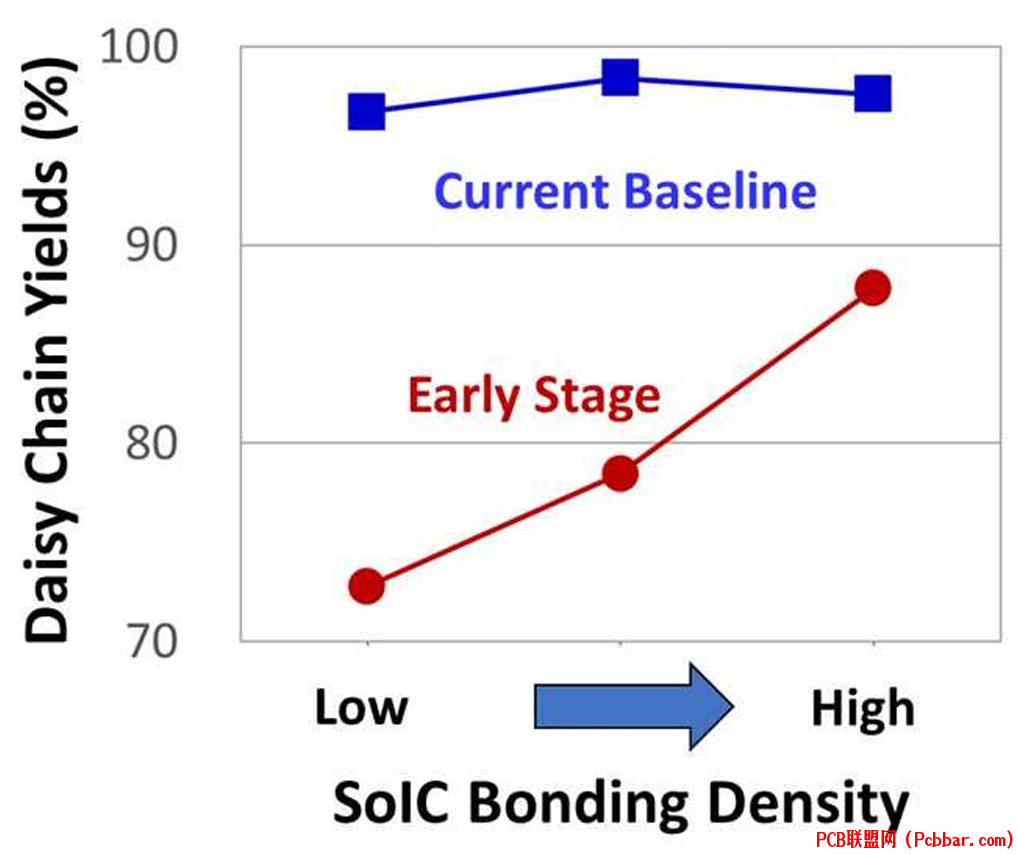

3 Q' _- ^8 ~3 T制造工艺采用了精密的良率管理技术。通过细致的工艺优化,该技术在保持高良率的同时实现了键合密度的显著提升。

8 d( \! H( {) V, T; h

uc2mkgbqs4m640339047.png

/ \8 H: m# f5 n& n$ i, k

/ \8 H: m# f5 n& n$ i, k

图2:展示SoIC键合密度与菊链测试良率关系的图表,显示从早期阶段到当前基准的性能提升。8 ~! p0 }- ]* _0 A B7 S, @

3 d) T% f) V. I6 N3 n

连接可靠性已经通过大量测试得到验证。该技术在数十亿个连接中展现出优异的良率统计数据:8 n' Z& y% ?( U1 x8 b

p1qlbconnuy640339147.png

! j# t- y& f$ `

! j# t- y& f$ `

图3:菊链连续性良率分布图,显示单片晶圆上7.6亿个SoIC键合连接的测试结果。0 e$ [! T# J9 J. H+ @4 {

" u# x- P4 @; _3 c0 m

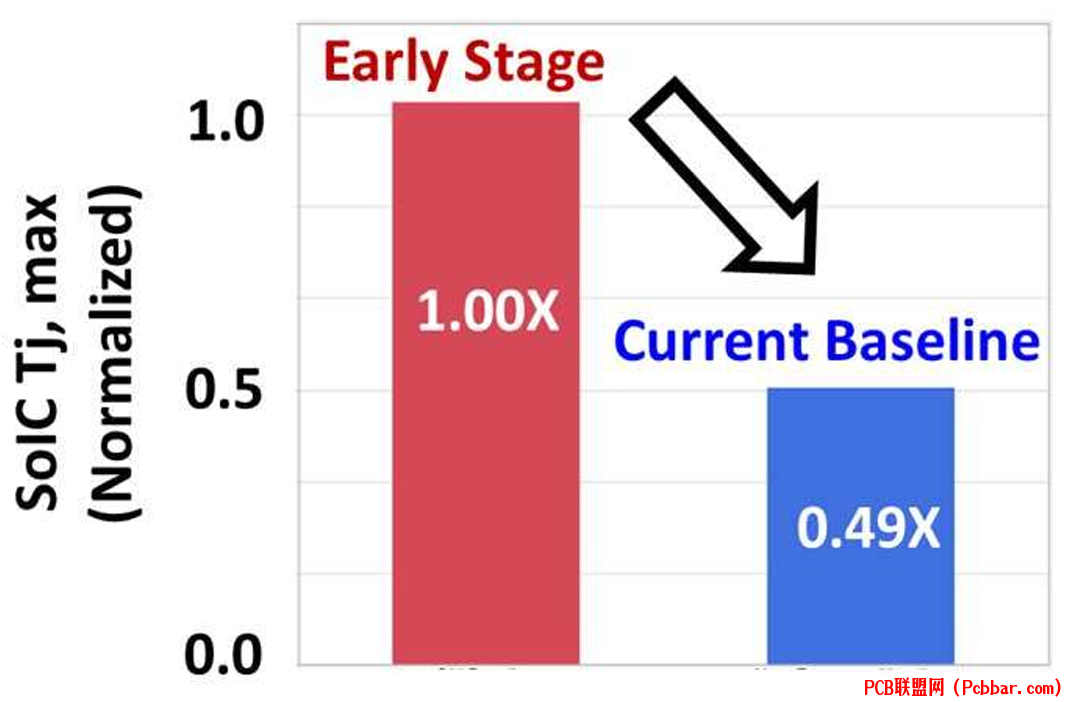

热管理方面的改进尤为显著:

% c% A8 a7 p. D6 f2 Z4 _

5ptmpmc4wo3640339248.png

& r! J; s. I! C k图4:柱状图显示热阻降低,通过新工艺使最高结温降低约50%。+ y* F% Z) u4 @7 m. d3 d+ a

0 f. v9 W& Q& K4 h0 Z' U6 v

3

% q3 z. ~& \ M5 n1 `: H! b( V/ b电气性能与集成能力- I: W% g) Y* @# I/ W% `

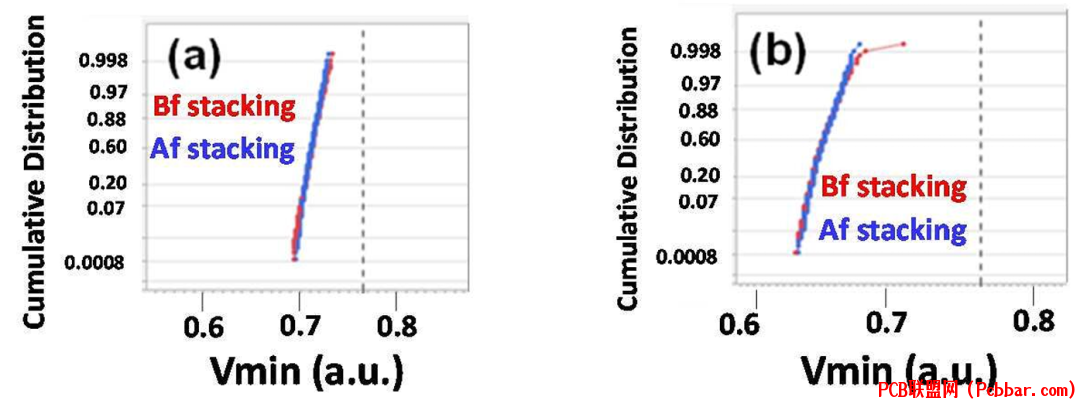

平台的电气特性已通过多种测试方法得到全面验证。在SoIC堆叠前后,晶体管性能的稳定性得到确认:

0 H! I5 C! `: ]% H

3hpfg3pgyd5640339348.png

- D+ G3 z$ p$ i1 u, M. o" M$ V图5:详细比较图显示NMOS和PMOS器件的Isat-Vt和Isat-Ioff特性,证实SoIC堆叠前后性能保持一致。8 [ U2 C" X. ]

8 r9 Q" O2 X2 I该平台在高性能存储器集成方面表现出色:

% U9 D! M, ~7 f5 z# U3 `1 c

ucjft4acdrw640339448.png

1 P# L8 C9 I4 _0 w- N; k# j* z% R; \" f图6:MBIST结果显示高电流(48.4MB)和高密度(50.0MB)配置的SRAM良率和最小工作电压(Vmin)。, t0 Y2 H( k/ n( y- E! ]7 i

5 j9 N) v, ~$ C( W

4# z( ^& [/ K B9 y) V J$ K

带宽与能效成果

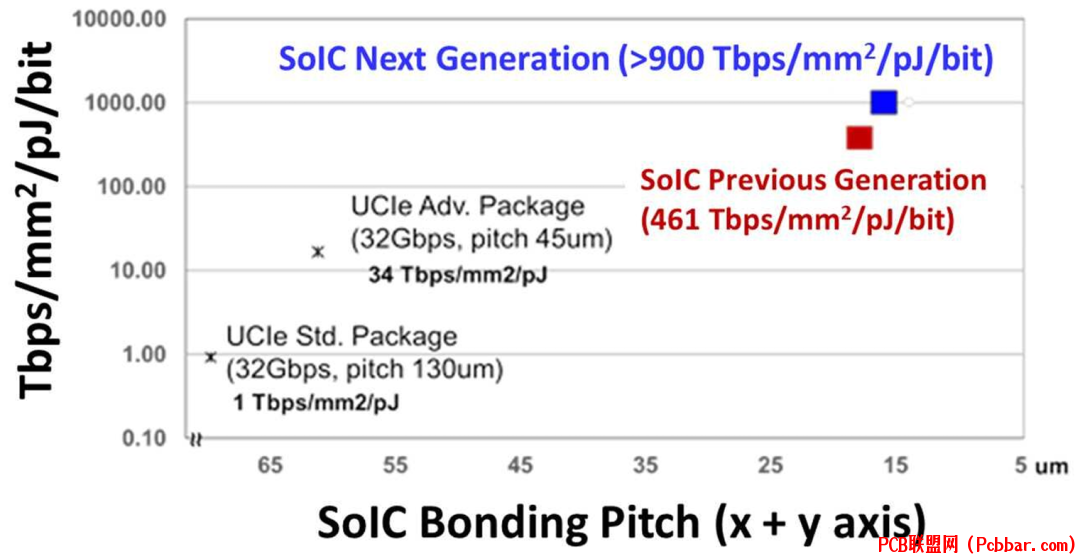

( p# H6 W. o! K. r y; c# V该平台实现了出色的带宽密度性能,建立了新的行业标准:% o2 T7 [6 q3 i* s# {% m7 E1 x: H/ _

qu3ffdhhbuh640339548.png

) t8 j$ y2 {! G, h+ o+ A

) t8 j$ y2 {! G, h+ o+ A

图7:带宽密度/能效与SoIC键合间距关系图,显示新一代技术达到>900 Tbps/mm2/pJ/bit。

( R6 d3 m# S! {* K) J% k3 a+ m

6 A7 u ]6 Q2 _+ z1 t54 C; Q7 V+ P3 ?! r `' I5 o( f8 ?

可靠性与保护机制

% l- c+ V) O8 J6 j" M- b# @! L* u该平台包含了完善的ESD保护和可靠性特征:" r; u0 a' E+ u6 ~

igqntxhfl3v640339648.png

* c/ ~& L/ r4 a9 u$ n图8:ESD电流分布显示实施防ESD工艺后的性能改进。

/ P) C" R4 ^/ K1 g- U: C) e' _' Z& B, Y

可靠性测试包括全面的封装级验证:

# v3 {+ p: J9 D7 Z. n6 | r

jlbkv5glj5u640339748.png

/ p8 s2 U+ c. b; \表II:封装可靠性和应力迁移测试结果汇总,显示所有标准可靠性测试均通过。3 \5 [) r Y/ J- d4 L

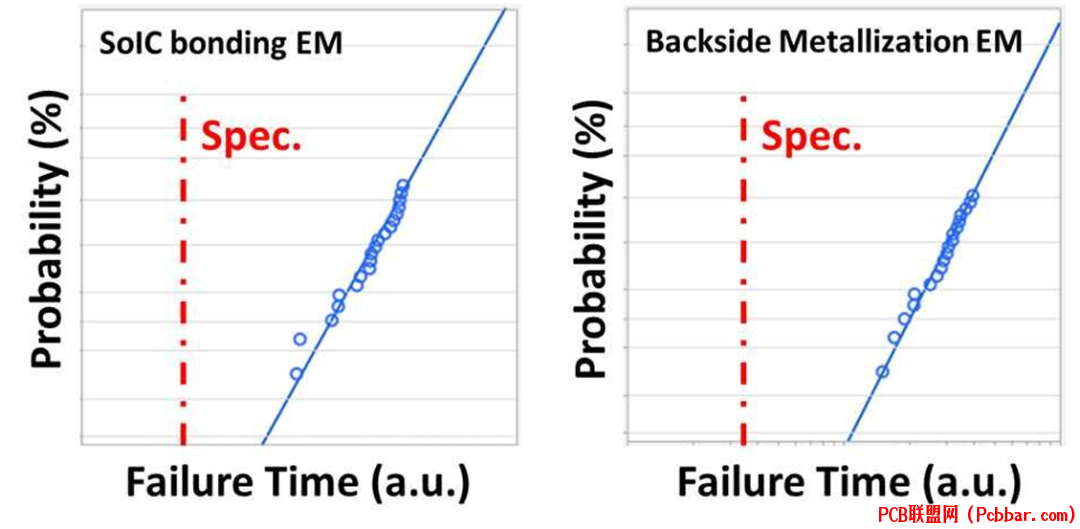

- Q5 V' h" j( `电迁移特性已经过全面验证:

, g9 {, P1 E4 |% n

vto2qg3rfne640339849.png

2 ?( b$ {7 N2 I6 J# u. f图9:SoIC键合和背面金属化的电迁移测试结果,显示可靠性符合规格要求。+ z, y$ y, d8 Z/ }) A4 a

2 x+ y" U }! G. m5 }/ u

新一代SoIC技术在三维集成能力方面实现了重大进展,为HPC应用提供了优异性能。该平台在电气、热学和可靠性方面的全面验证确保了大规模生产的准备就绪,而其先进特性为半导体行业的芯片间集成设立了新标准。

! r8 B3 b2 @3 U) s* N6 _+ _1 }

# Y0 Q) ~, H) w该技术与台积电先进封装解决方案的成功集成,以及与领先制程节点的兼容性,使其成为未来HPC创新的重要支持技术。随着半导体集成技术的不断发展,这一平台为下一代计算解决方案奠定了坚实基础。: @4 K1 O1 R$ ]3 g$ o! Y

5 f" ]' @2 \0 x) `: L

参考文献9 S# s: R$ h1 J3 l2 J

[1] Y.-M. Chen et al., "Next Generation TSMC-SoIC? Platform for Ultra-High Bandwidth HPC Application," in 2024 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2024.: u) Q# E+ @- k

END7 i! G: V1 L4 h9 V+ d/ Z4 |

. x- U" Y1 b% B2 b# \

软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。

b6 X: `1 C! b; U8 o点击左下角"阅读原文"马上申请

8 S. J9 m2 G3 U F9 i$ U- O/ o2 \7 ^

欢迎转载

/ }1 h: T% c# y2 n# b% i7 Q8 M# H- k9 j' C5 P: D

转载请注明出处,请勿修改内容和删除作者信息!9 D3 S$ X5 \) V) V

6 Y8 F" C% }1 o+ i. t9 J

8 X9 E9 @( X+ D/ y4 `2 p0 n4 k4 u1 @+ w- D6 H. w

1g2juqvlfr5640339949.gif

/ e% h- U: P: z9 ?+ C0 @

/ e% h- U: P: z9 ?+ C0 @

: J0 S* P' {' U% ?. t

关注我们

a6 g: |2 @& K" m/ \& B" ^/ {0 o2 X1 c) h

( a' L, H* B/ @( V; h* T

mtadtgxhmql640340049.png

" m; Z( p6 [2 ]$ L( a! c: ~ |

3 W* |3 R' n/ @4 Y" L

zhka0gdzazk640340149.png

% z9 Z* ]9 ]9 }" N; B( O- { | : M# N5 x3 B# r) g7 L

gg3pitnkt0t640340249.png

7 I; p$ v& g6 S) g8 }& H

7 I; p$ v& g6 S) g8 }& H

|

" ]# [5 G) Z i& J

3 l n+ G1 t8 I& G6 o8 x; u$ _/ g/ L- \- {9 m/ ~# z1 e: s) W

9 e H$ |9 U' K0 D$ ?" H关于我们:: a) R; Q6 U5 p( v8 X T7 B

深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。# \2 }- x" P+ ?4 q6 g

: ]' K# K9 _2 r# j

http://www.latitudeda.com/

$ G3 u7 \. R {: S6 W2 k: p(点击上方名片关注我们,发现更多精彩内容) |

|