|

|

引言

5 {: x+ d1 s- D w5 t! @% P近年来,对能效高的人工智能(AI)推理运算的需求推动了硬件架构的创新。虽然二维架构如脉动阵列和计算存储器(CIM)设计已显示出优势,但随着CMOS技术缩放接近极限,这些设计面临着局限性。本文探讨三维集成技术如何克服这些挑战,同时考虑能效和环境影响[1]。- `: s- I) t3 B- Y5 @

2avmsmji5oe6404566512.png

r1 J2 T' g$ H8 `0 H

0 ^/ b/ ^# Y. T0 _/ ]1

, S! \/ a7 S5 E/ v& d' n硬件架构与实现; r& V+ h6 R1 J- W

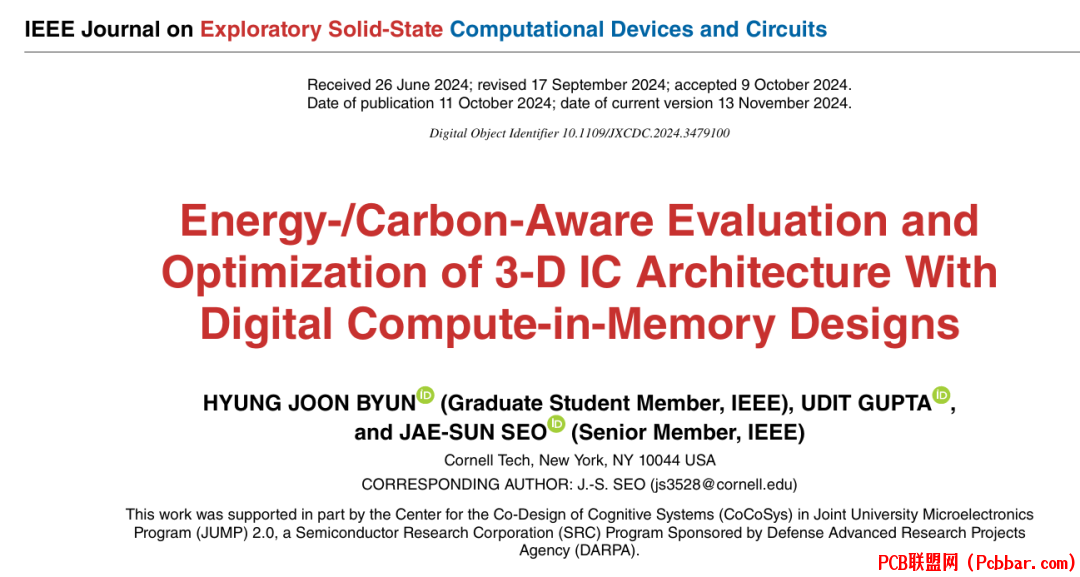

研究中探索的基本架构将传统脉动阵列与数字计算存储器(DCIM)在二维和三维配置中结合。如论文图1所示,存在四种主要架构方法:

4 r8 R+ c% C7 x$ d

aoyb3ily3g36404566612.png

! b4 V9 M5 ~% d' I

! b4 V9 M5 ~% d' I

图1:不同硬件配置展示:(a)二维脉动阵列设计,(b)二维DCIM阵列设计,(c)具有分离计算资源的三维方案1设计,以及(d)具有存储器叠加逻辑的三维方案2设计。- Y1 ]9 v: |2 C# |- r" k6 p# u

) ~! a# j% ~$ g( H

基准二维脉动阵列架构包含用于激活和权重的片上缓冲器,处理单元(PE)由8位MAC单元和寄存器组成。二维DCIM阵列用具有计算能力的存储器单元替代传统存储器,在保持相同吞吐量的同时减少数据移动。对于三维实现,主要探索两种方案:

7 l. P. ~" q, @: w三维方案1:资源在通过面对面连接的两个芯片之间平均分配,每个芯片都具备计算和存储能力。; N$ F D9 S2 t7 b2 G" l

三维方案2:采用存储器叠加逻辑方法,将缓冲器放置在计算阵列上方的顶层芯片上。3 x( U5 @+ \7 Z- ]* t [

) l( F4 ^) j0 ]0 i" E

这些架构利用了台积电SoIC等先进的三维制造技术,实现了小于10微米间距的高密度混合键合。这使得高带宽垂直连接成为可能,同时减少了线长。( L* r6 M& o7 F: }

/ F/ S- W; j0 P* `

2

7 I# o3 `; P% ^性能分析框架

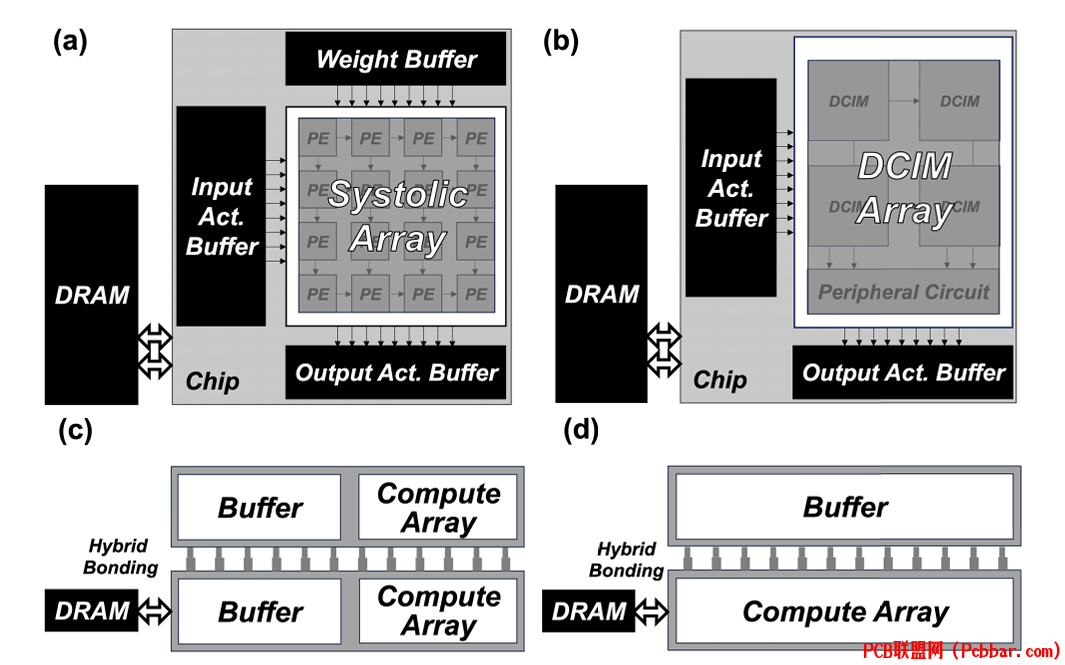

) Z& w; @9 e1 |7 \! s: n4 M为评估这些架构,开发了综合建模框架,如图2所示: O6 A3 n( `# A& T& ^8 h$ N0 _6 N

a1w25rucbs06404566712.png

4 x! R- d: _) n3 ?

4 x! R- d: _) n3 ?

图2:提出的框架概述,显示从工作负载分析到能量、面积和碳排放估算的流程。

6 n9 k q( W! V+ ?& V( i) o+ L E3 k5 G. E+ Y- l$ Q; u) [

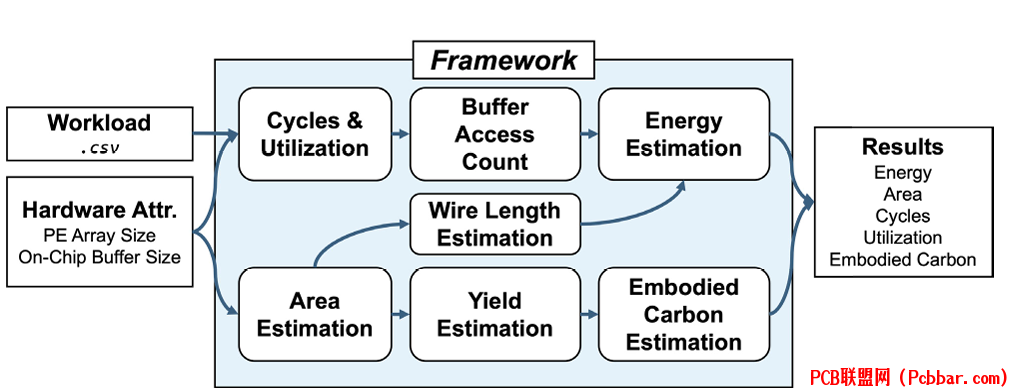

计算阵列尺寸(如图3所示)直接影响性能:

( l& D+ |) o; z- `

irdv32rxlyd6404566812.png

& X j" t7 M0 X+ W0 F

& X j" t7 M0 X+ W0 F

图3:(a)具有DR行和DC列的计算阵列尺寸,以及(b)输入/输出激活和权重的工作负载尺寸。

7 @9 v# g: C$ x5 H" W+ Z

; F f6 P7 u6 b0 D( D5 K' w3

& M- X' V6 A+ i3 i能效分析. }% s% z) [4 H1 h( M' B8 v$ m

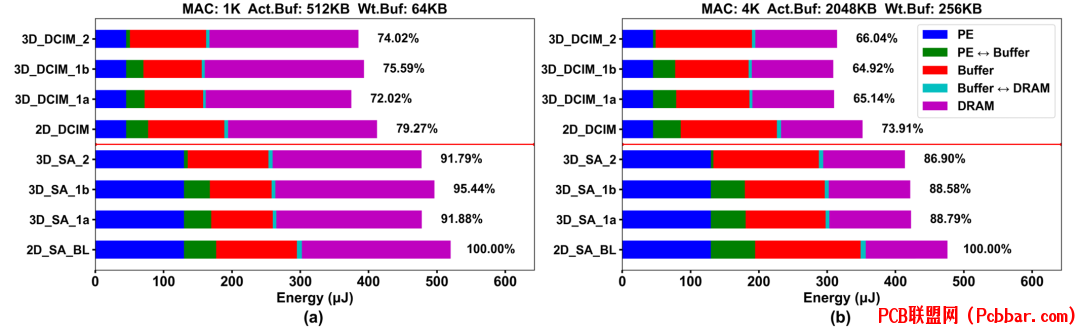

能耗分析揭示了不同架构选择之间的权衡。图4提供了详细的分类:

# l( z- `2 o3 \6 S* |; S! L

34rdauuku3j6404566912.png

3 X0 u+ v# n# ]2 z9 h; z2 u

3 X0 u+ v# n# ]2 z9 h; z2 u

图4:PE阵列大小为(a)1K和(b)4K时,脉动阵列和相应DCIM阵列计算MobileNet工作负载的能耗分析。

) n) R5 H& V9 Y, S0 ?2 ~! P" v5 J( h6 Y

结果表明,三维DCIM架构与二维脉动阵列相比可实现高达42.5%的节能。这种改进来自以下几个因素:垂直连接中的线长减少激活缓冲器大小利用率提高DCIM单元中的权重存储更高效DCIM设计中每次MAC运算能耗更低4 ~& h/ ~' T# U* p$ n0 P& ]

[/ol]

6 q0 g. X* N+ E' S" I& O, n+ [% b能源节省与面积效率之间的关系如图5所示:& _7 |, Y' W1 `8 b8 w

h0tokjxmqqa6404567012.png

: I) o; N' r2 O# t图5:相对于二维基准标准化的ResNet-50工作负载的能源节省与面积节省关系。7 i% T4 }" h; c1 _

2 A8 Q% o# y s+ X; ^# E$ r

44 H# _" |/ m7 v! A

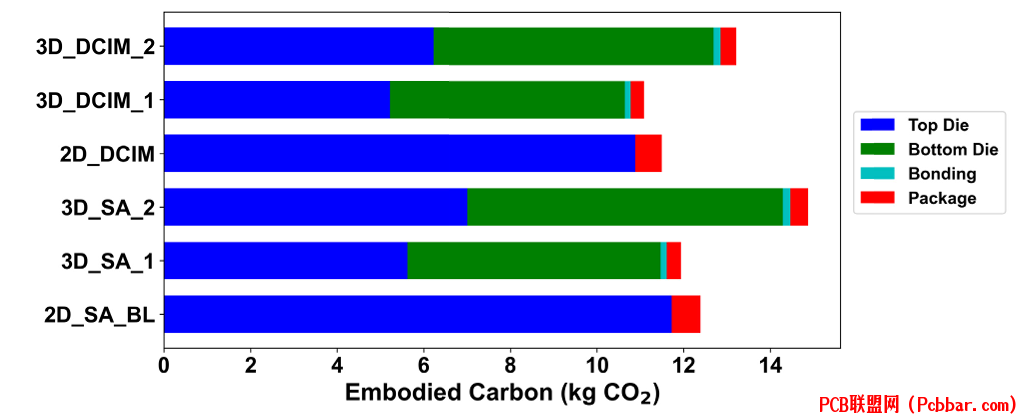

碳足迹考量

* P2 g- w8 v/ g) b; Z现代硬件设计中的环境影响分析已成为关键考量。该框架包含详细的碳足迹分析,如图6所示:

/ q( Z! `: X* x6 ~7 f" m# N- [ y

rwnneghczs46404567112.png

0 X% r$ V# k+ H: E

0 X% r$ V# k+ H: E

图6:1K PE阵列大小的不同硬件架构的碳排放量。

! b: t6 u8 L. i5 u e d( z5 r8 E- @, g' d2 a5 Q( W) M& ~

碳分析显示,虽然三维集成能提供性能优势,但也带来了特定的环境影响因素:TSV开销为底层芯片碳足迹增加约13%混合键合引入约7%的额外碳开销层间芯片尺寸匹配影响总碳足迹

, D5 E; ]% z: `) ~, {' k7 V[/ol]! S& c# C; T* z% n( @% n

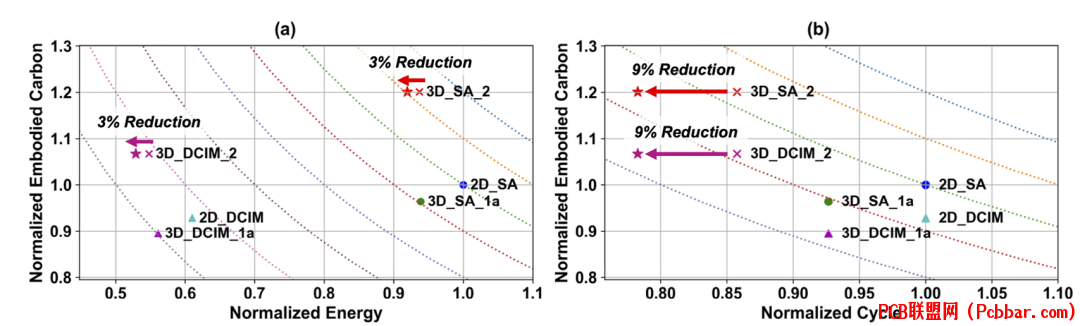

碳足迹与性能指标之间的关系如图7所示:

, z& W5 e3 X8 z4 u. y3 i& ~

bpednhekg5e6404567213.png

) y/ }( ^: ?( r. v5 z图7:(a)能量和(b)周期相对于碳排放量的关系,其中碳排放量、能量和周期均相对于二维基准进行标准化。0 w0 P# b/ V/ P( Z

: x2 B& \/ o) }- Z" Q( v7 m56 A# ]: g$ A) r4 V# v# j

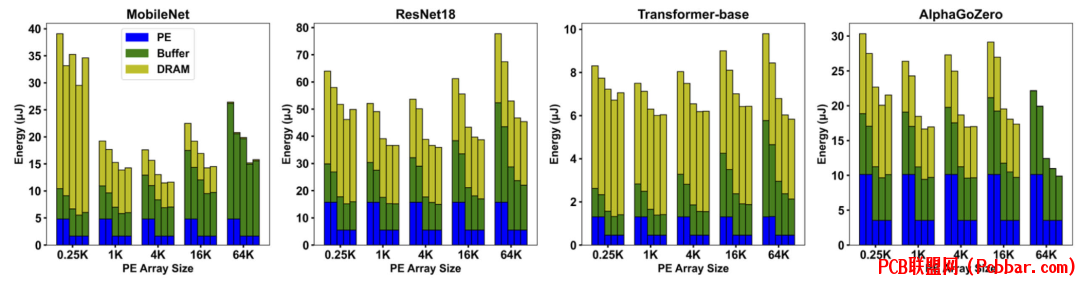

高级性能优化

4 {5 C9 T( O2 o4 S研究显示了在不同AI工作负载中的多项优化机会。图8展示了各种架构在不同AI模型中的表现:7 O, l3 q9 ?/ l

x3j3wenxdbs6404567313.png

7 h* N8 ^2 Z: [0 r$ [图8:在不同AI工作负载下,三维DCIM架构在不同PE阵列大小下的总能耗平均值比较。/ @; E+ h# N4 L% u

1 T. Y' x. m; U2 C

对于权重较大且通道较浅的工作负载,三维SA_1方案在工作负载映射方面显示出一些效率损失,在使用1K PE大小时,某些网络(如ResNet-18)的周期增加28%到40%。这种效率损失使利用率从二维基准的96%降低到69%-86%。

n$ E# L/ J" @ O/ q0 ]3 M' l: O

4 I% P, n- o( ?3 q' ]7 d但随着层权重维度减小和通道加深,三维SA_1方案显示出明显改善。对于ResNet-18,三维SA_1a平均仅比二维基准多7.0%的周期和低3.7%的利用率,而三维SA_1b方案仅多2.2%的周期和低1.0%的利用率。 R' P+ U9 F# }/ @

& n4 `: u# r+ E5 N; k三维SA_2方案通过将缓冲器垂直置于MAC阵列上方,实现了更优性能,支持同时权重更新,将每次折叠的周期减少到DR + DC + T ? 1。这使ResNet-18的周期减少11.5%,利用率提高5.08%。" Q# q3 m( G6 |6 ]8 h2 l" W

. E5 f1 U% u6 f4 Y2 ]7 @- @. G6 {7 @

6

4 y; Y. A7 a/ F# _碳排放分析细化

! r9 _# A: \* n6 h* j碳排放估算在不同PE阵列大小的扩展中显示出额外的复杂性。图9提供了这些关系的见解:

* i' x. T) j D: S) A9 c3 U7 i

nppwbwvtach6404567413.png

% W2 J8 e! H& O! V- r图9:各PE阵列大小相对于二维基准芯片面积的碳排放标准化结果,显示了不同架构方法的扩展效应。, L7 G5 i9 x# |, |* @

( k6 ~3 g' T5 `

分析显示,对于大规模设计(≥100 mm2),三维架构能有效减少碳足迹。然而,对于较小规模设计(如0.25K PE阵列),由于芯片面积小导致产率改善有限,三维架构实际上会增加碳开销。% y) h4 X% h$ Q+ D/ u

. Y+ C1 ?$ E) g- |0 R

当考虑存储器叠加逻辑配置(三维SA_2和三维DCIM_2)时,芯片面积不匹配成为关键因素。在这些配置中,如果缓冲器芯片大小超过计算阵列芯片大小,总芯片面积必须匹配较大尺寸,实际上增加了总碳足迹。这种效应在脉动阵列实现中特别明显,显示约29.3%的面积开销,而DCIM实现显示较低的3.4%开销。

1 I# d6 d' j% E. m" \" t! y, s# `6 [( G! C3 _! {! m

7; \- `2 X! c( V$ R6 e! e

未来设计思考

0 J1 z- `4 n8 H, l研究结果为将来的三维集成电路设计与DCIM提供了数项重要考量:对于小于1K PE阵列的设计,纯三维集成(三维SA方案和三维DCIM_2)相比二维脉动阵列设计优势有限,三维DCIM_1是例外。较大规模设计从三维集成中获益更多,特别是当结合三维SA_1和三维DCIM_1方案时,这得益于产率提升和芯片面积不匹配减少带来的更好布局。不同三维方案的选择应考虑目标工作负载特性,因为通道深度和权重维度显着影响各种架构的效果。混合键合和TSV的碳足迹开销必须与潜在性能提升进行权衡,尤其是对于较小规模设计,产率提升可能无法抵消额外的碳成本。

{. Z' V% [7 |7 |3 e( A' L[/ol]. [; ^" } s/ f- K; v

8

0 m7 A& ^& f9 @+ o* s总结与展望. R% l! X( \& v: J! `

基于研究结果,可得出以下主要结论:

3 S0 w0 z2 j7 J7 G7 Z5 @在能效方面,三维DCIM架构展现出显着优势,与二维脉动阵列相比,在8种不同AI工作负载中平均实现42.5%的能耗节省。, [6 O- s4 t6 H

垂直数据映射方式显着影响性能。对于ResNet-18等网络,三维SA_1a和三维SA_1b方案分别实现了7.0%和2.2%的周期增加,但利用率仅降低3.7%和1.0%。

0 h8 v6 z; g$ a# }三维DCIM_1方案在能效和碳足迹方面表现最佳,特别适合大规模设计。对于小型设计,需要仔细评估三维集成带来的额外制造复杂性是否值得。

+ G. C M3 l" }5 ~5 E& B) ]芯片面积不匹配问题在存储器叠加逻辑设计中尤为突出,导致高达29.3%的面积开销,这直接影响碳足迹和成本效益。9 o6 G: I0 l$ _. M0 K

[/ol]$ H0 J6 B$ A* w

三维集成与DCIM技术的结合为下一代AI加速器提供了实用解决方案。然而,设计人员需要根据具体应用场景、规模需求和环境影响进行细致权衡。特别是在考虑采用三维架构时,应充分评估工作负载特性、芯片面积匹配度以及环境因素,以实现最佳的综合性能。- N4 j/ M+ d: f7 t' l1 c9 x! X. c

1 R6 C5 t: b) e0 S5 ?+ y: d$ }- l

参考文献$ `! y; ]% _3 @' s' I

[1] H. J. Byun, U. Gupta, and J.-S. Seo, "Energy-/Carbon-Aware Evaluation and Optimization of 3-D IC Architecture With Digital Compute-in-Memory Designs," IEEE Journal on Exploratory Solid-State Computational Devices and Circuits, vol. 10, pp. 98-106, 2024, doi: 10.1109/JXCDC.2024.3479100.5 ^( w3 B. f4 |1 x

END* h: `( U: i. X

8 S8 L; T( M" c; E4 x& I$ i" L7 B$ U软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。

/ ]. @& @( k3 P6 X/ U0 t点击左下角"阅读原文"马上申请

r, y, E F/ O# e/ ]6 W6 g

' {" B7 b4 N- E. r3 q: @0 r欢迎转载4 s$ k Q) J$ }, {- o

# [* |) X9 l6 s. V2 ~1 q: Q

转载请注明出处,请勿修改内容和删除作者信息!( F* n9 l5 A) I, D$ r/ r: B

. F! H. d4 v/ I! d

$ W2 I1 x, Y2 t' h7 A0 N6 T

8 ]1 ~; t4 w+ |- d4 b7 _

ghkpeie510u6404567513.gif

, G" J8 e( Y* n' g/ X! v# K

, G" J8 e( Y* n' g/ X! v# K

( o, r4 o- G9 Z) e- N

关注我们

2 ^6 S. {8 C/ c0 x6 P$ }: o0 B. t& a$ u9 O

. y( S- Q: p% M9 u% n" P

ma0ojxbbkjg6404567613.png

# I6 N# J; m3 z8 y/ W: @

# I6 N# J; m3 z8 y/ W: @

|

. L5 h$ O) C; o7 M0 a2 N0 ?

vrmqlsx3f3v6404567713.png

; i6 \# T+ P! z' \ |

9 A, V( v6 C3 Z1 ]" o* H1 Y) q

so0jaxzm5ys6404567813.png

/ ]# b2 [! q' Z) q; `. p |

9 L* C. e; n' y9 M. u0 I7 {

- P# x# R0 ^ K P% p& n

. E' l5 | b2 [5 a9 G2 W. T# q0 B. A! q7 z4 b h1 m/ V- W+ `

关于我们:

" a& l0 V: ^/ m z8 j深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。0 j2 c; x( y8 {, K8 [& j

' z! U) p# P% ^! n, c% Fhttp://www.latitudeda.com/9 Y# X# J- q1 A

(点击上方名片关注我们,发现更多精彩内容) |

|