|

|

|

efw1zowrs0o640214313.gif

; f' N# e* K& x点击上方名片关注了解更多( m3 V N1 A" S, `

, w( V6 R) v1 p B# w

! i' ^1 h: R- z+ H5 r& ] _- A4 P+ d" x7 h6 `0 c- r

大家好,我是王工。

4 j& g; ]+ X4 s最近想要自己鼓捣点东西出来,设想的是先做好方案,画好原理图和PCB,然后在嘉立创打样回来焊接调试,在做方案的时候才意识到,可能会被DDR给难住。因为平时只需要设计方案和原理图,公司有layout工程师负责画板,我们不用自己操作,最多参加一下评审。这玩意儿看着简单,但真要自己去动手的时候,可能才知道没有想象中那么容易。

& d- @* y9 H; J. J# {& T: g3 [

kgpdhwqxpdr640214413.png

& } p& E9 Q N2 H4 r

& } p& E9 Q N2 H4 r

我想着,跟公司的layout同事交流一下经验,在这里顺便捋一捋DDR相关知识,跟大家一起分享一下DDR基础。为了提升文章的可读性,咱们还是分几个小点来写:DDR基础

. b8 q2 C8 _) ]8 t z gDDR发展历程

! |# b' o) |: }: `, vDDR的pcb设计

. U9 j" M9 G$ w' |, C T# Z5 h. a* a8 L

1、DDR基础DDR主要起个什么作用呢?它是作为 CPU 和存储设备(如硬盘)之间的高速数据缓冲区。核心功能是临时存储正在运行的程序和数据,以便 CPU 能够快速访问和处理这些信息。

; U, Y4 g1 J2 Y1 N5 d& P1 a: ~- v因为硬盘的读写速度较慢,无法直接与 CPU 高效通信。4 C7 H; a5 i0 O" @0 W6 o( N) K6 e

av5qrnd2jbj640214513.jpg

& Y' E% Y5 |; S

& Y' E% Y5 |; S

DDR是存储器的一种,关于存储器的一些基础知识,大家看看如下链接:

" [, c, _. d; m存储器基础DDR之频率DDR之内存时序电源DDR硬件设计技巧/ I* ^2 V* w# l, W5 K" S2 A

当然这都是很基础的知识,也只是关于DDR的冰山一角。

: R/ k9 [9 N+ W# p. y/ X

4 B" n' `* n. a+ ^ ?) g, |/ v9 z' ?* p; f5 E4 v

DDR的版本迭代经历过SDRAM、DDR1、DDR2、DDR3、DDR4和DDR5,预计DDR6将在2026年上市。

" ^( g- k0 [( I3 {/ i

2 o* H3 j* c8 J8 }' `

ckdhajb325k640214613.png

/ y. ~, c/ }; Y' M

/ y. ~, c/ }; Y' M

虽然今年已经是DDR5上市的第4年,但DDR4仍是目前市场的主流,打算以DDR4进行讲解。2、DDR4的发展历程以镁光型号为MT40A1G8WE-083:D为例

, [8 L) X: O, u0 ~2 H4 ?( l

' V; q a6 ~. m, ~2.1 DDR4的命名规则

, p# c7 S! }3 e l# n9 H

orlenu1ysww640214713.png

. S# ~ b& `! o: @, }! S8 [MT:代表制造商 Micron Technology。

q7 R* U4 E% C& }40A:表示产品系列或技术类型,指 DDR4 内存。

( _* O u4 @( I" {7 a6 L1G:表示内存容量为 1 Gigabit (Gb),即 128 Megabytes (MB)。/ X# W8 |/ [0 p) b

8:表示内存位宽为 8 bits。

) {$ K6 j$ g6 f6 K+ ~WE:表示特定的封装类型。% W8 y! R: a8 ^. ?8 N3 S: M/ t Y* {

083:表示速度等级为 833 MHz(等效于 DDR4-2666)。

9 v0 a+ Q7 |8 ^& t:D :可能代表特定的温度范围或工业级应用。

3 `$ [9 @( |1 @0 l2 Z[/ol]& Q$ Z# F O) H' W+ _* _% q: _

( U& m% v( O2 n- R2.2 DDR4的容量计算( b/ }( }# K5 W# g

我们以最后一组红色圈出为例来计算一遍:

2 e8 f( }# U4 U# j4 }

jwuwa5m5pv1640214814.png

: l% t' L2 H+ X6 H- gDRAM颗粒的容量 = 位宽 × 地址数量bank地址线位宽为16;bank group选组线为1,BG0;bank选择线为2,BA[1:0];行地址线为16,A[15:0];列地址线为10,A[9:0];) m9 x2 y% {1 `) F4 k5 ^2 T" a

容量=16 x 2^(1bank选组线+2bank选择线+16行地址线+10行地址线)

2 Q0 d& N0 C4 D* z, _/ H# t容量=16 x 2^(1+2+16+10)

, I I; l# _; I$ p' G容量=16 x 2^29

" u- J" U+ C# H8 R5 {1 r3 U& X; }- t容量=8,589,934,592b(单位换算b,Kb,Mb,Gb)( u' Q: {8 m5 f% g

容量=8Gb(除以3次1024,注意b代表bit,而不是byte)

, P* q. H/ b8 B+ n. H9 F容量=1024MB(8Gb/8)

' { m4 s* u) r0 M$ h( ?% q3 l

" ]# y+ A& I# j2 R& I

& Y1 D7 \* o' x8 |" S% {& `) d2 ?& C2.3 DDR4的速率下图表中的数据展示了不同速度等级下,内存模块的时序参数。例如,速度为2666 MT/s的内存模块在速度等级-075E下的时序参数为18-18-18,对应的访问时间、行地址到列地址延迟和行预充电时间均为13.50纳秒。2 m' @6 N) Z2 d+ @6 ~# y B7 O5 s

$ S; p3 O5 z* E$ {

evjtibwmoc4640214914.png

: @4 X: }1 L0 G S

okilfyjzgyb640215014.png

( j2 @' \3 p l0 z2 v

( j2 @' \3 p l0 z2 v

- k* a' v* v0 f+ g4 B: l

1.Speed Grade1:内存模块的速度等级。. {( A( }6 b m

2.Data Rate (MT/s):内存模块的数据传输速率,单位为百万次传输每秒(MT/s)。

1 g0 X3 J9 ~1 h3.Target CL-nRCD-nRP:目标时序参数,包括CAS延迟(CL)、行地址到列地址延迟(RCD)和行预充电时间(RP)。

+ B0 @+ ~5 q x" {/ d4.t AA (ns):访问时间,即从发出读取命令到数据可用的时间,单位为纳秒(ns)。2 S, W$ O; M% l0 }

5.t RCD (ns):行地址到列地址的延迟时间,单位为纳秒(ns)。' o& ~$ w- G2 N, c4 J

?6.t RP ?(ns):行预充电时间,单位为纳秒(ns)。6 M; s5 c/ h3 v, Z

, Y$ E! Q/ P U! B: U

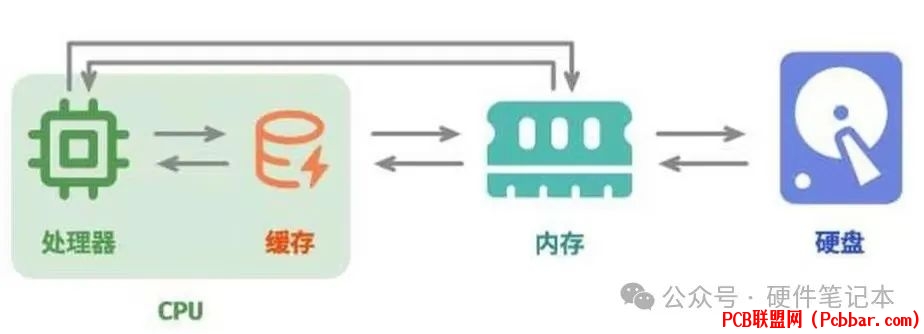

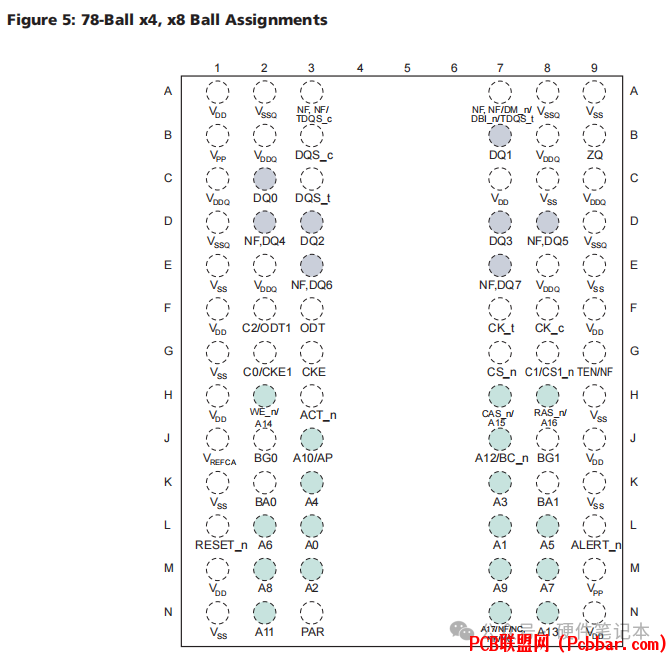

2.4 DDR4的封装: ?6 ~# G) a- }. B( ?

DDR4封装(有78球和96球,7种尺寸大小)封装(Packages):4/8bit芯片采用78球FBGA封装,16bit芯片采用96球FBGA封装。, I% J) O' P- Y- }% R7 U1 f

0oqijeqqxib640215114.png

: \* A/ |$ @5 v9 x3 O7 N+ G尺寸:13.2mm X9mm

F. Y5 C9 i4 H0 Z尺寸:12mm X8mm

* t9 o- t; A5 X( ]: T尺寸:11mmX7.5mm

5 \8 a ]8 Z$ K- B3 T8 E0 o0 }- X0 [* c9 ?

n1fg4tp0rhx640215214.png

1 c0 T/ A- O& g/ N8 Z3 r# y' |6 s尺寸:14mmX9mm. N4 h0 \! A6 t0 b9 L1 ]3 f

尺寸:14mmX8mm

/ n) V* s& T/ w1 Z+ n8 z) @7 w' U尺寸:13.5mm X7.5mm

' U: m2 ^+ D5 f( L& n0 L尺寸:13mmX 7.5mm

& X. Q9 C7 y4 X" U0 H# p/ S1 U' Y* X/ n2 j! [) l# M

当然,DDR还有很多其它细节,包括选型,一些重要的电源线,数据线,地址线,控制线和时钟信号等,大家感兴趣可以自己下来了解,下面再说说DDR4的PCB设计。% Y4 M4 w, I* f

3、DDR4的PCB设计DDR4布局

8 a" ^2 G: d, O$ z, X; a1、DDR在布局的时候一定要尽可能的靠近CPU,阻容元件放置在DDR背面,特别是滤波电容要尽量靠近管脚,走线要尽量短,电源线尽量粗,必须要配置比较大的储能电容。, s0 q1 q* W; L; @. V9 \6 K

" x0 Z, T0 D1 d8 b& k2、地址线布局布线需使用Fly-by的拓扑结构,通过串行连接每个内存芯片,从而减少信号反射,提高信号完整性。

& _8 R( x! e. k( G, v: }

skvqkm4fy2i640215314.png

/ E5 h0 q \* G: Y; ~; i, H/ U, z8 c7 H9 e# i

DDR4走线1、阻抗控制。PCB走线阻抗必须要严格控制,否则会出现数据通信异常,或导致电路性能下降,这个阻抗跟PCB线宽,线距,线层,板材还有其它相关因素有关。通常信号线中如果是差分线,阻抗应该是100Ω,如果是独立的线,单端为50Ω。这个需要专业的工具直接计算,以保证信号完整性?。

~7 K4 a* e: n% J1 C1 i3 y% N: f/ B

k22s20kuvge640215414.png

2 E9 x0 V0 c8 R" S2 x. U9 c4 Q. ]

2 E9 x0 V0 c8 R" S2 x. U9 c4 Q. ]

( a8 d5 i: v3 {5 d9 V

可选用嘉立创的阻抗计算神器,链接如下:

) z4 Z c4 n/ Fhttps://tools.jlc.com/jlcTools/index.html#/impedanceCalculatenew

: e! s4 ]$ x2 S5 ~ j& Z6 X' `1 W) P" U$ W

使用说明如下:https://www.jlc.com/portal/q7i37381.html

6 |, Y- ? x5 O U! x# x" q0 S0 @4 s* m8 P M

- A1 \( a; o0 `/ j& y" ^

2、DDR4的信号可以分为4组数据线和2组地址线,数据线最好同组同层(即:同一组的信号必须要走线在同一层),地址线一般很难做到同组同层,这一点也没有硬性要求。先把数据线走通,对于同一组信号内的走线,layout要做等长处理,最好控制在10~20mil以内(数据走线),对于地址信号走线要求就没那么高,一般50mil以内就可以了。9 [$ a8 U4 \2 \: }* v; x2 F

/ S- M; H) d8 _% `3、这里有个细节要注意一下,实际走线长度=芯片内部长度L1(数据手册会有标注)+ 芯片引脚之间的走线长度L2。( _- O, B3 A1 X5 p( x1 S3 p' M

ujcvhdt3ogr640215514.png

b3 ~# b I8 I% D. ~5 P' f' |$ R# ^9 x+ y4 T5 I

4、做等长的时候要注意一个3w原则,相邻的信号线,中心间距大于线宽的3倍,还需要对敏感的差分线做包地处理。5 f" l# Q: C& A4 X: t( L

j0gyh14ttca640215614.png

; } {$ }9 R7 S% n5 B! t2 {. H# I

; } {$ }9 R7 S% n5 B! t2 {. H# I

% j. Y1 x% x: O" T6 h7 q# l

以上描述看起来很简单,实际操作会更复杂,多熟悉几次应该就好了。

1 X4 q( e$ i5 V7 [5 Y e% N+ h% M) y- }/ X& ~. m

还有一些相关要求,可参考DDR4的走线设计要求在JEDEC标准中有详细的规范

+ _* Q2 t* S3 D6 Z4 Whttps://blog.csdn.net/weixin_43199439/article/details/142467998! T" S; c% L$ M. u2 T

& o; [) Q& F7 l$ X3 U( g: \好了,PCB设计的重点就讲这些了。

6 }" g& W. Y0 l0 Z1 T9 S; j. d7 o; [0 S i: J

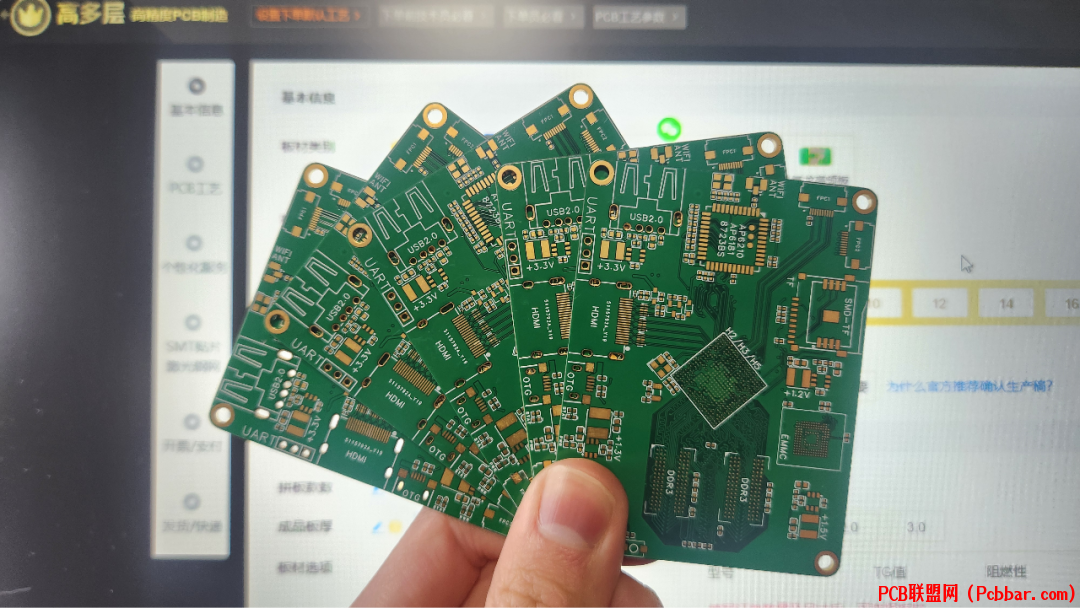

原理图和PCB都搞定了,那么下一步就要打样回来调试,板厂我首选嘉立创,主要是平时一直都是在他家打板,没出过啥问题,他们家的工艺文件规范,服务态度好,每次打板都会建一个小群,几个人服务一个人那种,真的有体会到上帝就是顾客的那种感觉,有问题可以及时沟通,效率很高。" Y8 {6 Y$ w0 Z7 {

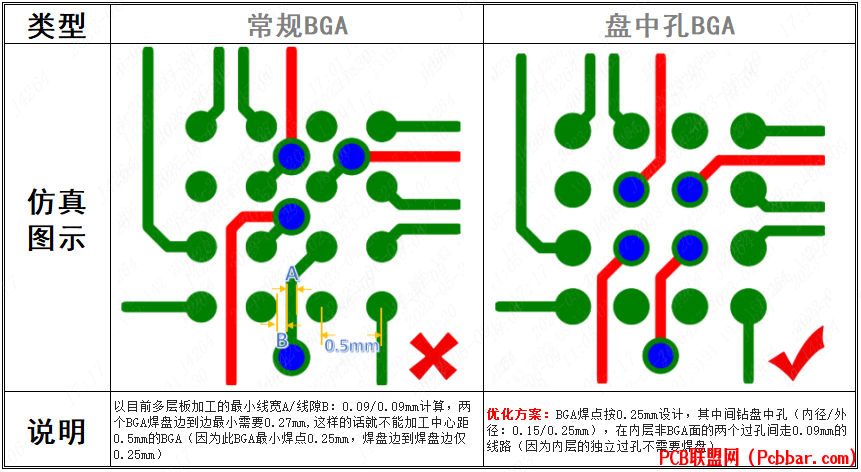

- B Q Z9 `1 ^3 z! ~: S6 C& ^再来看一下他们针对BGA封装的一些工艺指导,通过以下图片对比,明显可以看出嘉立创的盘中孔工艺相比传统工艺的优势(图片都有文字说明)。- O* n: E- } B }2 U3 ?( W

tgfa45xwfia640215715.png

' [% q8 y8 ?& _; y

' [% q8 y8 ?& _; y

- J, i% W. L) q1 z" `1 w

; }: e3 p! i" e. G- ~1 H0 i) J

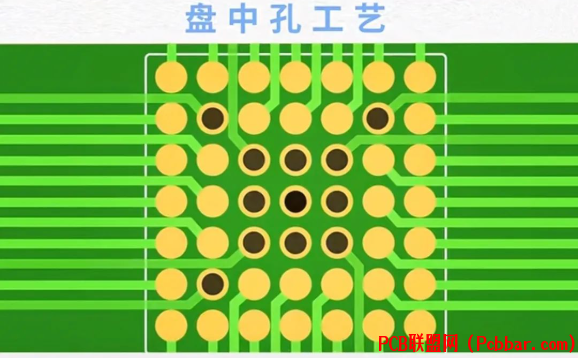

dr521ddmae1640215815.png

: j# V8 V3 P' i2 }9 l5 r. Q6 l& v. d. X

为了节约成本,我本想计划做四层板,但看到嘉立创对于六层板以上的PCB,可以免费升级盘中孔工艺,我迫切的想赶紧体验一下。可能还有不知道盘中孔工艺的同学,我这里再解释一下,简单说就是直接把过孔打在焊盘上,中间再用树脂塞上,然后表层和底层用电镀铜的方式把孔盖住,这样孔就看不见了,贴片时也不用再担心传统工艺的漏锡问题了。

3 n8 [9 k5 j, S0 }' W: G

ypckmrshbl5640215915.png

! j8 t/ G* [ O0 u9 T' Z

! j8 t/ G* [ O0 u9 T' Z

不用单独打过孔,也更方便我进行PCB走线,这又大大的降低了我的布线难度。1 v3 s# ~, [, X7 D* g

fnmttkaenal640216015.png

! d1 N' J' [6 C

! d1 N' J' [6 C

而且板子实物的表面看起来也更整洁,美观。大家可以看一下嘉立创官网的晒单,这个板子采用盘中孔工艺,过孔很少,整个板子看起来很清爽。

" F! O# E( g. E3 ?- y3 c

cjznfttgows640216116.png

; l; v3 d8 t* L2 ^! ^0 \; L! l好了,今天的分享就到这里,咱们下次再见。

, p' t# U3 \( D* ?2 e+ u

: b* X, e; ^1 }" n+ g

# B) j2 w& y+ M8 {( Z. A写在最后

- ~+ ~3 N! i- E* m都说硬件工程师越老越吃香,这句话也告诉我们硬件也是需要积累的,王工从事硬件多年,也会不定期分享技术好文,感兴趣的同学可以加微信,或后台回复“加群”,管理员拉你加入同行技术交流群。

* Z, o/ W+ c: X1 |) A9 w推荐阅读(点击图片直接进入)" V" y4 r9 l) t$ V6 l8 S. t9 C

htfofwqjfny640216216.png

2 l& w5 g9 O* v- W+ u! C

$ r; B z9 v" @5 V6 V. l) G, D, q0 H S7 a8 O9 z; J. ?# l

投稿/招聘/推广/宣传/技术咨询 请加微信:woniu26a3 u$ A& [4 n, |" g

6 G" Y% B! B: W& }" ~! g: j 6 G" Y% B! B: W& }" ~! g: j

" W" q& f+ S# _% h% {% R5 z声明:6 l2 ^9 p7 W6 J, h! U# b. |" u

声明:原创文章,转载请注明出处。本号对所有原创、转载文章的陈述与观点均保持中立,推送文章仅供读者学习和交流。文章、图片等版权归原作者享有,如有侵权,联系删除。推荐阅读▼4 @% \ n$ b6 t5 N. D5 b

电路设计-电路分析

5 H/ i3 h+ y d, L5 `. h8 a remc相关文章

( B; O/ a& p. B" I% ]2 h6 m( @电子元器件

* p4 d9 \+ U+ I$ r |

|