|

|

引言" h7 ~$ O" W J. s$ x1 \& H

半导体行业对Chiplet的兴趣正在不断增长,但要实现广泛的商业应用,还需要更多的标准、更先进的建模技术、方法论以及大量投资。Chiplet具有显著优势,包括更快的上市时间、不同工艺节点的一致性结果,以及与单片SoC相比更高的良率。目前,行业内对Chiplet开发存在两种主要方法[1]。

2 S# j7 y# V' @+ }8 c6 a+ ]8 x1 {2 Q

, s, p4 h. w7 u% G5 M- S13 l! _) Z) p% z$ k1 J0 p* A; a- J

设计方法与市场动态

( P. N( i- ^& p! f2 }0 O jChiplet领域目前存在两种竞争理念。大型垂直整合企业致力于严格控制接口规范,而初创公司、系统公司和政府机构则提倡基于标准化互联的自上而下方法。这种二分法为行业带来机遇和挑战。

4 q7 L) F4 Y; d( i8 `+ \( b/ o+ F% Y

传统的垂直整合模式允许公司对应用和半导体进行优化控制,避免互操作性问题。英特尔和AMD等公司已成功实施这种方法,主要专注于良率优化和大型芯片尺寸管理。 N; t" m4 G% U- ?% K

zqsjl4kkbya64063934625.png

3 p ^: h/ S8 T* a. X

3 p ^: h/ S8 T* a. X

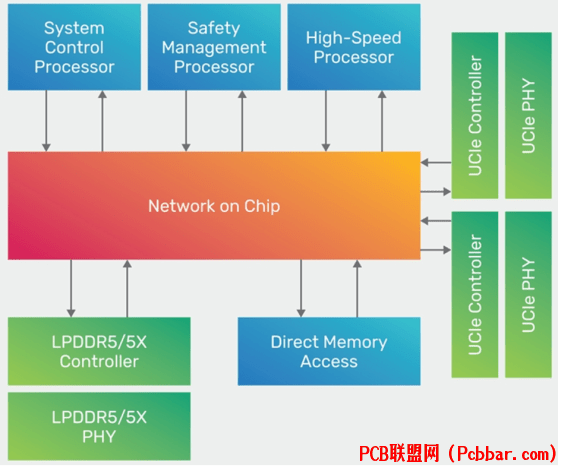

图1展示了Cadence的系统Chiplet架构,说明了系统控制处理器、安全管理处理器和高速处理器通过片上网络连接的集成方式。

! _/ i0 {* U6 w# J& o7 C

* @+ Z& |2 p/ z$ q" S. T& Y22 a8 N9 V, i( @! u4 C

建模需求与挑战

8 V- B# E6 q6 n9 V" ]3 U6 V6 TChiplet建模包含设计师必须考虑的几个关键方面:

+ h1 o# u0 R3 k$ e性能建模:包括对系统级分析必需的晶体管级建模。当处理多个Chiplet时,复杂性会增加,因为每个组件可能具有不同的性能特征。. \! n- D8 i: W/ ^8 J) F2 C. V

热分析:封装设计师需要详细的热模型来了解相邻Chiplet之间的热流动。% ?3 d7 {& t& [/ D- p( Q; A) o

在多Chiplet设计中,散热模式会影响整体系统性能。

0 H4 U9 R5 m6 M% q* I$ C功耗建模:与单片方案相比,Chiplet设计中的功耗模式和电压漂移考虑更为复杂。设计师需要准确的模型来预测不同Chiplet的功耗行为。

1 b5 ~# T7 H" |6 T+ f O" F5 t

! d" E" E; Q" a$ v; R8 F3( t. B+ r N* m$ W; W

标准化与互操作性

& Y# p5 ^* |3 W! K/ V! r; z行业正通过Chiplet数据可扩展标记语言(CDXML)交换格式等计划推进标准化。开放计算项目(OCP)和JEDEC的这项合作旨在创建一种描述性语言,解决互操作性挑战。3 j! j( K2 K/ p, Q# C ~

5 c" t' C9 N0 |2 Q. T标准化的主要进展包括:( h2 u3 J' e; d& _$ X

通用Chiplet互连Express(UCIe)标准,适用于先进和标准封装

# ^# j! D0 B0 B6 N) B) k, u+ j用于顶层连接的IP-XACT模型

; R. b. A' Q/ ?3 _! x; t架构模型的标准化接口

, A; g1 g3 I& h3 m工作负载分析的性能模型

- T8 P. N9 s# l% V/ P; S, w

: d9 l% i/ V# m* K& j# n( P4

' F( y8 B4 L& D2 z. j3 p7 n/ S未来方向与行业需求, o; T4 A F( ~

Chiplet技术的成功很大程度上取决于具体案例和标准化工作。行业专家建议可能需要"变革性"方法——由拥有重要知识产权的公司主动建立事实标准,而不是等待委员会驱动的标准化。/ O2 W+ U3 G, P! c2 e* Q" n; e( {4 C

3 q, P) i# _, q( ~2 c, B5

" Z5 o9 e" O& L$ X' s+ E) Y( q7 Z结论

9 A4 k, p1 C, {3 z) V# b. r" L4 `Chiplet方法代表半导体设计方法论的重大转变,但成功取决于解决几个关键挑战。行业需要在标准化与创新之间取得平衡,同时确保建模能力与设计需求同步发展。随着技术的成熟,预计将出现更多标准化方法和改进的建模技术,使基于Chiplet的设计更易于实现。

1 a3 E$ c/ e. ?" w9 g3 J8 @2 I5 O+ ?3 d: N, C( k" o

参考文献0 D4 g3 p8 c5 ]- m( F" T ~% H- d

[1] Mutschler, "Top-Down Vs. Bottom-Up Chiplet Design," Semiconductor Engineering, Nov. 26, 2024. [Online]. Available: https://semiengineering.com/top-down-vs-bottom-up-chiplet-design/ [Accessed: Dec. 1, 2024]

! }, v1 ^" ?* _, b* w+ KEND: L% G- Y) f E& ?: u j" ^

7 y+ c1 V5 u8 X$ T# n% @0 E( X6 R# n软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。

' l: \# U2 g: _0 i" ^点击左下角"阅读原文"马上申请

) g: z: Q+ K5 g1 w" d1 n4 V

) n- N# t$ r* _5 ~+ A; `: u1 ^欢迎转载

; T9 M$ f2 z$ H& Z! l9 r. J+ O8 G8 j; l& D- a1 P" P8 P( _ C- Z

转载请注明出处,请勿修改内容和删除作者信息!

8 W8 P) l e# j2 \! p' G1 K( Y. g) D& p, Z- D

4 r |8 m9 \* y

4 V6 W1 n+ f* }/ o$ \' h$ b/ D6 J

lsgglby400e64063934725.gif

9 ?! w! H% R: O" K

( { ?# K/ B6 }9 k# N' @* `) C/ n/ b关注我们- ~! U, A% _/ K9 _% b$ M

5 h6 X# S) I" r. s. [- J' [

# \ b* w; o) [& a0 D% \& T3 t

5rken5ex43q64063934825.png

m4 I9 J: W, `. Z | # z8 ^; K8 k7 t7 C, G$ a

fx0rvrtvn1b64063934925.png

6 v1 k6 R; b* ^ |

, ~; S' s) q* K" D8 y- g

go2g2u0vtjq64063935025.png

) ^$ f2 b @) R N

) ^$ f2 b @) R N

|

# u" m9 [" \+ w, ^4 G9 t; h$ t

4 L. [! _8 b; Y5 G* U0 \

8 @1 e- F) G, u" y2 d

1 A* n' @: N0 c2 `0 u( S' c关于我们:

* c! q. Z0 c1 L# K2 ]% m深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

9 Z4 m0 s8 g) L) X* u K, I5 y

3 |- H0 Y' {7 ihttp://www.latitudeda.com/

% u( ^' k" w& e" G1 C% U(点击上方名片关注我们,发现更多精彩内容) |

|