|

|

引言8 m2 I) e5 J o. v; ^

人工智能(AI)正在深刻改变半导体行业,特别是在芯片设计过程中。本文探讨AI如何重塑芯片设计的各个方面,包括分析、优化和设计辅助,帮助逍遥设计自动化的读者了解不同的AI技术及其在提高设计性能和生产力方面的应用[1]。3 c y3 A! o& E- ^# ~ g

( ?% p2 {; J6 @& Q1 u4 M* Z人工智能在芯片设计中的应用简介4 N' i( t% H g s: m! {

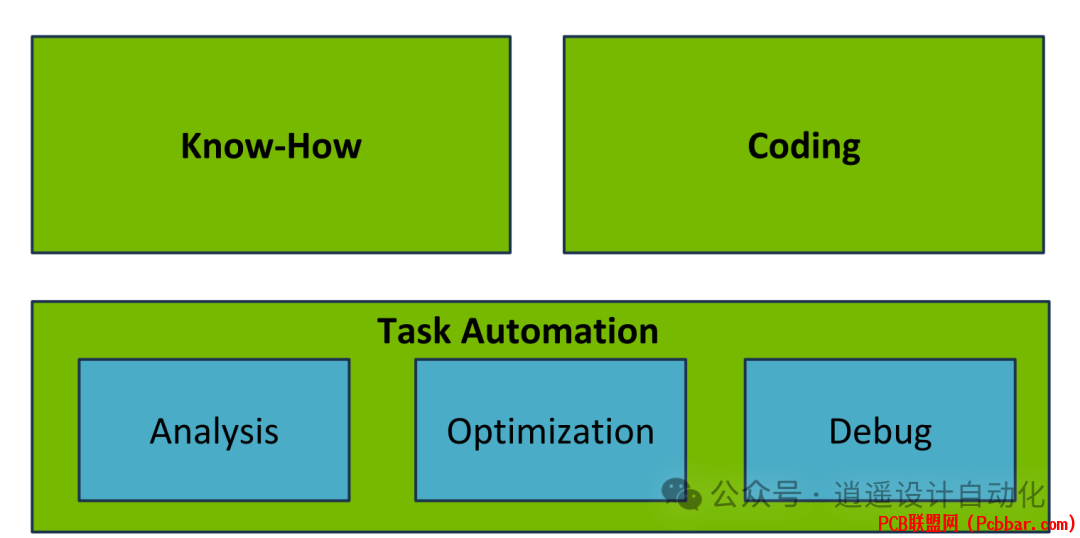

AI正在芯片设计行业掀起波澜,提升设计过程的多个阶段。AI主要影响以下关键领域:分析:AI实现更快速、预测性和跨阶段的芯片设计分析。优化:AI驱动的优化技术带来更快速、更可扩展和更优质的结果。辅助:AI为芯片设计师提供专业知识、编码支持和任务自动化。, G7 c- ^: i6 b( E" J4 V

[/ol]

1 M2 ]# R2 F/ s1 d( [" v( u7 M+ z8 R( L0 R

au5litfob4s64021058353.png

0 W5 e) \: B6 @0 \8 w* P' f' }9 q

0 W5 e) \: B6 @0 \8 w* P' f' }9 q

图1:此图展示了AI在芯片设计中影响的主要领域:分析、优化和辅助。

" S& T# _% {7 ~' Q( s8 ]9 W3 g. I" i2 O q' @2 L$ J0 O

芯片设计中的AI技术

) z8 O# P0 N3 w0 u+ W0 m4 d多种AI技术被应用于芯片设计,每种技术适用于设计过程的不同方面:经典机器学习(ML):适用于小型结构化数据,线性回归、支持向量机和决策树等技术用于初步分析。深度学习:卷积神经网络(CNN)适合物理设计数据,而图神经网络(GNN)适合线路网表数据。贝叶斯优化:此技术用于构建目标函数的概率模型,并选择最有希望的数据点进行采样。强化学习(RL):RL代理通过与环境交互并获得改进奖励来学习优化设计。生成式AI:这些模型,包括变分自编码器(VAE)和Transformer,用于生成最佳设计点和学习优化表示。大型语言模型(LLM):LLM用途广泛,可应用于问答、编码、提取、重写、分类、总结和推理等多种任务。. s6 M8 e! T* Z4 E2 }

[/ol]2 J+ Y7 K7 Y. f8 ?

- }. w9 }2 u/ c+ V# y& p

4juhcy3pb2h64021058453.png

0 z7 p4 O! D& b3 J

0 z7 p4 O! D& b3 J

图2:NVIDIA芯片设计中使用的不同AI技术,包括经典ML、深度学习和各种优化方法。% [, ~5 l* i8 h- r% V" ~* P3 G* b' Q

w1 i8 D, P9 X0 Z7 V0 y4 m

AI在芯片设计中的应用

7 w( K. O* H3 \1 ^7 t3 D让我们探讨AI在芯片设计中的一些具体应用:- C' |" K+ ^3 p) V1 T6 ?5 j

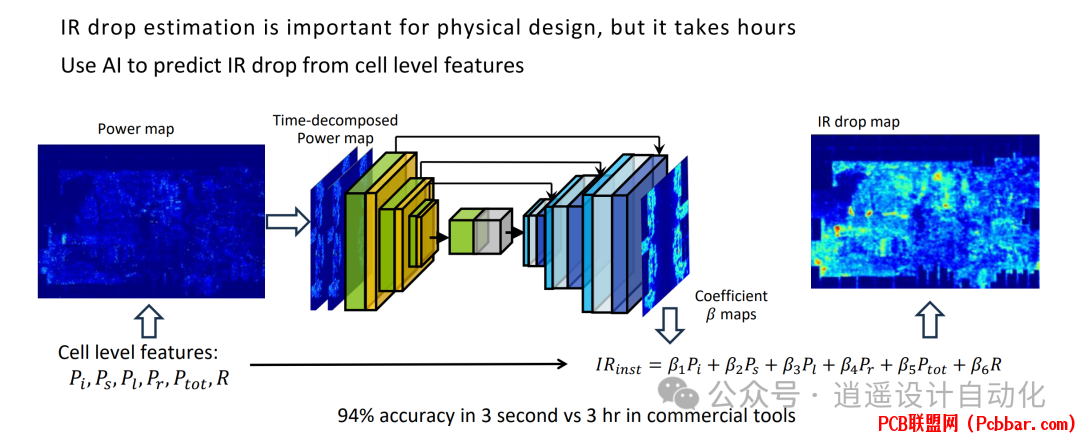

1. IR压降估算2 n7 p* D) u& r; |: ]

IR压降估算对物理设计非常重要,但传统方法需要数小时。基于AI的方法可以从单元级特征预测IR压降,在3秒内实现94%的准确率,而商业工具需要3小时。

4 x" e' X5 Q) E8 Z

& R+ f5 Q! M4 c# M0 U4 B! D' u

2tx1j4mo5te64021058553.png

; W7 V5 S% ~- r* l# y1 l8 |! C图3:使用AI进行IR压降估算的过程,显示了功率图和系数图。

4 c& f' C3 e# r6 E& A

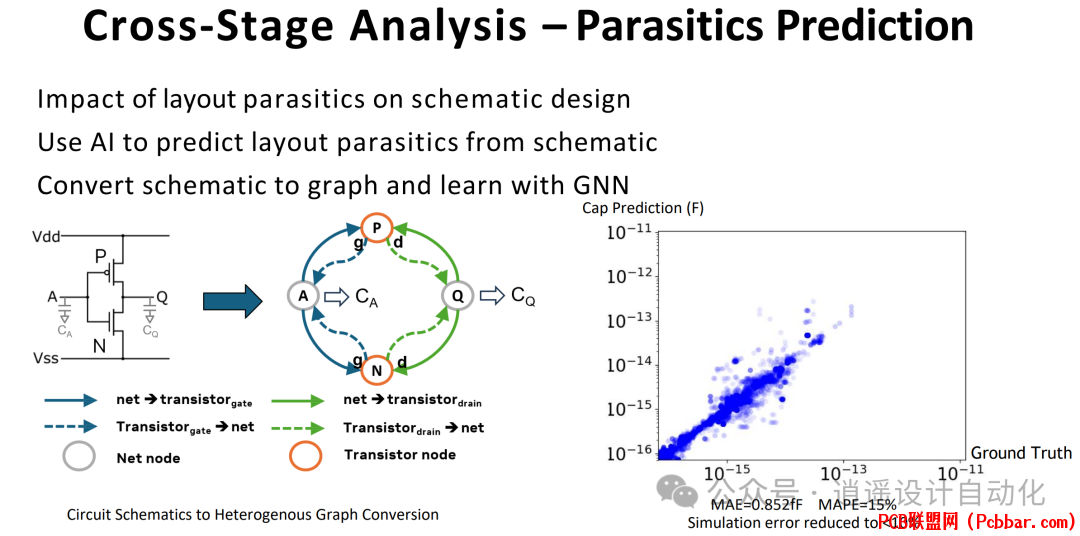

3 s+ l3 B: R& D2. 寄生参数预测

5 l* p9 ^: [1 N4 S y3 UAI用于从原理图预测布局寄生参数。通过将原理图转换为图形并使用图神经网络(GNN),设计师可以高精度估算寄生参数,将仿真误差降低到10%以下。3 L2 n7 s: |. Z$ T, d

4 Q+ I* D0 ~* z. f" i1 V

c1gtrm41qir64021058653.png

5 m5 Y, j+ T8 K" x- d5 C

5 m5 Y, j+ T8 K" x- d5 C

图4:此图说明了将线路原理图转换为异构图以进行寄生参数预测的过程。1 M _* {2 t! `6 o7 k/ l. B

2 n- V+ G7 s; S& c- u6 c- ]$ e

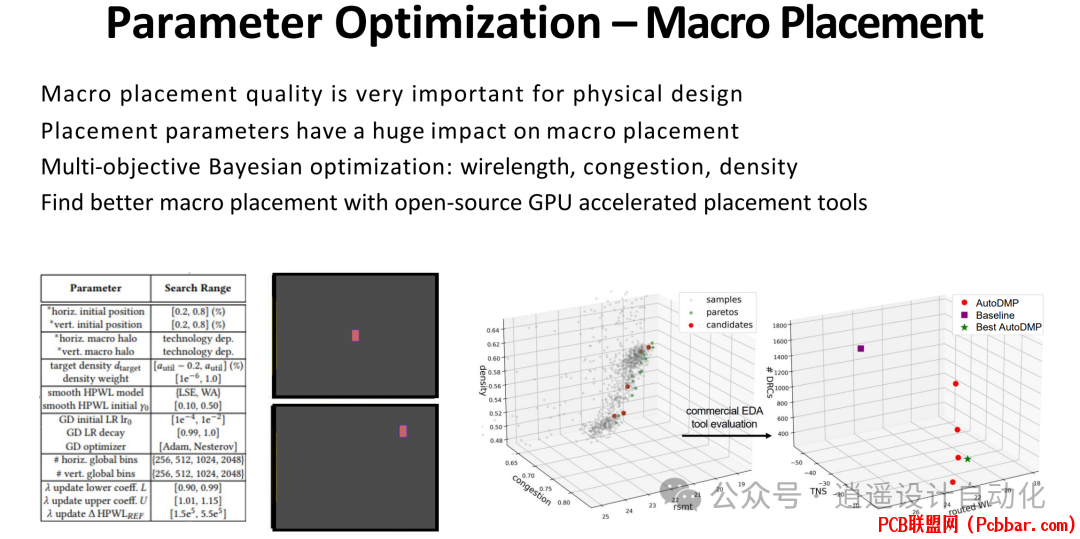

3. 宏单元布局优化6 Q# b; l: Y' P, O% E9 e$ e3 }

宏单元布局对物理设计非常关键。多目标贝叶斯优化被用于改进宏单元布局,考虑线长、拥塞度和密度等因素。/ G" l4 R2 h# f

M, g, n; I" K f ]4 r

4z2dmgfkdjb64021058754.png

. ] {5 W$ |% }

. ] {5 W$ |% }

图4:此图比较了基准宏单元布局与使用AutoDMP(自动化DREAMPlace基础宏单元布局)优化后的布局。

# |6 U, V% E5 P6 h" v& K

* F, W# V% F- X8 g: ]; I4. 设计规则检查(DRC)修复

; A4 i/ h* `( c* K5 |3 X. e/ q强化学习代理被训练用于自动修复单元布局中的设计规则检查(DRC)违规。代理学习逐步减少DRC错误,最终得到干净的布局。

. |( t, y& i6 x& H6 h5 n4 b* m. F

- }: a7 {9 V: g* Y5 @9 a

fz4c3haxceb64021058854.png

4 J1 @# Y a2 J+ F/ X v1 N9 v8 F图5:此图显示了RL代理在单元布局中修复DRC违规的逐步过程。% }+ t; _9 M/ K1 l

2 S9 n! N: e( E x0 ~* N

5. 数据通路优化9 Q' Q' G; |3 q1 @3 u# V

强化学习也被应用于优化数据通路结构,如前缀加法器。RL代理探索不同的前缀图结构,以实现比知名加法器架构更好的性能。

% o7 m3 _; P# f9 l |

% X2 O: P* A t" x: P/ N% r2 A, `

ujytwryxx0d64021058954.png

8 ^' l0 T2 W& U& v

8 ^' l0 T2 W& U& v

图6:此图说明了使用强化学习优化前缀加法器结构的过程。' @0 J5 y" @3 W$ A

9 z+ k# L% {: K$ m6. 门尺寸调整$ R8 N/ U( J8 v: }6 Q: A0 g+ b7 j

Transformer被用于生成最佳门尺寸,以进行时序和功耗优化。通过将门路径建模为序列,AI可以生成优化的门尺寸,与传统优化方法相比,实现了100倍到1000倍的加速。

1 h7 m9 v. h: _( ]* R: P

6 B T% G" q) Q6 r0 d

0qijvawhgw164021059054.png

! R+ A2 A6 X% F8 G" }3 d

! R+ A2 A6 X% F8 G" }3 d

图7:此图显示了Transizer方法在门尺寸优化中实现的功耗/延迟权衡。9 r: L- T. ]$ q2 }$ x2 ]& k

# @9 Z. S% f6 c; V+ P7. 加速器设计7 @4 F) D+ X5 y+ `( ]- v

变分自编码器(VAE)被用于学习硬件加速器设计的连续可重构潜在空间。这种方法在探索设计空间时实现了6.8倍的样本效率和5%的性能提升。

) _4 W/ K% K" E3 U8 m$ ^! p7 ~5 `$ u. A' j/ i6 T5 S* X$ b0 S Y

rkdtnch42ip64021059154.png

+ j6 u. L" n ?, l图8:此图展示了在神经网络加速器设计空间优化中使用VAE的过程。! ~% c8 i9 J& |0 u# r7 q7 H, |

; m6 a9 D7 |) S大型语言模型在芯片设计中的应用

1 t3 v! I; E! Z8 O: |0 x大型语言模型(LLM)在芯片设计中越来越重要。可以通过以下技术适应各种任务:' o; o) h% W s g; \

参数训练检索增强生成(RAG)上下文学习基于代理的方法

( S# X( u6 {1 K% r7 B5 o5 p# b) F' V1 s& z

LLM在芯片设计中用于多个目的:编码辅助:为特定任务生成EDA脚本。专业知识辅助:回答关于设计、基础设施、工具和流程的问题。分析辅助:总结错误报告并预测任务分配。! R' L; R& R0 Y' y2 e, F' U9 b9 c

[/ol]4 M( }, |/ F: Z: t( G4 r# R: l. I

4 T# B7 N% D0 g' y0 S/ }

im2bfim05ml64021059254.png

& E2 h- C, p% y3 d7 b

& E2 h- C, p% y3 d7 b

图9:此图显示了LLM在芯片设计中的各种应用,包括编码、专业知识、分析、优化和调试辅助。4 q3 K* u. q# _% u0 n

/ ^; D% x! w E* w/ X

结论+ G# u- g6 m1 i. Y# g

AI正在通过提高分析速度、优化质量和设计辅助来革新芯片设计。随着该领域的进展,可以期待看到:持续使用贝叶斯优化和强化学习,以实现芯片设计中更好的PPA(功耗、性能、面积)。在优化数据上训练的生成式AI模型,加速传统优化过程。LLM模型和代理通过聊天机器人、协作工具和任务自动化显著提高芯片设计生产力。可靠高效的推理基础设施的重要性日益增加。% M( h8 X; ]6 B

[/ol]

& j( y! z" R4 O. W' v) E3 b% e* ^4 c2 G为进一步推动该领域发展,需要更多数据集和基准,如VerilogEval、FVEval和LLM4HWDesign。随着AI的不断发展,其在芯片设计过程中的集成无疑将带来更高效、更强大和更创新的半导体产品。

' |' o1 u9 J, F' S

# ]4 ~- ]# j& w9 H# D$ B( t: w

8 O$ \* |/ J) H5 l( L参考文献

0 I: J; ^* @3 @% T[1] H. Ren, "Introduction to AI for Chip Design," presented at Hot Chips, Aug. 25, 2024.

& {+ e6 i" `2 q/ q8 A% ~: v8 ?' c* m' h6 |# k7 x

- END -8 d0 r% t$ i) F- ^6 r& ^0 ~

9 ]" }9 }/ Z6 m6 U( I% A软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。1 Q0 }3 c' ]" f8 v$ g3 Z

点击左下角"阅读原文"马上申请

- n$ K' x9 ?3 a* R, c2 P5 a$ L5 n( E* x- y, `1 z

欢迎转载3 s$ O* z; s9 f$ C* A7 w+ _

" k" z b; [! G8 b转载请注明出处,请勿修改内容和删除作者信息!

2 Y5 S; _+ P- m7 [5 @ B8 c. i# Q# O1 r0 ~& \1 r& V r

. F" X9 b1 d" _$ O, V4 k. x- s1 W" R9 B) b* J5 ]

rjgkz3rptol64021059354.gif

, [& e; ^; M. P7 d

, [& e; ^; M. P7 d

" S* t' r7 S$ W- x关注我们$ Z& W9 J! b6 g$ A' V _( y

1 q6 ?& N# {$ u9 R s

2 E0 z* W: W$ ?- A8 c2 w9 | h% n6 v$ `

noaau33gdof64021059454.png

5 G) i3 l/ w6 j! ~$ ]4 j# v4 C

5 G) i3 l/ w6 j! ~$ ]4 j# v4 C

| 7 U3 }0 t) p, T

c4byehph22s64021059554.png

5 h/ |8 f& ~* n, a3 J" E- {. B

5 h/ |8 f& ~* n, a3 J" E- {. B

|

$ W. m) b; U* f2 b3 r/ l/ f, M

4ogv4t25yhy64021059654.png

4 |+ @ t# K3 e! ?1 w$ H, e X

4 |+ @ t# K3 e! ?1 w$ H, e X

|

. Y, x2 r" K+ Y) p

$ ^% m! V9 g3 c' R

* }6 y @) t$ N& p

& L6 L/ o4 l% f$ m

6 M) C4 z% r0 n

/ I7 X$ H/ x; Q: C9 T9 X

3 ^9 x' P3 C; V" Z2 w( V关于我们:

- Q' P# k: M# }8 l4 J深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。& o0 H/ }, w9 B1 L+ \6 Q

! j0 c$ T+ w1 ^- x$ l& y) T

http://www.latitudeda.com/3 r& k" z* c6 p0 n: V

(点击上方名片关注我们,发现更多精彩内容) |

|