|

|

以太网口是我们日常工程中常用的通信接口,以太网接口有很多种,本文将对常用以太网接口进行科普介绍。* ]0 M6 [* ?5 O0 {. S; r" p

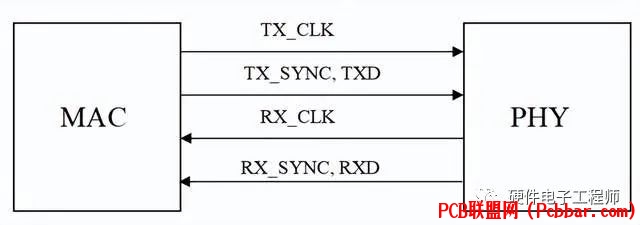

1、GMII接口1.1 GMII接口概述GMII接口属于源同步时钟类型(时钟与数据都是由同一芯片驱动),时钟速率125MHz,接口连接关系如图1所示,22根线,其中TX_EN, TX_ER, TXD这些信号同步于TX_CLK;RX_DV, RX_ER,* z1 Z3 q X' f5 P/ h6 H- S

qmsrxdmvnnc64010454919.jpg

& H: E# c% G% a

& H: E# c% G% a

图1 GMII接口原理框图

0 W- J) u* q3 `; m# yRXD这些信号同步于RX_CLK。其它的两个信号CRS, COL只用于半双工模式,一般设计中不会用到,而且这两个信号与时钟是异步的,对这两个信号不做要求。各信号说明见表1。& ]) B4 x% N9 w, q ?- V+ A9 @

表1 UTOPIA LEVEL 2接口信号说明. L( @- T: y/ m

信号名称

; T- H. H1 w- |7 h/ H! H | 信号说明

9 Y. C* X4 K% U- q4 x | TX_CLK

% A" y7 j& W$ A: g) e5 _ | 发送方向时钟信号

2 p, `3 m' w. W2 l4 b* ~7 [ | TX_EN4 t6 d# p; I8 x* F) x

| 发送方向使能信号

) u, Y$ ~. k" ` | TX_ER

, ~8 Q% W1 e8 r5 D7 U( S | 发送方向错误指示信号

0 u% N8 I& `' ] | TXD

' C: y, i0 V4 N0 Q' t9 H | 发送方向数据信号

) e( j) Q( C! m5 U3 N; D( z | RX_CLK

! c+ r( f5 f; J4 a9 [! q( e6 ~ | 接收方向时钟信号0 ^3 s' W$ ~) i6 X8 J, p. p7 n

| RX_DV

" ~7 G2 k% {4 @9 E1 n i% J) ` | 接收方向使能信号& v; b1 v" _; y# \* ~3 j, L9 P

| RX_ER2 c6 C ~! t* q) U* V" @, _4 O2 P

| 接收方向错误指示信号

* m2 r2 X8 A! O& t | RXD

% j' }0 l3 H4 l% _ | 接收方向数据信号+ f6 j: j; p# H* m

| COL: O/ }" ?7 r. F. I0 _

| 碰撞指示信号

; @6 r$ A" o. f | CRS' W1 P( Y' F8 } O. V. s( P; @

| 载荷检测信号' D* g+ C1 [, Z

|

1.2 设计原则1、要求同方向的时钟数据严格等长,即TX_EN, TX_ER, TXD这些控制/数据信号与TX_CLK等长;RX_DV, RX_ER, RXD这些控制/数据信号与RX_CLK等长。一般设计中,要求控制/数据信号与时钟信号的长度差不大于1cm(约0.1ns)。

7 M* n' k% z0 ]; d8 N2、要求信号的发送端(包括时钟/数据/控制信号)串接33欧姆电阻以减小反射,提高信号完整性。

2 A* A# A" x4 C7 [3、信号走线中要注意保持阻抗的连续性,尽量减少过孔数量(一般过孔数量在3个以内)

4 G% f; r* x7 `8 Y6 R/ i4 b4、因信号线较多,在布局允许情况下,PHY与MAC尽量靠近,减小高速信号受的串扰。- N) x, n9 u: Y: ]

2、RGMII接口概述2.1 RGMII接口概述RGMII属于源同步时钟类型,最初是由HP制定的一个GMII精简版专利标准,得到各大主流厂家的认可,成为一个普遍应用的关于xMII系列接口的标准。RGMII经历了1.0\1.1\1.2\1.2a\1.3\2.0几个版本。从2.0版本开始支持HSTL,之前的版本支持2.5V CMOS。* X" s# u; C* l8 y

TXC/RXC时钟频率支持125MHz,25MHz,2.5MHz,可以适配1000M,100M,10M速率。在时钟的上升沿和下降沿均进行数据采样,相比GMII接口,数据信号线收发方向各减半变为4根,信号线总共有12根。如图2和表2说明。1 @0 F( L M# C

to5rm2zcp1s64010455019.jpg

9 j3 w. U5 C" [: x0 a9 R图2 RGMII接口原理框图

4 G; l+ z, a P# S5 U, B表2 RGMII接口信号说明' O/ E$ H p' i! I

信号8 `4 t' D; ^; h$ L7 _8 g. @& M3 @2 r

| 方向- r2 {$ T' T8 }3 ]3 Q7 N* O7 L' G

| 说明/ O8 n) Z# p0 ~) w, l# r

| TXC

+ b1 P% L7 o; R4 }% D | MAC-->PHY

, f* ^+ N' f, m/ [" Z | 发送时钟信号

7 }6 l9 _. a5 o6 [; {3 @ | TX[3:0]

2 [* {# R1 I5 |: ` | MAC-->PHY

4 \& b, h# u( g& B | 发送数据信号8 T; M: j$ z. P# @) x* K, G( P2 S

| TX_CTL

4 j5 [1 n/ W9 ]9 W" O8 h0 Z) P | MAC-->PHY

/ p" O! C2 t, m8 N$ X3 Y* c7 `' V( @ | 发送控制信号9 S. X7 f* I. Y u# W* N( {! }

| RXC- n2 W Y# W' {/ d* u# H& T% u

| MAC4 [! _1 n0 @$ R( B8 t

| 接收时钟信号

6 H8 Q2 m+ n' ?% k/ U; Z, j+ y- \ | RX[3:0]! I; Y6 m$ m# m1 C. K

| MAC3 a( v' L+ W0 ?$ c" I

| 接收数据信号

+ ^8 S( S z( W2 y/ O7 b | RX_CTL

8 y- I+ H, `; N! o. | | MAC

4 y0 i3 T5 w' L5 M9 r; M | 接收控制信号

3 u% ?% X" C7 n$ e0 j1 r' m |

2.2 设计原则1、要求同方向的时钟数据严格等长,即TX_CTL,TXD这些控制/数据信号与TXC等长;RX_CTL,RXD这些控制/数据信号与RXC等长。一般设计中,要求控制/数据信号与时钟信号的长度差不大于0.5cm(约0.05ns)。

, u2 ^5 x1 r( B$ g0 x/ i g+ |2、要求信号的发送端(包括时钟/数据/控制信号)串接33欧姆电阻以减小反射,提高信号完整性。1 m) h: Q4 p: M+ U

3、信号走线中要注意保持阻抗的连续性,尽量减少过孔数量(一般过孔数量在3个以内)。

- m. d ]/ }% z" o: h4、因信号线较多,在布局允许情况下,PHY与MAC尽量靠近,减小高速信号受的串扰,线长最好小于4000mil。! }2 y/ Z6 s' z

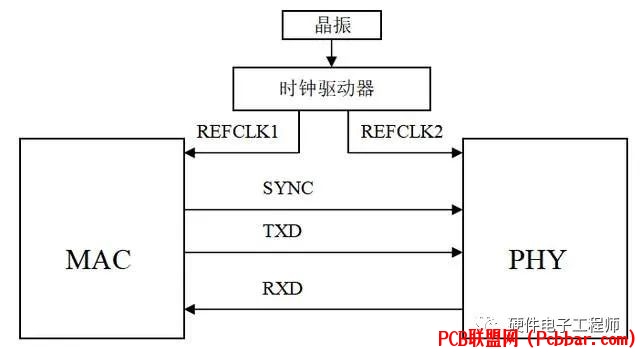

3、SS_SMII接口3.1 SS_SMII 接口概述SS_SMII(又叫S3MII)接口属于源同步时钟类型,接口原理框图如图3所示,时钟速率125M Hz;信号与时钟间的关系等同于GMII。

9 d9 t# B$ n& K# Y ^

wrrmkpfd1ny64010455119.jpg

* Y2 R$ L. g: G t$ |

* Y2 R$ L. g: G t$ |

图3 S3MII接口原理框图

, G) c, }. l1 T3.2 SS_SMII接口设计原则1、要求TX_SYNC, TXD信号与TX_CLK等长;RX_SYNC, RXD信号与RX_CLK等长。一般设计中,要求控制/数据信号与时钟信号的长度差不大于1cm(约0.1ns)。

* j" |" B+ |( ?7 B1 k2、要求信号的发送端(包括时钟/数据/控制信号)串接33欧姆电阻以减小反射,提高信号完整性。

0 i! n0 P4 n& T# L. j9 w2 H3、信号走线中要注意保持阻抗的连续性,尽量减少过孔数量(一般过孔数量在3个以内)。

; D' ~* h1 `! R4 n4、在时间允许的情况下,尽量对接口进行仿真。# m% \% q R- |& e- |& h

4、SMII接口4.1 SMII接口概述SMII接口公共时钟模型(两端芯片的时钟来自共同的时钟BUFFER),时钟速率125M Hz,接口原理框图如图4所示;并不要求数据线与时钟等长。4 \* e+ D8 @4 T

4.2 SMII接口设计原则设计时可以先考虑使REFCLK1, REFCLK2等长。

9 C, N9 l7 ?0 k5 J+ x7 r: N[/ol]* b% ?. N1 Q9 W

02dkbz2nxcl64010455219.jpg

0 H" y% i* ]6 u/ A, R

0 H" y% i* ]6 u/ A, R

图4 SMII接口原理框图$ a. X5 ?* Y" K# P4 s8 `

2、要求SYNC,TXD,RXD这几个信号走线尽量短;(从芯片资料理论上看出这些线

2 f2 s* o7 h h的最大长度为1.5ns,21cm;但由于芯片差异性较大,因此实际布线中尽量走短)。$ h3 s$ s" W$ b/ M% E2 l0 _

要求信号的发送端(包括时钟/数据/控制信号)串接33欧姆电阻以减小反射,提高信号完整性;5 t3 b; e+ h! P( M1 q3 u7 ?. w

信号走线中要注意保持阻抗的连续性,尽量减少过孔数量(一般过孔数量在3个以内)。

, P9 s0 G+ i" O2 |) f1 O& w[/ol]5、RMII接口5.1 RMII接口概述RMII接口属于公共时钟传输模型,时钟速率50M Hz;并不要求数据线与时钟等长。图5所示为RMII接口的原理框图。

3 `1 r8 l+ ?8 D2 w

eg1m31rvbmq64010455319.jpg

# ~1 X/ ^. O' f图5 RMII接口原理框图5 G4 D; _* {- z

5.2 RMII接口设计原则设计时可以先考虑使REFCLK1, REFCLK2等长。

9 d6 F* L A. Q K; y i要求其它的数据/控制信号走线尽量短;(RMII规范规定信号的驱动能力在包含负载输入电容情况下不小于12inch,也就是30cm;但由于芯片差异,实际布线情况下尽量短)。

1 s \. d$ a/ j* F+ Z8 G& I要求信号的发送端(包括时钟/数据/控制信号)串接33欧姆电阻以减小反射,提高信号完整性。1 M/ I+ w( c; S. }

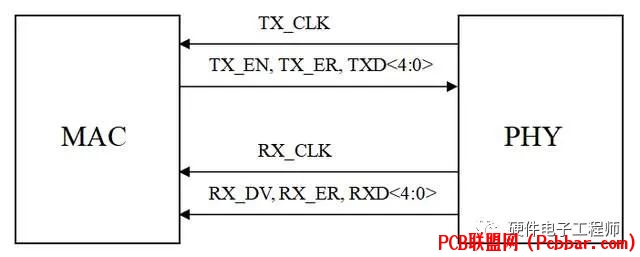

[/ol]6、MII接口MII接口属于公共时钟传输模型,时钟频率25M(100M以太网)或2.5M(10M以太网)。两个时钟都是由Phy发送给MAC的。接口框图如图6所示。另外,该接口的其它两个信号CRS、COL是异步信号,无特殊要求,故不在此图中画出。

5 _( V- _7 ?' t) J对于MII信号,由于信号速率较低,因此在布线上无特殊要求,只要求Phy与MAC离的不要太远就可以了。 e; y3 _. F8 v- @8 y4 M# {8 _% S; \

ztseg0uap1x64010455419.jpg

& e7 I( f1 U; u9 _1 Y3 D

& e7 I( f1 U; u9 _1 Y3 D

图6 MII接口原理框图 |

|