先进基板技术概述2 s9 s) A& ~% w

) U/ S0 h/ F5 S9 C3 ]/ _" u3 \先进基板是现代半导体封装的核心,支撑着Chiplet、光电子技术与存储器的集成,以构建紧凑且高性能的系统。随着摩尔定律放缓,行业焦点从晶体管微缩转向基板材料与制造工艺的创新。本文深入探讨有机、硅基与玻璃基板等关键技术,解析其如何应对互连密度、热管理与信号完整性的挑战。1 L0 L4 E- C1 p8 s- A# S

新型基板材料及其特性* t) g9 u9 k. j; p, _7 m t b5 d

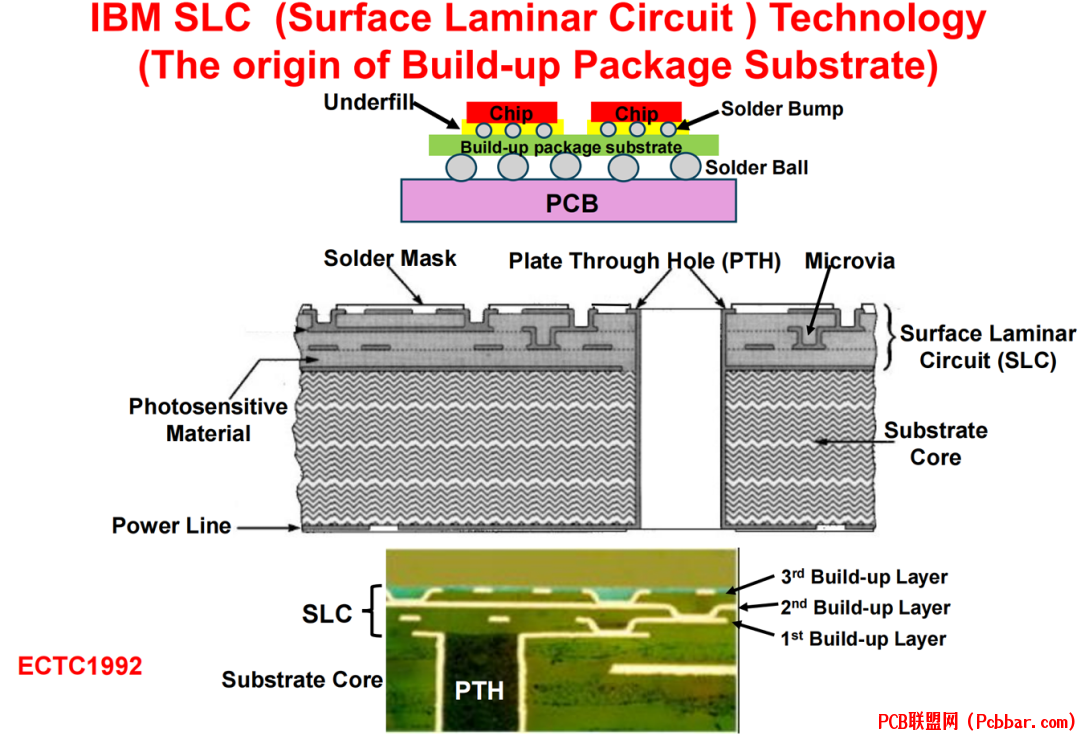

; T# w( ~1 N: k5 p9 M有机积层基板,有机基板(如味之素积层膜ABF)因成本低、柔韧性高,主导消费电子市场。此类基板通过在核心材料(如FR-4)上交替堆叠介电层与铜层,并以微孔互联实现高密度布线。IBM的表面层压电路(SLC)技术率先实现10/10 μm的线宽/线距。& l1 g7 e; ?% V% K4 S

gqznbazudmf64057677010.png

: J8 Z4 q$ v, m/ [* j

: J8 Z4 q$ v, m/ [* j

图1: IBM的SLC积层基板,剖面图展示有机核心上的微孔、焊球与积层结构。5 A& b* f1 s! i& K

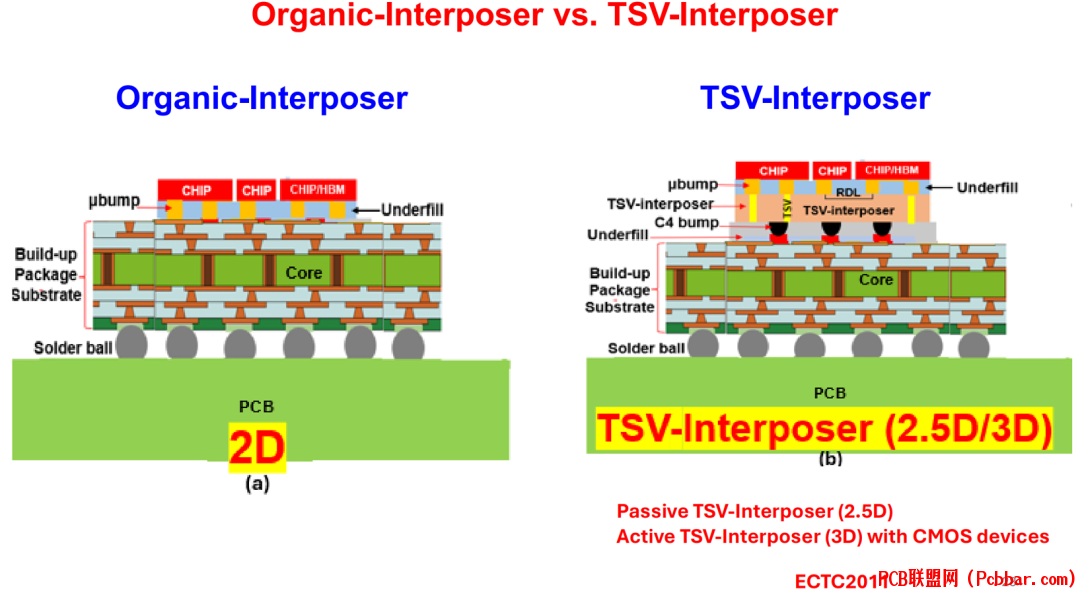

5 {4 w; e. P) j- M% x硅中介层,含硅通孔(TSV)的硅中介层为2.5D集成提供高密度垂直互连。台积电的CoWoS技术采用被动硅中介层与四层再分布层(RDL),以40 μm间距连接逻辑芯片与HBM,实现超万点微凸点互连。

6 j* R) M6 g% i. ?

sxzigs5bzxx64057677110.png

7 t7 I% X6 b$ f# R图2: TSV中介层架构,(a) 含微凸点的TSV中介层;(b) 含嵌入式硅桥的有机中介层,适用于成本敏感场景。1 a4 Q- o9 V% d7 J/ X) V3 w1 g7 G

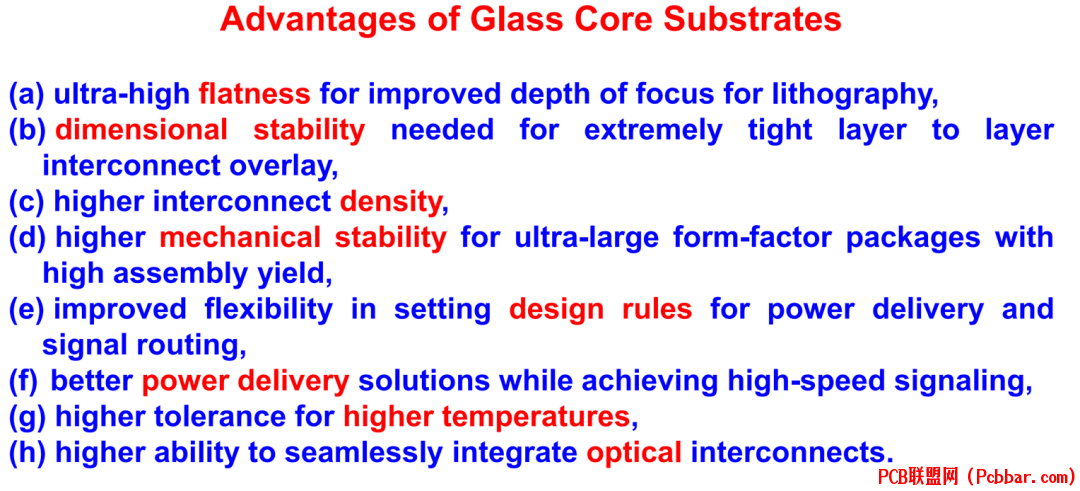

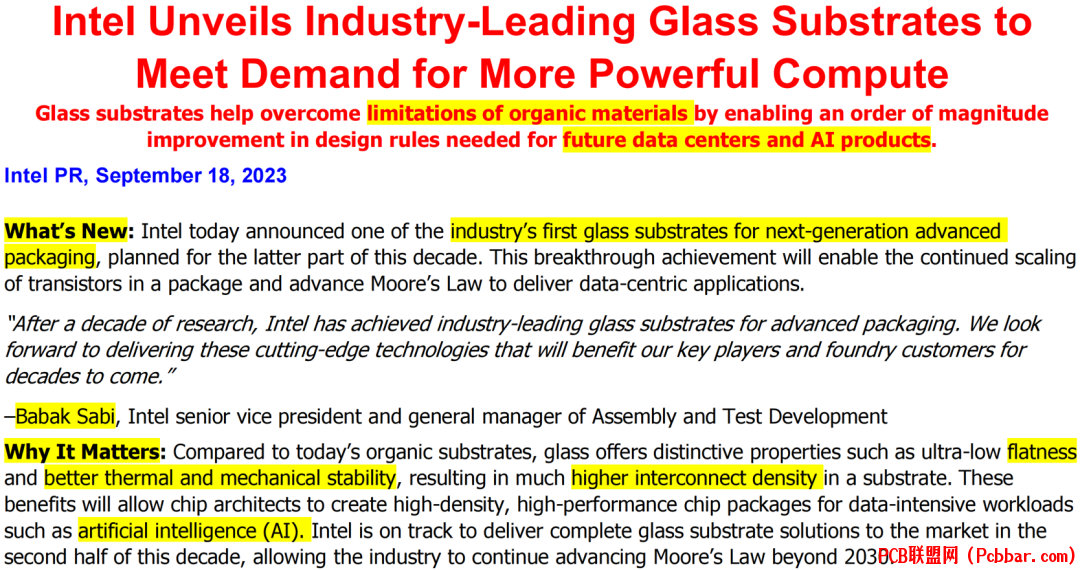

3 G0 u4 {6 _( g& T; r玻璃核心基板,英特尔的玻璃核心基板具有超低翘曲(2500 mm2)。玻璃的互连密度为有机基板的10倍,且兼容光波导集成。

( q* ?$ e. C3 T! K& v+ l! k; ~# q

nqzgdqlryxm64057677210.png

2 \( i7 Y( M3 r$ a6 T$ _图3: 英特尔玻璃基板优势,核心特性包括尺寸稳定性、机械强度与光互连兼容性。0 s& ?' f, F: S( |/ Z: w

关键制造工艺与技术7 e2 l2 s/ O. H

( _& \% Q. p; D$ b3 {

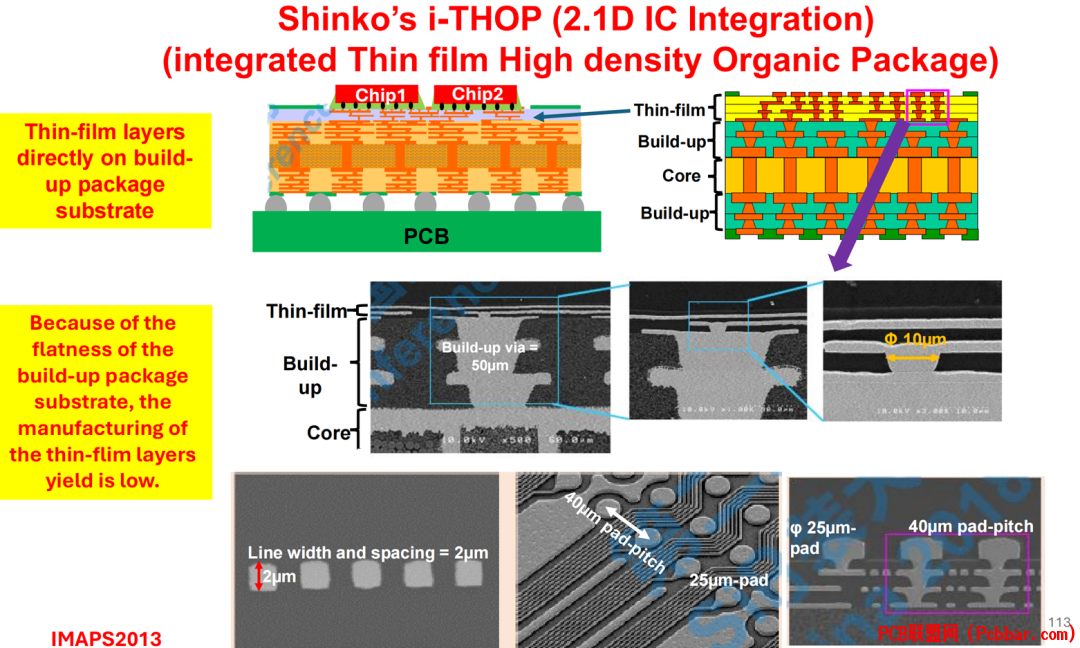

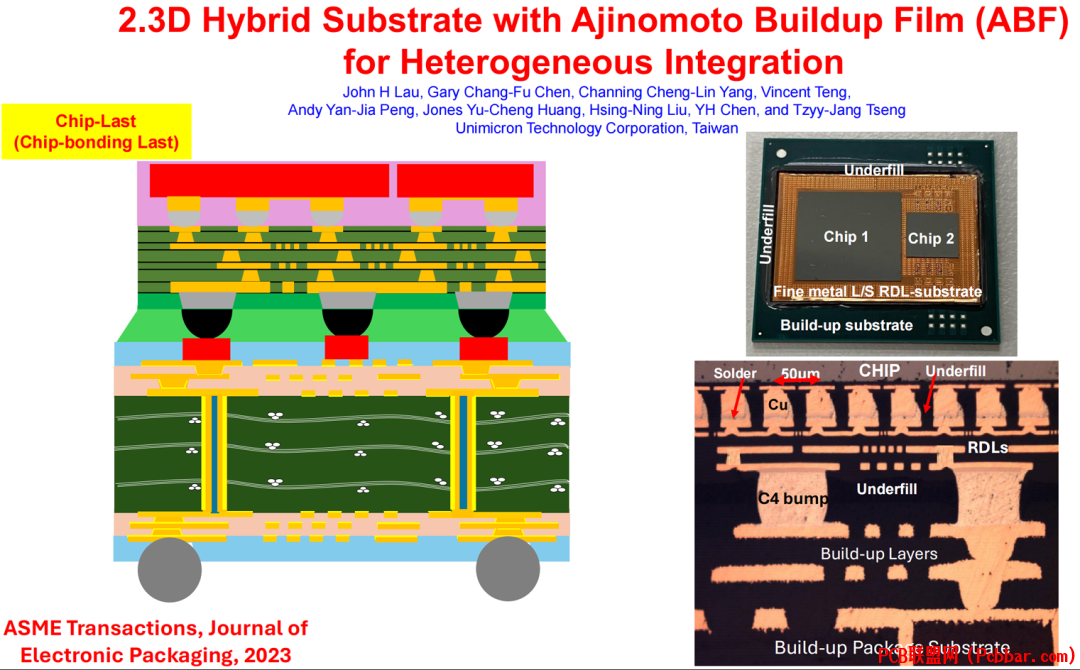

积层工艺,积层基板通过逐层压合介电与铜层制造,关键步骤包括激光钻孔、电镀铜与光刻。新光电子的i-THOP技术在有机基板上直接制造2 μm线宽/线距的薄膜层,满足高密度需求。

. H& W$ ?. K$ A1 u: m

1bie1dezium64057677310.png

+ x, U& Z5 K$ Z2 A6 E) q: N; A* ]图4: 新光i-THOP工艺,在有机积层基板上制造2 μm线宽/线距的薄膜层。

5 f) `/ T# U. ~5 m, \: e3 U% ~' E' _, k( R+ v

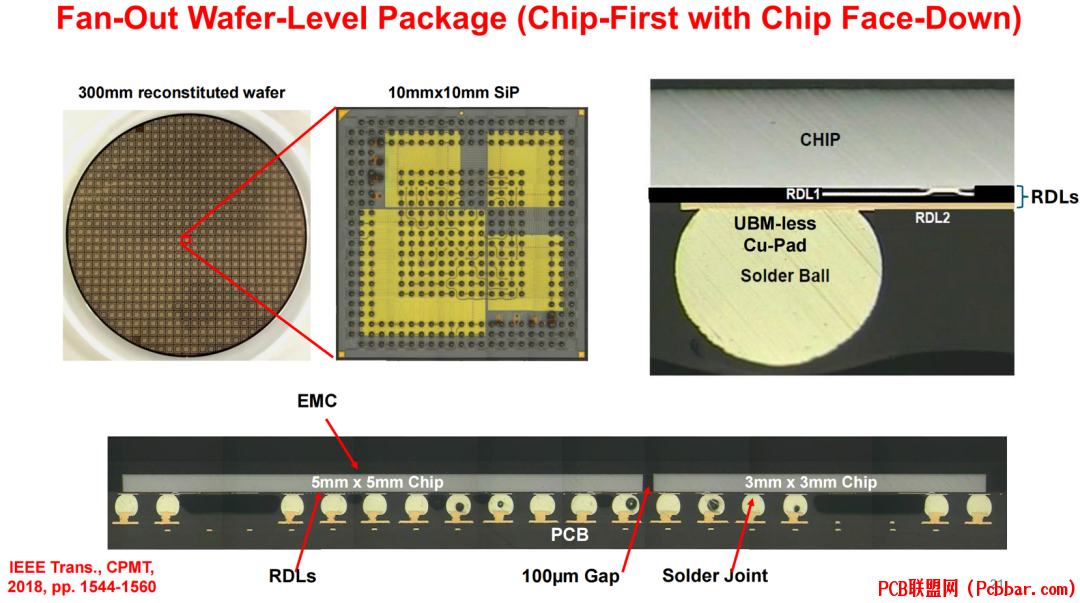

扇出型RDL技术,扇出型晶圆级封装(FOWLP)将Chiplet嵌入环氧模塑化合物(emc),通过RDL布线。台积电的InFO技术省去焊球与底部填充,使苹果A10处理器封装厚度降至825 μm。

. }* u6 V- A# ]7 I9 M& b

exlwf5iflq364057677410.png

3 x, t/ E- e0 ~/ K9 @9 l: x2 U图5: 扇出型晶圆级封装,重构晶圆上的RDL连接多个Chiplet,省去传统基板。

9 L" z) `# t$ Z$ p3 `( j; ]& k; j* O# C0 R% f' R- O

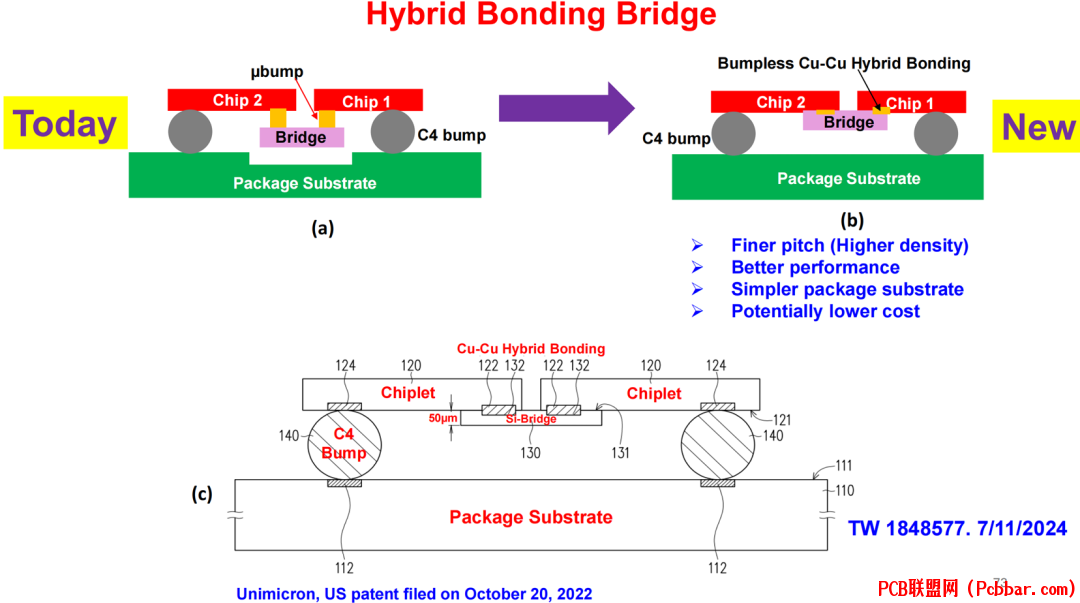

混合键合工艺,混合键合以铜-铜直接键合替代焊球,实现亚微米级互连间距。欣兴电子的工艺通过抛光铜垫至原子级平整度(- c3 z1 I: k4 ]2 M! U. ]

k3eoex0dewd64057677510.png

" A; V6 n4 b9 `4 S图6: 混合键合工艺,无凸点铜-铜键合实现高密度3D集成。. |% q: r* C$ R- B

质量控制与测试方法9 s1 c9 Q5 |1 ?

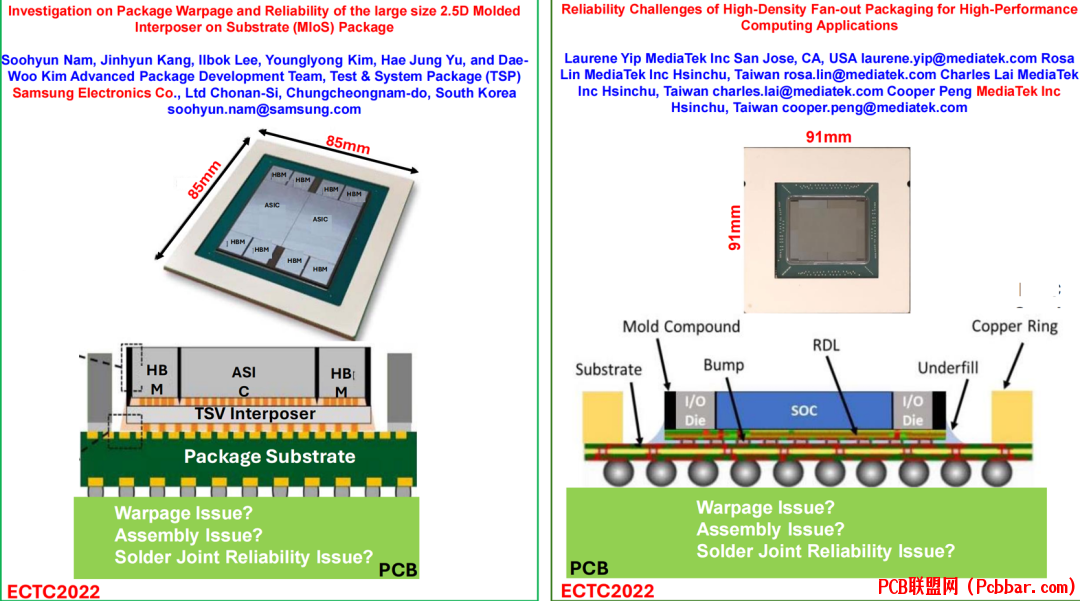

: j3 Y9 N. q+ W翘曲测量,基板翘曲通过云纹投影或激光扫描测量。台积电的CoWoS-R要求大型中介层(66x68 mm)翘曲

& @9 E* ^* s5 ^& ^

ywsuj53l51i64057677610.png

8 u) b0 w7 b* c

8 u) b0 w7 b* c

图7: 模塑中介层翘曲分析,91mm中介层在热循环中的翘曲分布。

( k0 \% ]( }! a1 |+ K# A/ s' t4 G; M# c" p) V f% B' l7 L. H {( g- b# g! |

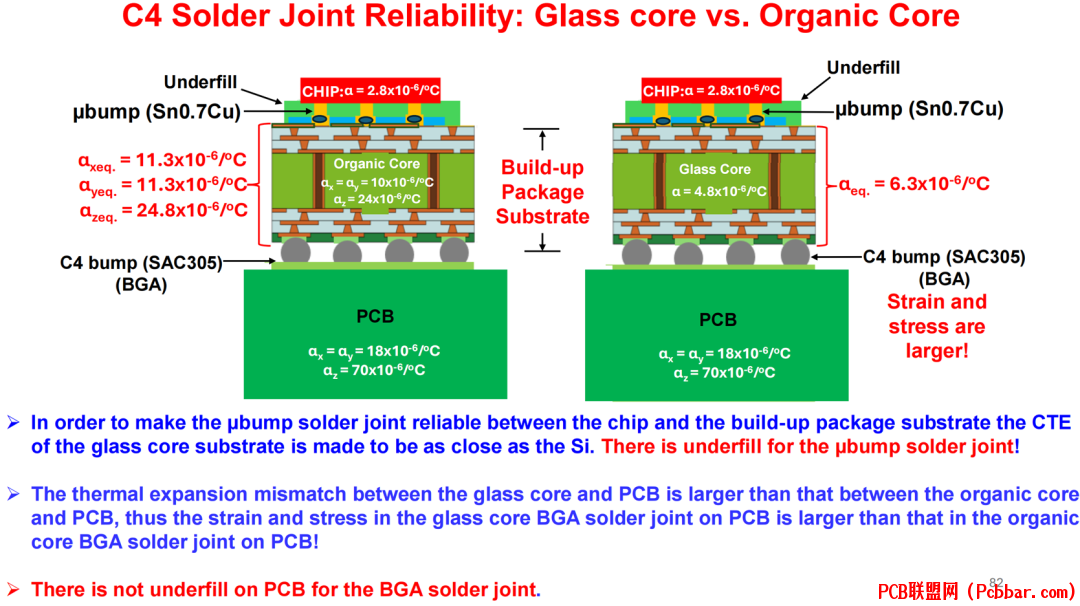

热循环可靠性测试,热循环测试(-55°C至125°C)评估焊点可靠性。有机基板(CTE=24 ppm/°C)在C4凸点的热应变高于玻璃基板(4.8 ppm/°C),如英特尔的对比分析所示。

5 I$ T C7 l+ ^) l% f# Z) L, Y

weoj5ydmev264057677711.png

5 L& C# P. [: } U: a0 N+ _8 V图8: C4焊点热应变对比,玻璃与有机基板在温度循环下的热应变差异。3 R3 H$ X4 m) _3 R( Z4 M

! w; d. O2 p! _/ I

电性能测试,高频探针台验证射频与光电子基板的信号完整性。博通的3.5D XDSiP使用时域反射计(TDR)确保10 TB/s互连的阻抗匹配。6 R& h" Y: D; P* \: b

基板制造新兴趋势9 ~* m! e& D5 {3 B6 G/ v; }

1 f& _1 x1 b& ?玻璃核心基板,英特尔的玻璃基板瞄准数据中心与AI应用,支持3320 mm2级封装。挑战包括高初期成本以及与PCB的CTE失配,需开发免底部填充工艺。

1 z) p' s! f7 H, c2 {, H) K

sp4xdcfkghd64057677811.png

9 u% c4 D, o& G2 S+ w# s; D

9 u% c4 D, o& G2 S+ w# s; D

图9: 英特尔玻璃基板路线,从有机向玻璃基板过渡,支持超大型封装。

1 O8 v$ B7 T" a4 u+ m" o: ^. t, }$ u/ ]: r+ L

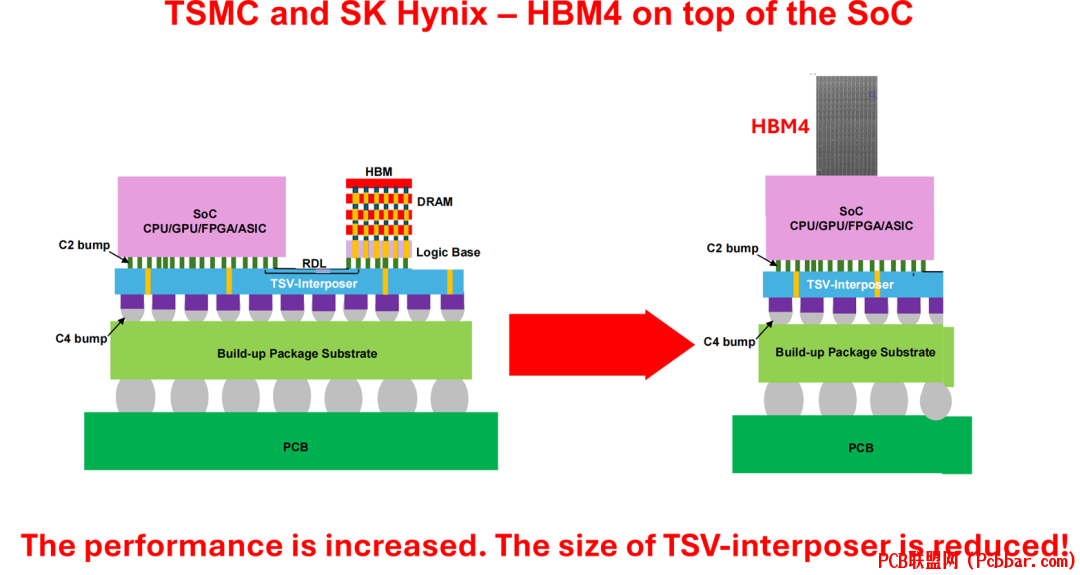

3D混合键合,台积电的SoIC与英特尔的Foveros利用混合键合实现芯片面对面堆叠。SK海力士的HBM4通过该技术将HBM直接堆叠于SoC,降低延迟与功耗。

2 e- V9 q1 U0 w" }8 Y m% X

b2dxpuzd5w164057677911.png

/ L) H5 S% }6 j* {2 F) V$ ^# F

/ L) H5 S% }6 j* {2 F) V$ ^# F

图10: 3D混合键合集成,HBM4通过混合键合堆叠于SoC,优化性能。

: d+ ~: {0 j( s

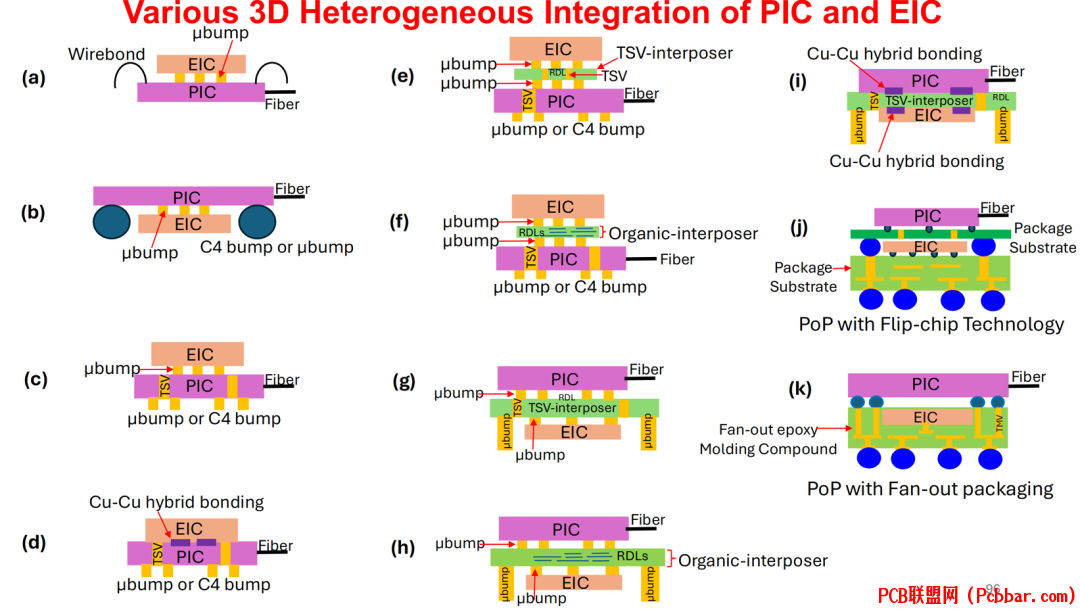

5 W/ f" s; Y+ Y/ p光电共封装(CPO), CPO将光电子集成芯片(PIC)与电子芯片(EIC)集成于同一基板。思科的设计在玻璃中介层中嵌入激光器与硅基光电子,实现1.6 Tb/s光互连。6 a- Z Y9 |" H1 n5 t2 X

kgw5nbjwlms64057678011.png

+ `3 _" ]0 W; ]3 ^1 A+ q

+ `3 _" ]0 W; ]3 ^1 A+ q

图11: PIC与EIC的3D异构集成,光电共封装的多配置方案,含TSV中介层与混合键合。

7 ]$ h4 |. S6 r1 h% _; Y$ ~& ]4 g+ |. A

面板级工艺,面板级扇出(PLP)通过大尺寸面板(如600x600 mm)提升制造效率。欣兴电子的混合基板结合ABF与PID介质,实现5 μm线宽/线距的RDL。

. \+ T2 X( I+ ~/ `. u9 d3 E

3kgfb1cbquf64057678111.png

- P! m8 [, B7 E0 g$ d图12: ABF与PID混合基板,ABF积层与PID RDL的剖面结构,支持高密度布线。

5 L6 H1 E, R7 a5 @' f, D总结1 l: R# e$ K* f+ D

, Y( W" H( S) q: |$ k+ H先进基板材料与制造工艺是下一代半导体集成的关键。有机积层基板凭借成本优势主导消费电子,硅中介层与玻璃基板满足高性能计算需求。混合键合与扇出RDL推动3D集成迈向更高密度,但热管理、翘曲控制与标准化仍是挑战。玻璃基板与光电共封装等新兴趋势,凸显材料科学、工艺工程与系统设计跨领域协作的必要性。

l, Y7 x: p6 y1 f# C0 T+ y Q* ?参考文献

1 `! n- _7 t$ q

+ C3 V) e) F* w# J1 X% w, y[1] J. H. Lau, "Advanced Substrates for Chiplets and Heterogeneous Integration," presented at the IEEE/EPS Distinguished Lecture, School of Integrated Circuit, Tsinghua University, Beijing, China, Jan. 22, 2025.

3 V8 E$ A+ C3 C- A* ^END$ @5 ^4 L4 L* U4 s. u

软件试用申请欢迎光电子芯片研发人员申请试用PIC Studio,其中包含:代码绘版软件PhotoCAD,DRC软件pVerify,片上链路仿真软件pSim,光纤系统仿真软件pSim+等。更多新功能和新软件将于近期发布,敬请期待!

& J3 {; F/ R* P V! B4 q2 @点击左下角"阅读原文"马上申请

" M" Z( h6 X" V0 \% f* k3 k1 }5 L* }) X4 v: |* B

欢迎转载2 d: h3 E# p3 j l, A, {/ f

$ Z8 _$ k9 b- d/ \9 X6 _3 Q2 |- Y

转载请注明出处,请勿修改内容和删除作者信息!

# ^: Y# `* P) ]. l* b

9 n# p# Z/ J4 ]/ O8 P+ v7 A7 ~) o- q1 r4 |+ i; k1 c4 Y

c" \5 t7 ]/ H2 D" V! a5 t

z2cf134o3y464057678211.gif

+ g2 {5 ?( ?8 c R! [( t0 |2 v7 ~9 K, `' R! b0 b) e% r" M4 `

关注我们

0 O: R' d! E3 T# [" n# b3 n6 z: t8 v6 N

$ E1 h) v7 A4 c# |

okq4vmicdlo64057678311.png

) {" ^/ \& L! b& G( s

) {" ^/ \& L! b& G( s

|

) S1 a% P% L6 u# K8 m! }

5t5ukp23fjd64057678411.png

2 X2 {0 {' U' A |

3 h! w! e5 U) R" }0 q8 i! I

s5krdnm1jbn64057678511.png

. d$ E! D4 T$ x- w2 _5 J! }

. d$ E! D4 T$ x- w2 _5 J! }

|

; _, ]6 X3 K3 S* j3 Q6 h% R! c. F6 [. ]" z# {+ W/ z* |5 e7 f

. G, y; ?0 W M5 j2 g0 O ~6 r4 `% |8 ~9 ]/ Y0 \6 ]

关于我们:

- C8 X$ w4 s1 R. a深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

7 I0 N- |" I1 P8 R, y

( x Z R& W% O6 Ihttp://www.latitudeda.com/$ `- u( t: R! z6 \$ e- V8 F

(点击上方名片关注我们,发现更多精彩内容) |  /1

/1