|

|

引言, t/ y' \. Z% z9 K) @

在亚2纳米半导体技术领域中,供电网络设计对高性能(HP)和低功耗(LP) CPU的性能发挥着关键作用。本文引用IEDM会议论文分析了最新的背面供电网络(BSPDN)技术,比较了不同架构在热性能和供电完整性方面的特点[1]。

4 j/ y y6 Q, M6 ]0 B: J

1g0vpgua3m16405303523.png

7 E H6 H9 k! H3 H! V

7 E H6 H9 k! H3 H! V

4 A9 z/ a* C. X; b0 ?/ K n5 ~

首先介绍基本的BSPDN结构。随着技术的发展,多种背面供电架构已经被提出用于解决先进制程CPU的供电问题。3 d- G" |+ ^3 F0 s- Q

a2ljk3fft4u6405303623.png

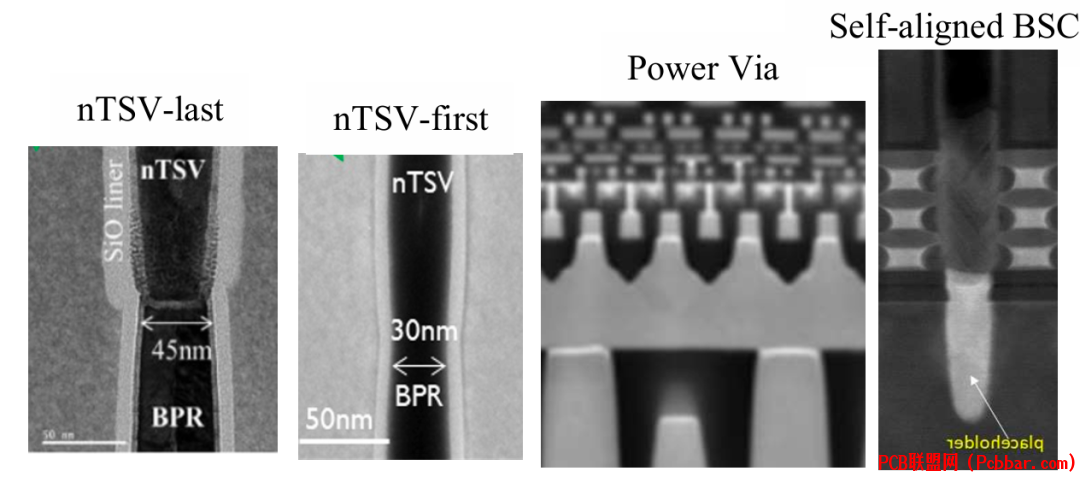

' {7 O; C! C4 R- Q, C0 |图1展示了不同的先进BSPDN局部连接方案,包括BPR+nTSV last、BPR+nTSV first (slit-nTSV)、Power via以及self-aligned BSC等设计,这些方案分别由主要半导体公司开发。, |5 T) y, B( |1 Q5 H

+ o r6 S/ a# W) w% b8 {" r

4yiz052fvxq6405303723.png

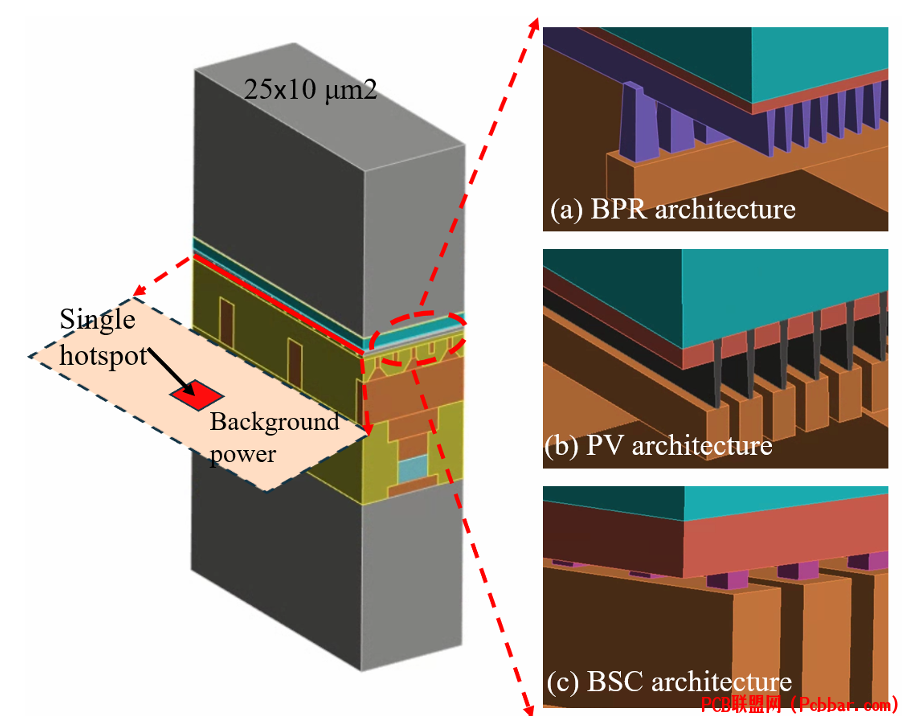

( r& n4 a# P0 S8 Q b( R图2说明了不同BSPDN方案的结构示意图,重点展示了背面供电连接触点以及各种架构中的局部和全局供电线路。

5 Q% T: e! O. s& Y6 \' P* {) z( D" y3 G5 v

这些架构的根本区别在于向晶体管层供电的方式不同。每种设计在制造复杂度和电气性能方面都具有独特的优势和挑战。3 ^" F; H$ V' @1 g- ?' @

6 A9 S. d& ~4 y j& c- V* B V9 ]1; m. V% E1 ?" T; X1 W

技术参数与设计考量0 i, z6 K2 j' Y1 \' q

在评估BSPDN架构时,需要考虑多个关键参数。供电结构与器件层之间的接触电阻对整体性能有重要影响。

! Y! l x8 g- D3 Y. z' u" t

5vdaplimia36405303823.png

, @: \" [- l/ l4 P

, @: \" [- l/ l4 P

表1列出了不同BSPDN方案中局部供电导线组件的详细电气参数,显示了从BPR到BSC技术在接触电阻方面的显著改进。

% E; G1 E# r6 U. C

' [ J* q2 r; L4 r0 |+ N( f0 O3 R2 f& T功率密度分布是CPU设计中另一个重要因素。高性能和低功耗应用对功率的要求差异明显。- L U: P* J$ Y* d& B$ P( P

dbetpvjagnv6405303923.png

+ |% R. }3 {- C图3展示了HP和LP&HD CPU的功率密度分布图,显示了这两种设计在功率需求上的巨大差异。2 i8 @# v" _, P) [

. q7 v) {7 G! j1 N- n5 u24 I/ U$ m, }1 g- ?

热建模与分析

0 |0 c$ [5 V b; {- W理解热行为对评估BSPDN架构非常重要。全面的热分析需要对芯片各层进行详细建模。

2 q. S, w" f. N. }

2g44shzzjgz6405304023.png

/ d* F: G/ A1 N7 J

/ d* F: G/ A1 N7 J

图4展示了后端布线(BEOL)的热建模方法,包括完整BEOL模型和有效热导率计算。+ ]/ I: w" V9 Q2 a" M7 u: k5 A

% t& u$ u! u& b' P; G( g W

0fufmotdiy26405304123.png

$ _$ D. t, a/ f2 N$ R, w/ M0 d图5展示了不同架构的背面互连建模细节,包括前端器件层(FEOL)、后端布线层(BEOL)和减薄硅衬底的实现方式。" y+ K1 b% D* E

& \2 M0 B+ f$ c3 j, ~0 r热建模同时包括封装级和局部分析,以捕捉各种热效应。9 s2 ?. ~9 d$ O8 H# x% s

' q) c5 l, E& q8 K7 N6 a

mkf0er1ehdk6405304223.png

: v& O" h9 j' m. m$ g; w0 y8 O图6展示了采用等效层的整体芯片建模方法。

z4 D% H t' k0 H9 F8 ^) L

9 g$ F5 h5 f/ s

iu1lc1id15p6405304323.png

& j2 u. G: V) p9 o8 o$ I

& j2 u. G: V) p9 o8 o$ I

图7说明了三种背面连接架构的局部热建模示意图。

: s# Q! A4 {1 L2 ^! H

$ D3 K* q. ]/ w2 R6 X1 v( \) h3& q3 s+ o" R, t% q2 L

性能分析与结果7 } x+ ?. Y5 _* Z6 j$ M }9 B. {: D4 \

热性能分析揭示了不同架构间的有趣规律。+ Z5 [8 W4 I: u& D P$ k

dqbwn0voncx6405304424.png

: v( ~) d" c" ]4 `4 O- q$ n, _; F

: v( ~) d" c" ]4 `4 O- q$ n, _; F

图8展示了采用500nm减薄硅衬底的BPR架构的逐层温度分布可视化结果。

$ D2 t2 ]6 v) X5 O |

ocrkdkrw3s56405304524.png

/ v5 e( x1 K! @* }8 ~8 S$ K( s9 W

/ v5 e( x1 K! @* }8 ~8 S$ K( s9 W

图9显示了具有详细背面互连的整体热建模的垂直温度剖面。2 O$ z$ g, W' o# ]- y* F( y

6 C, x. e6 f7 L; n# H

不同衬底厚度的温度变化为热管理挑战提供了重要见解。' i. v% d; a2 B, u

uwg2ar0cdv06405304624.png

( D0 P& C1 H3 |# J* W1 F! f" Y M1 C

( D0 P& C1 H3 |# J* W1 F! f" Y M1 C

图10展示了不同PDN结构和衬底厚度下整体热建模的最高温度比较。+ u/ {5 z/ h$ D- g

/ N u) U! |0 g

4e2p1sbmlqq6405304724.png

# j E2 T: F! e

# j E2 T: F! e

图11说明了高性能和低功耗CPU设计中最高温度随硅衬底厚度变化的趋势。

& ?+ h0 l# o# p& T5 c2 x& E, s. u5 {) u

供电完整性分析显示,与传统正面供电相比,背面供电具有显著优势。% |& _# ?) _# j- e8 ~# I

mlizu2figjp6405304824.png

* R9 k4 [2 Y2 }# [, f& r2 _图12展示了功率密度图分析的多个周期和不同BSPDN技术的IR压降累积概率。, L9 p3 K/ Y* `- f x3 @! a- u; H1 _# v

. T5 @& `% h2 ], [+ v

分析涵盖了动态和静态场景,并考虑了工作温度的影响。

+ d% V3 l6 \) ^- H$ B

5kzg1c3nnlq6405304924.png

7 W: M* `0 u2 G% L" \图13展示了LP和HP CPU中不同PDN技术的98百分位动态IR压降比较。7 ~' [/ V/ B6 h8 r

$ `8 h8 @9 N/ F# p4 B; H

zsmpwtrq2ea6405305024.png

~+ p" S. \% \+ a; v8 Z图14显示了背面M1或正面M1节距对动态IR压降性能的影响。

2 J1 W3 n% P8 \+ y. b, _+ _8 o% E1 ?! \

通过这项全面分析发现,尽管BSC技术面临热性能挑战,但在供电完整性方面表现出色。而PV架构在热性能和电气性能之间提供了良好的平衡。这些研究结果为先进工艺节点下的CPU供电网络设计提供了重要参考。4 h1 ?( u& D. G9 q: F# e4 F& o' p

- \/ A F, K9 L+ v5 B参考文献

+ K4 q& N! {; Y, X[1] L. Wang et al., "Power and Thermal Integrity Analysis of High Performance and Low Power CPUs at Sub-2nm Node Designed with Various Advanced Backside PDNs," to be published in 2024 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2024.9 r, Q1 y! }% r. j$ R* R

END

4 } O7 q( Z" J3 G& ?) `软件试用申请欢迎光电子芯片研发人员申请试用PIC Studio,其中包含:代码绘版软件PhotoCAD,DRC软件pVerify,片上链路仿真软件pSim,光纤系统仿真软件pSim+等。更多新功能和新软件将于近期发布,敬请期待!4 z# Q$ Z* ~! Y' E; \3 F

点击左下角"阅读原文"马上申请0 A+ S) g6 u* {1 V4 @

1 m( a- H$ y% x" i, y欢迎转载

& b8 U( n: }$ R% w8 u# N' y9 w

1 d1 J# [, N& R# z% G! l转载请注明出处,请勿修改内容和删除作者信息!

; ~& V9 i9 ]& |9 Z2 I" ^; I

, ?! [ K6 B m/ r2 D0 q

* M, S. @: F4 _' s/ H6 }. i2 V3 b2 c, T/ I

z15bfljx4yg6405305124.gif

Y3 k! u5 ]& L" j1 u

Y3 k! u5 ]& L" j1 u

3 d$ k% B4 a% C# X% v3 s关注我们

" N1 j4 F$ [+ X T8 \5 n

5 P/ r3 q2 S7 l7 ?: W) S2 \0 i& f2 l1 z

3q4jzwc42a36405305224.png

# F; n2 e" V' q4 z6 n9 A0 W

# F; n2 e" V' q4 z6 n9 A0 W

|

* w' R9 F3 o. y3 _2 m; N

k2x11s3f0vg6405305324.png

2 d2 u5 ]6 Z+ g

2 d2 u5 ]6 Z+ g

|

$ Q# w1 K, ? C9 y

4oi3mkueirr6405305424.png

* A: m* f: K3 P |

7 |! s" m0 A4 P# k2 d( H

. h p: ]' l5 f5 ~) u$ x8 }$ W5 ]0 C

/ \. H4 D# ^8 ?2 ]8 {

% V5 h, q+ I5 b2 ~6 d! v关于我们:

; r; b3 A: P- A1 {4 |; f+ Z9 v* t) F深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

3 [' D8 a8 g4 [8 a

8 z" b* L! r S; L( x7 Shttp://www.latitudeda.com/

\: a6 T+ a5 s(点击上方名片关注我们,发现更多精彩内容) |

|