引言

5 E. u9 u: d9 K+ Z! u/ N+ O# r$ L极紫外(EUV)光刻技术在先进半导体制造领域扮演着重要角色,能够实现更小尺寸和更复杂集成线路的生产。本文通过TSMC专利来介绍EUV光刻掩模技术,包括基本结构、设计考虑因素以及在半导体制造中的应用[1]。: h3 T9 v- [8 K. f8 P1 Z

i2rhr1fsa516401576918.png

' B" A+ g6 ]1 U. }" P: n& L i

' B" A+ g6 ]1 U. }" P: n& L i

- `$ u7 l6 D% C* C1 x

基本结构与组件% }% U& I7 n% @& ^$ f* l8 S+ V

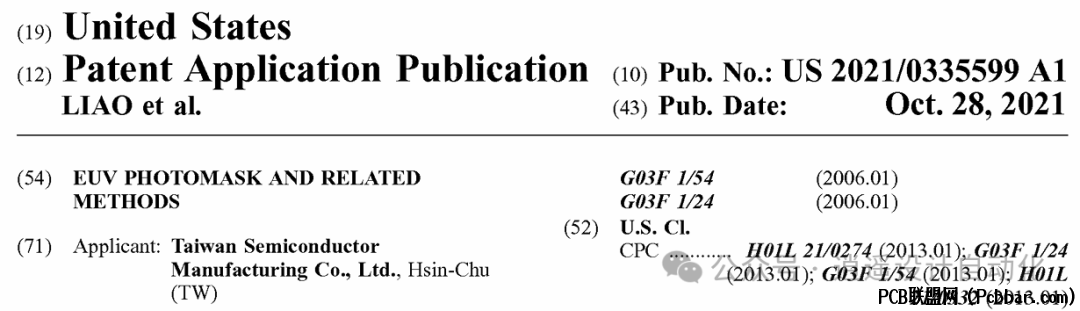

EUV光刻掩模是将线路图形转移到半导体晶圆上的模板。图1说明EUV掩模的基本结构:/ K; m: r7 q* G/ Q' {

aorf3c4j13x6401577018.png

! A% a5 [; V$ f+ |

! A% a5 [; V$ f+ |

图1:EUV掩模的横截面视图,显示了包括基板、背面涂层、多层结构、保护层、吸收层和防反射层的多层结构。

- D9 n1 x3 s- Y- }/ U6 i* `5 B; e) q/ j! Y

EUV掩模由多个关键层组成,每层都有特定用途:8 W) H9 q, P) q

基板通常由低热膨胀材料(LTEM)制成,例如二氧化钛掺杂的二氧化硅,厚度约为6.3至6.5毫米。在基板上涂覆70-100纳米厚的氮化铬(CrxNy)背面涂层。

) I9 W: f7 U5 a9 |采用离子沉积技术在基板上沉积钼-硅(MoSi)多层结构。这种结构的典型厚度为250-350纳米,每对钼-硅层由3纳米钼层和4纳米硅层组成。

3 l1 w# a8 h S' L4 u" H5 z在多层结构上覆盖约2.5纳米厚的钌(Ru)保护层。该层具有双重作用:在制造过程中保护多层结构,并作为随后吸收层刻蚀的终止层。8 x( P/ c' z. Z" L0 q2 S3 y

吸收层可由TaBO、TaBN或Ta2N等材料制成,厚度为50-75纳米,设计用于吸收波长约为13.5纳米的EUV光。; \6 G& `0 O2 S) z- x

+ s8 U* f- l4 OEUV光刻系统运行3 r) }5 a! _5 J9 y0 u! O4 G- g

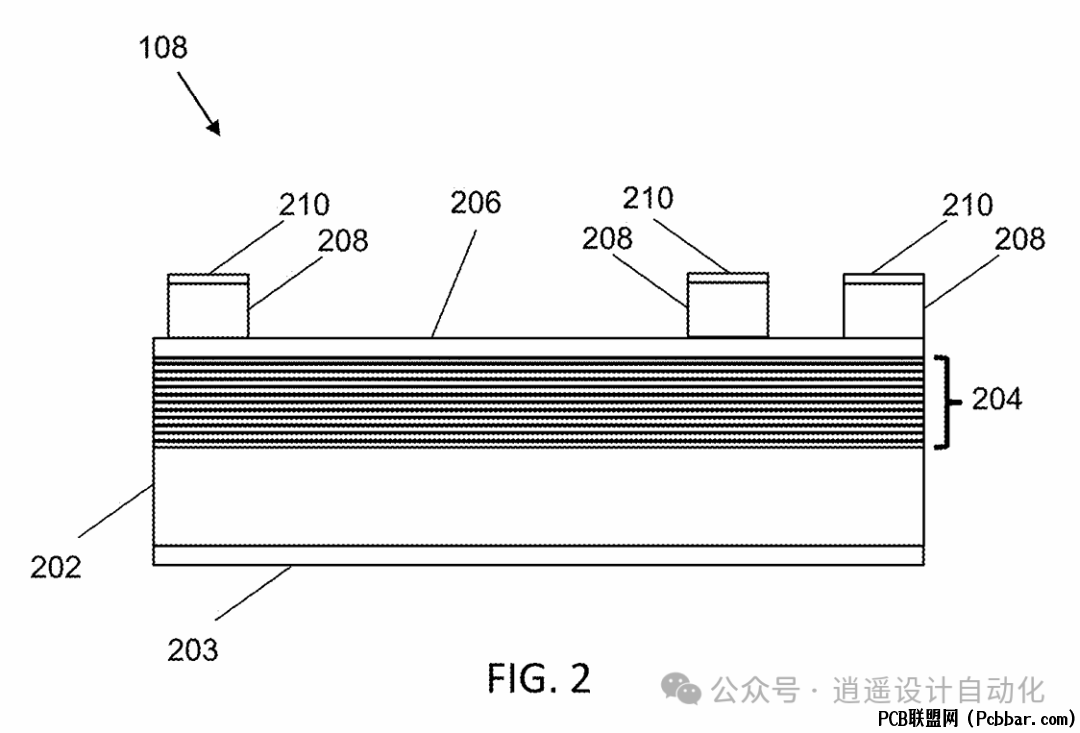

让我们通过图2来了解EUV掩模在光刻系统中的工作原理:, `, ^: m7 I2 n: T

aqbk0ibv1cz6401577118.png

: x! e+ b7 P% W7 w' l0 A8 _( O图2:EUV光刻系统示意图,显示了辐射源、照明器、掩模台、投影光学系统和基板台。- @% b/ m+ j5 L! e I/ R# B

. H% \6 {7 Y. r; p: Z2 B; X

EUV光刻系统在高真空环境下运行,包含以下主要组件:+ H$ k y3 H. N' S( ^2 i2 \, I6 l

辐射源产生波长集中在13.5纳米的EUV光,通常使用放电等离子体(DPP)或激光产生等离子体(LPP)光源。

; `% `/ X. V: _" k3 J! F照明系统含有反射光学元件,用于引导和成形EUV光照射到掩模上。

& i c; B. x, p系统可配置为轴上照明(ONI)或离轴照明(OAI)。- E+ c- G! \# W8 N) k, e, \

投影光学系统收集从掩模反射的EUV光,并聚焦到涂有EUV敏感光刻胶的半导体基板上。! O1 a/ M" c& p

2 e, D; \* ~, `1 B4 f9 l掩模设计创新" h! Q: S5 J, |3 F0 \& D

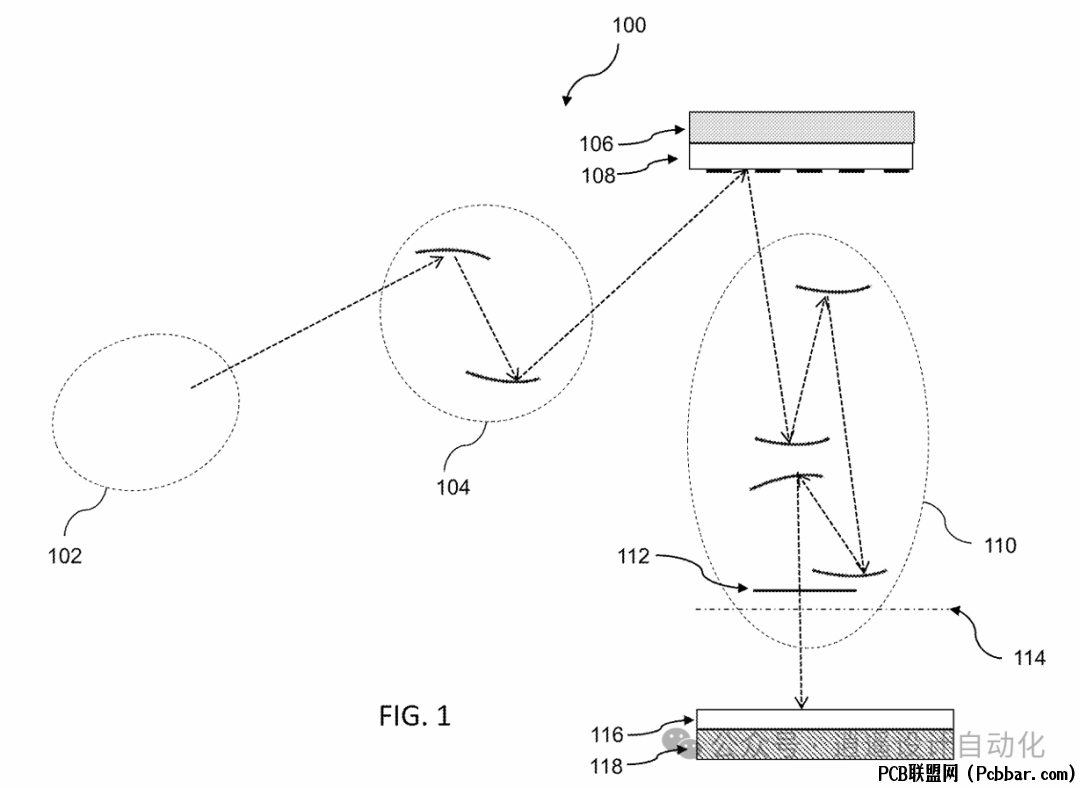

EUV掩模技术的重要进展是引入专门的开口区域来解决常见问题。让我们通过图3来研究这种设计:9 G M5 G8 @) A1 H# c, o6 H

rxjzqr1rqd36401577218.png

8 ?9 f. B. p! U5 d/ f _3 Q, D

4dvb3waur346401577318.png

' r- T" G3 {, M( k$ I( D {. |图3:EUV掩模的俯视图和横截面图,显示了主图形区域和用于防止表面起泡和层分离的开口区域。3 l$ b8 D8 d& @- Z

" X6 |3 \- y2 F8 P; ?+ T$ ^% A) Y

创新的掩模设计包括用于线路特征的主图形区域和特定间距的专用开口区域。这些开口区域用于释放曝光过程中产生的氢气,防止氢气在吸收层和保护层之间积累,否则可能导致起泡和脱层。" b1 y, P" H+ m4 F9 W/ s( B/ R

( ?1 l; g! q2 k9 X实际应用和制造过程

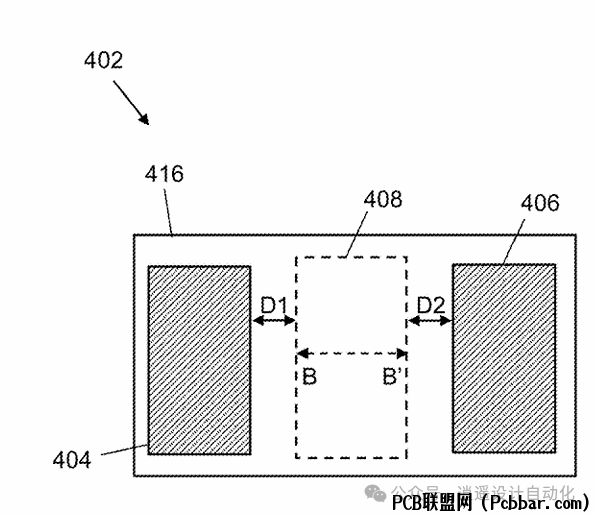

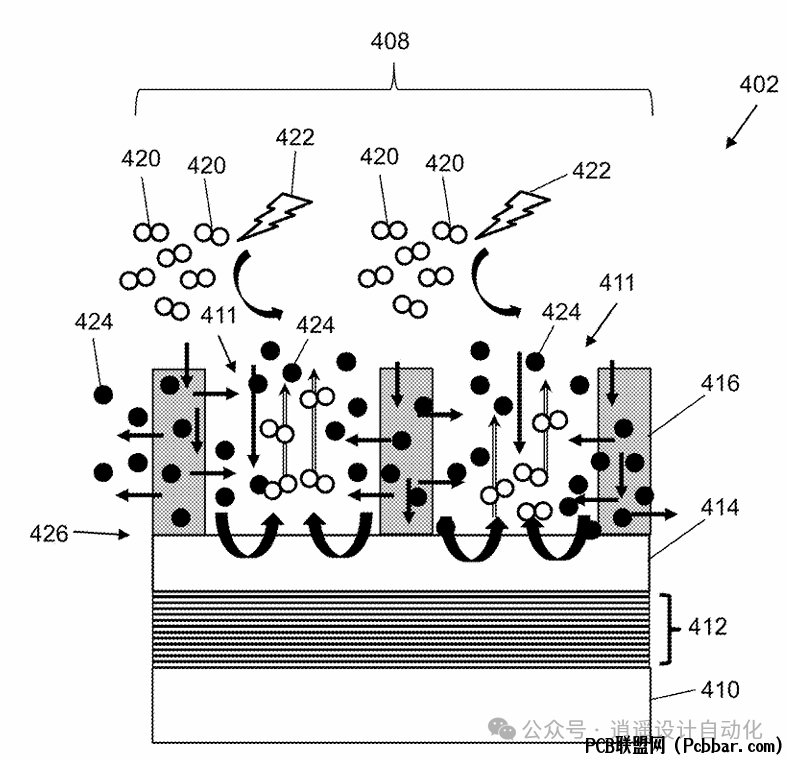

7 k; u. V& R' q6 s# A* S1 c7 dEUV掩模技术的实际实施涉及系统化的制造过程,如图4所示:

$ Z& C) U" t$ ]) W

epqrqirc3ec6401577418.png

. k8 s6 j, }! L

. k8 s6 j, }! L

图4:使用EUV光刻掩模进行半导体器件制造的步骤流程图。

( j: a. z5 T6 D! z. N, w9 U( @. v; B+ L" i' a; t: o4 p( S/ Z# @* K

制造过程包括以下关键步骤:基板制备、光刻胶层形成、使用EUV掩模进行曝光、显影已曝光的光刻胶,以及通过图形化光刻胶层中的开口进行后续制造工艺。

6 @$ P* Y8 n# {0 h$ F" a5 o- ~- n0 E- ^

这个过程的成功很大程度上依赖于在多次曝光循环中保持EUV掩模的完整性。开口区域等创新设计特征有助于防止掩模降解,确保图形转移质量的一致性。) `) N0 F7 A' E( H9 `) k1 w

& K( V2 ?* B9 V4 j4 u

结论7 E6 @% |$ e+ S" s. `# g

EUV光刻掩模技术在半导体制造中发挥着关键作用,使生产更复杂的集成线路成为现实。掌握EUV掩模的基本结构、设计考虑因素和运行原理,对半导体制造技术的持续发展具有重要意义。掩模设计的创新,特别是引入战略性开口区域,帮助解决了EUV光刻中的主要挑战,促进了更可靠和高效的半导体制造过程。

9 N, V- o( F/ a( E: v0 M% i

" f" ]& X4 ?- X% `- Q参考文献

9 p9 X' N1 {. F! G( A" f3 N[1] C. Liao and P. Shih, "EUV Photomask and Related Methods," U.S. Patent Application US2021/0335599A1, Oct. 28, 2021." O( e% N' z- F9 B; @' m9 ~

$ T1 {7 g# A1 n1 W2 L

END& Z0 b- p+ r6 s/ G

+ X7 Z. ]! Z5 g! h6 Q

. @0 t" j9 w- J Y& t" G6 X

软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。/ \& T( ]0 u4 G* a& ^- p% e* E( \

点击左下角"阅读原文"马上申请8 K* [/ k) e- w* P( l/ e

2 u) }; n# N1 P欢迎转载5 c9 H" z! V) I. u

# g8 J0 l( r% @' }& L3 P

转载请注明出处,请勿修改内容和删除作者信息!) a$ b, d$ `8 {) Y( G! h

/ G( s% l0 u7 u- l' H6 {8 G

# K, P; ^( a' w& s8 t5 e$ L

$ t( }% V8 j" H

uvu0tkmkdyd6401577518.gif

/ ^2 ]& p1 m' N9 e2 m0 J, ?. v+ j/ g. J

关注我们

& g+ T- m1 f2 b: L1 x

3 }. S8 s {: Q4 z5 K \! \

' ^* w* f8 Y& C, J" m

azx3zfzbmtl6401577618.png

8 h$ b [1 \0 h |

0 }) }3 ?2 h# Z. p @

n2gkejag3bc6401577718.png

& ^/ f" o* ?. @( L' j2 j8 @+ C

& ^/ f" o* ?. @( L' j2 j8 @+ C

| 8 n) c0 f) @# m

54mot1hmrzy6401577818.png

6 j. q8 ]) H# V0 t+ Y

6 j. q8 ]) H# V0 t+ Y

|

?$ E9 ?. Q: ?$ K

+ ?% C/ D# M6 I* y

) t, F. p2 \+ X; q' C4 Y# M, o

5 f- _. T; ]* A' c; l关于我们:

3 e/ H% o) p: _$ x& W) d5 a2 H V8 n深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。1 `# d! } b$ I# l) i Y

) n( ^5 u; o: U1 V- {. s9 C8 Nhttp://www.latitudeda.com/4 }: k; Z2 {9 v8 p! g& }

(点击上方名片关注我们,发现更多精彩内容) |