集成规模的理解

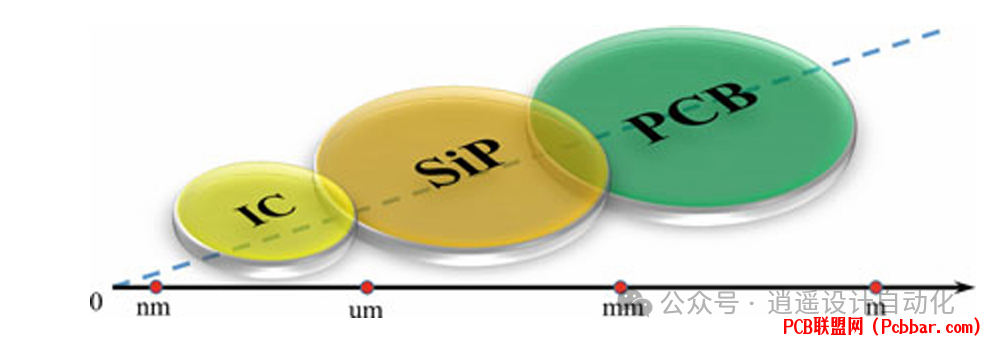

/ q- [4 I& ^& Y电子系统集成技术已经从简单的2D排列发展到复杂的4D结构。集成规模可分为三个主要类别:IC的纳米级集成(以nm为单位)、SiP或先进封装的微米级集成(以μm为单位)以及PCB的毫米级集成(以mm为单位)[1]。

! ]% J+ P4 _ v9 N

4e5igb4nngh6404969557.png

: S* t, F. u- x! p' R

: S* t, F. u- x! p' R

图1展示了集成规模示意图,说明了IC、SiP和PCB技术在不同尺度范围的分布及其重叠区域。

5 t/ X% W3 L/ h

* u h" s' P) p2D集成基础技术

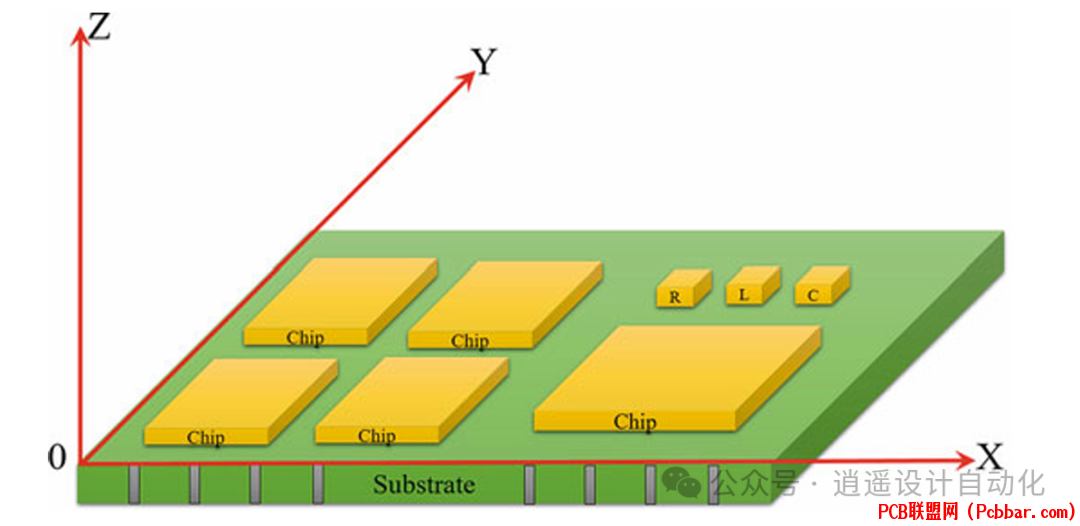

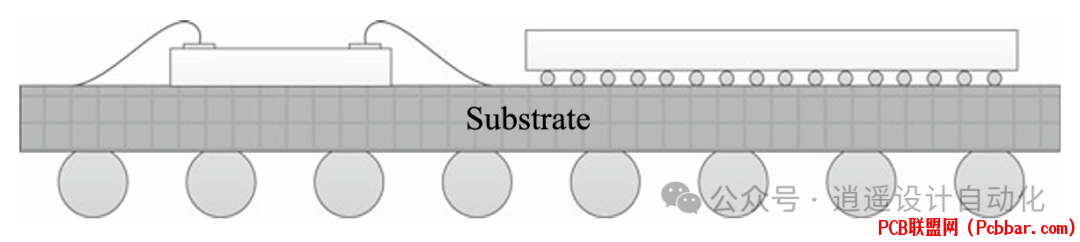

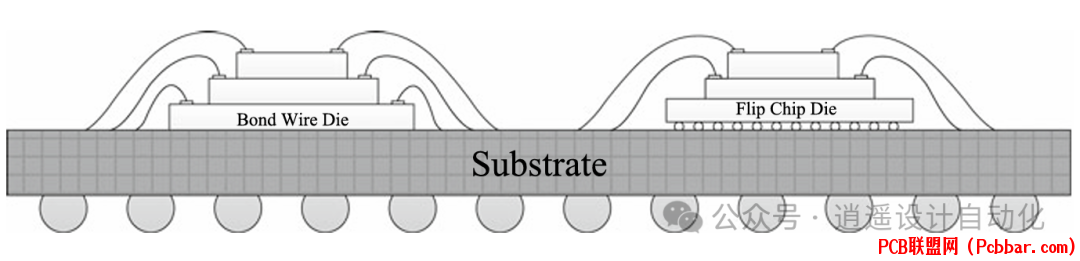

6 X1 s# ^2 N. J' P+ h* U+ E2D集成是最基本的集成形式,所有组件都水平安装在基板表面上。这种方法常用于多芯片模块(MCM)和基本的系统级封装(SiP)设计。电气连接通过基板实现,组件直接与安装表面接触。

. o0 {" j. d: A, j9 N2 e

i3wc1e45feo6404969657.png

5 ~7 Y& T+ u9 y8 H1 n \( E

5 ~7 Y& T+ u9 y8 H1 n \( E

图2展示了2D集成定义图,描述了组件水平安装在基板平面上,电气连接通过基板实现的方式。5 ?& J- A' v+ [& @

8 J* X' H+ ]+ _- ]( L! B/ u9 f

n20ohg3avt26404969758.png

: q* b4 o ^$ G图3展示了使用2D集成的SiP实例,展现了水平组件安装的实际应用。1 ^, I. O! `$ Q5 t0 v$ m

+ {9 s% ]4 H6 b1 r# ?; @- L2D+集成技术进展

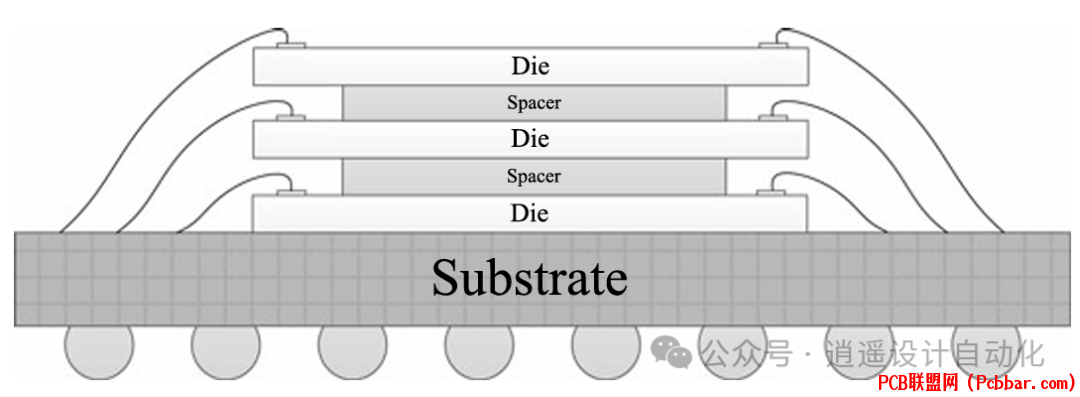

& ~, _+ V) C v4 x, O2D+集成是2D排列的改进版本,引入了垂直堆叠,同时保持基板级电气连接。这种技术提供了三种主要的堆叠配置:金字塔式、悬臂式和并排堆叠。

/ V. }( v# p' j0 s8 E5 R( F$ ^ d W

5ihtv312hwa6404969858.png

/ T' s- g% s* _- w0 d R

lodd32fanjd6404969958.png

- m+ {$ o8 L% i2 \

- m+ {$ o8 L% i2 \

mlyvqmo2ro56404970058.png

+ I/ [8 K5 C- O# V3 S/ k图4展示了2D+集成的三种主要类型:金字塔芯片堆叠、带间隔物的悬臂芯片堆叠以及并排堆叠配置。* B1 q3 W+ i' C' [5 B& z

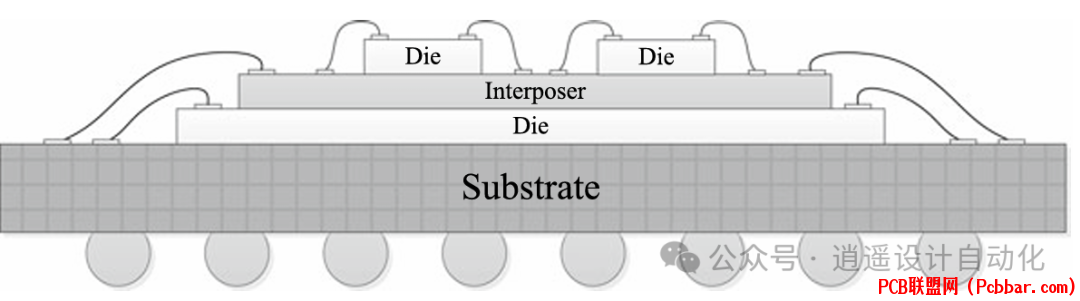

" X+ ]) L/ Q3 c& D2.5D集成技术

2 a! [, u, N. `( H7 X$ y" l2.5D集成在芯片和基板之间引入了中间层,实现了更高的集成密度和更好的电气性能。这种方法可以使用多种中间层材料,包括硅、玻璃或陶瓷,每种材料都具有特定应用的优势。0 [2 b. l; m& D! v

3xcqlnvhs4v6404970158.png

6 w/ [& I5 h- E2 V+ c/ i

6 w/ [& I5 h- E2 V+ c/ i

3igcducahea6404970259.png

; L4 _) @. T `- |5 L* h图5展示了带TSV和不带TSV的硅中间层2.5D集成实现方式,展示了不同的中间层连接方法。

: d% S" t/ j& q, Q! u h) n3 T3 f8 J# x+ O+ c, J& Q

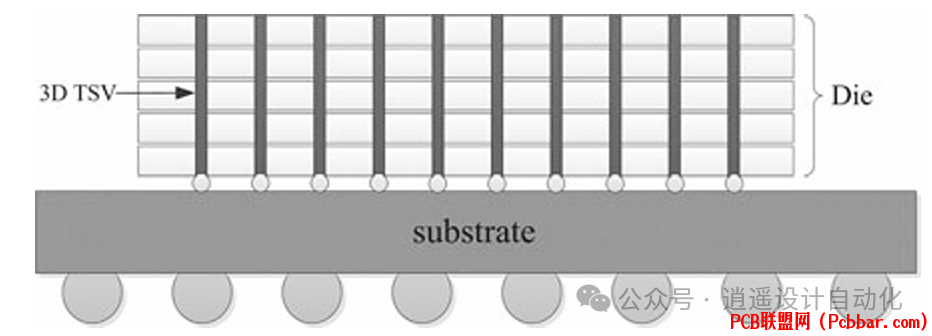

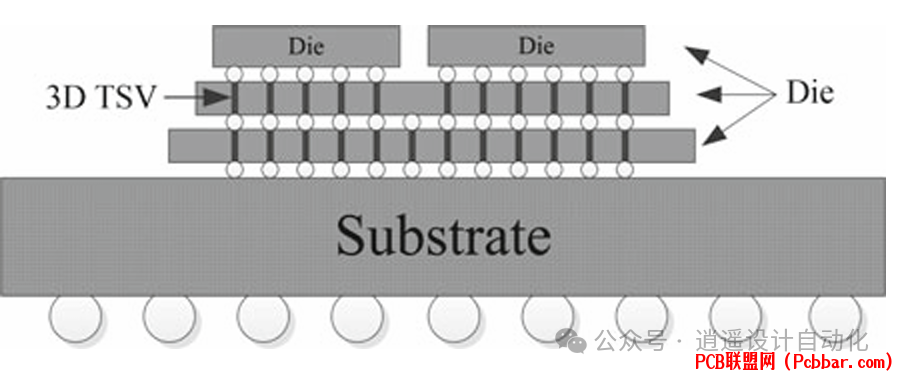

3D集成技术9 V" o+ ` Q) f, W/ B

3D集成在垂直堆叠技术方面实现了重大突破,直接通过芯片实现硅通孔(TSV)。这种技术实现了芯片间的直接连接和更高的集成密度,可应用于相同和不同芯片的组合。

9 i4 G" p v' n

3zymzwd1req6404970359.png

% k5 v' Z, |5 C6 @

za5ol5cw2u26404970459.png

+ N# A; X# j3 ~# f1 E- u, ^图6展示了相同芯片和不同芯片的3D集成,展示了TSV技术在垂直连接中的应用。

. I; `& A8 F% K9 ~+ |" X+ f- t; ]' E6 ` A$ I% Z

4D集成技术

8 }2 F; L" W& V4D集成引入了多个基板非平行排列的新方法。这可以通过刚性-柔性组合或专用陶瓷结构实现,为空间排列和功能提供了新的可能。6 v8 S0 P1 D! F B

w4zmbn3um1k6404970559.png

* H b. ^. M( ~/ F2 |

caeig25kcau6404970659.png

) b' N8 Q0 m! b图7展示了基于刚性-柔性基板的4D集成展开图和完成图。

; @' m. n7 z* b+ r9 J; G4 |* b1 h

jzbwrpb4tto6404970759.png

1 H# ^( u. r1 J" C

3dad2zsallv6404970859.png

. p' p0 c, J |

. p' p0 c, J |

图8展示了气密4D集成配置。

8 _% n7 H, s- M) Q5 F

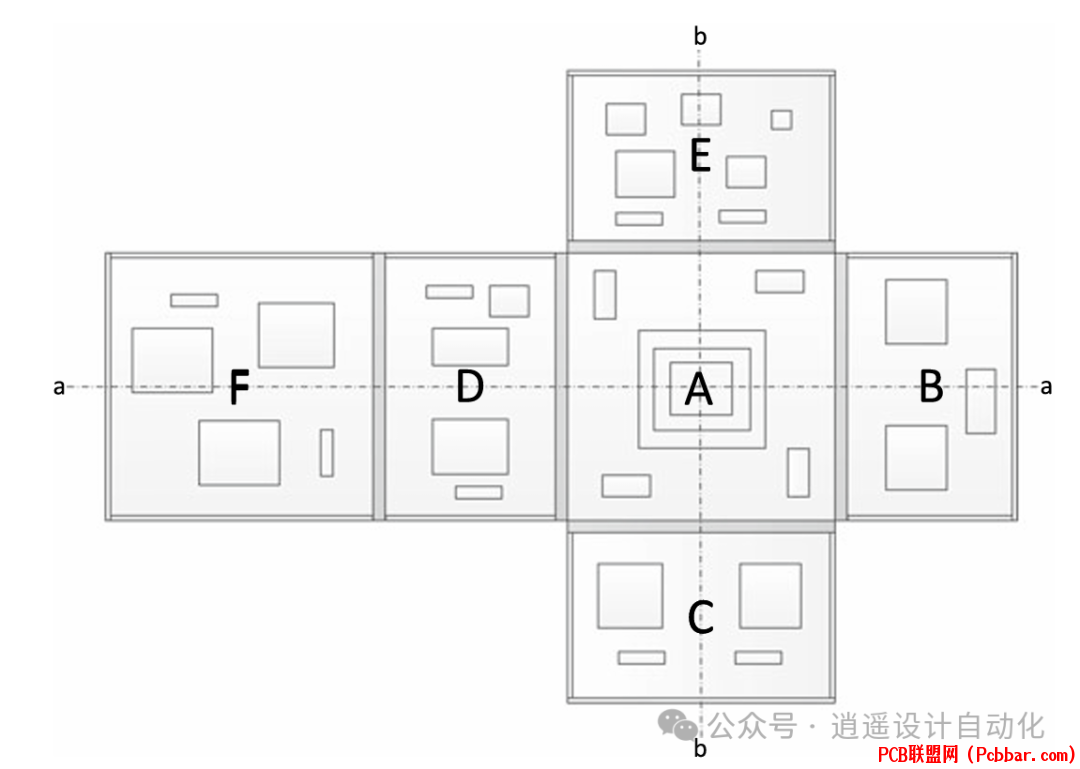

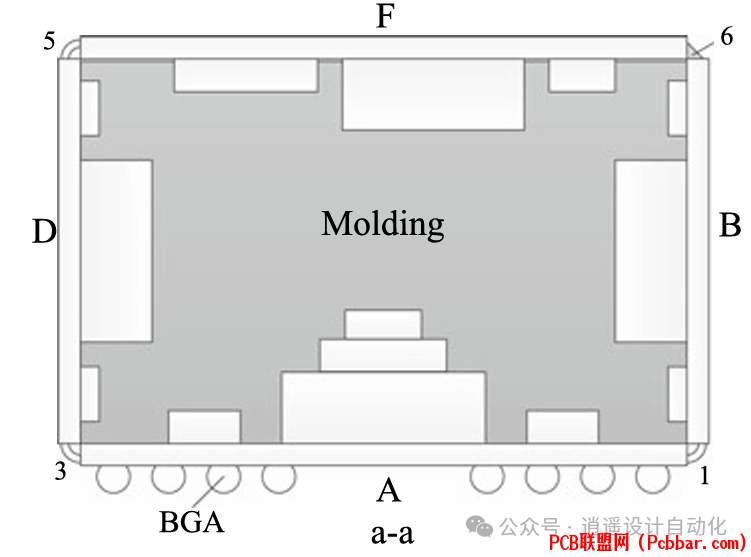

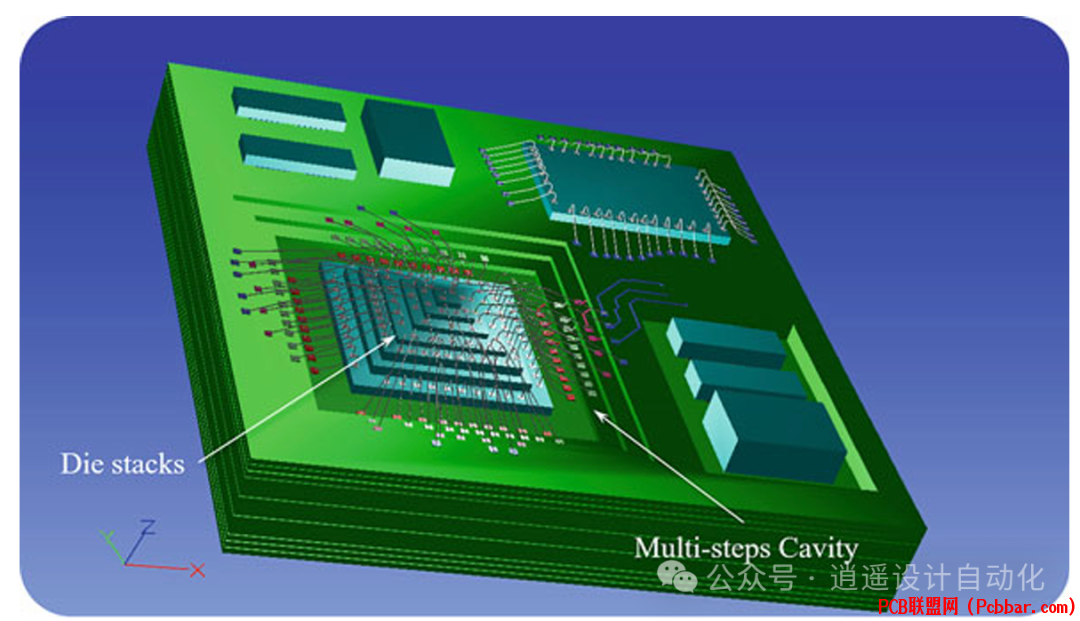

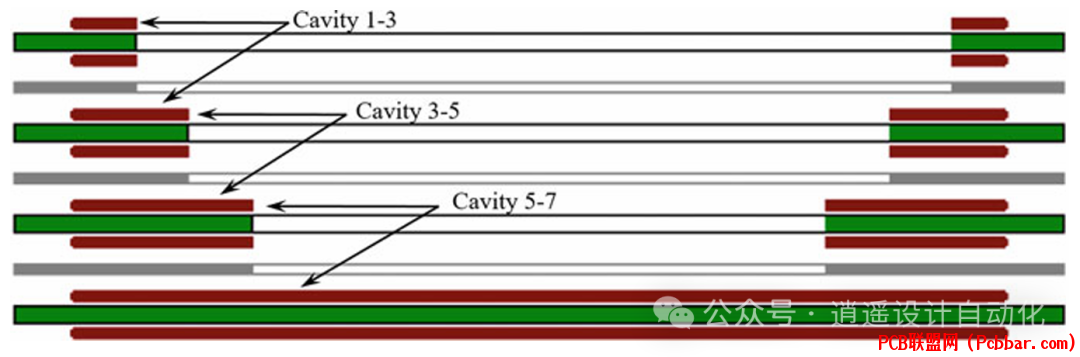

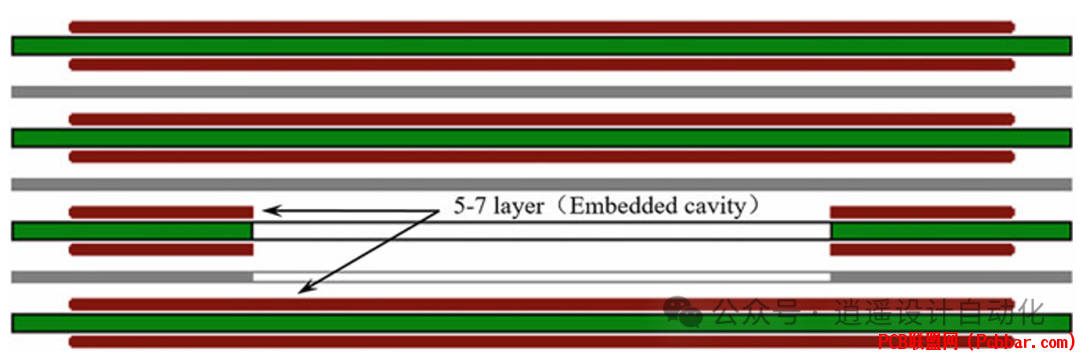

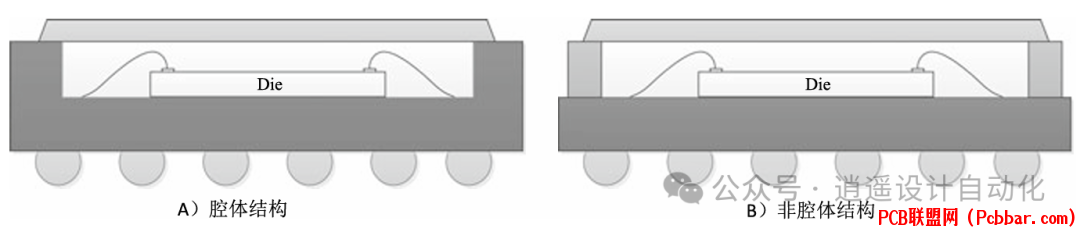

% {1 W( V/ N7 I腔体集成技术

. w$ ]+ h$ v2 P腔体集成利用特殊设计的基板开口来增强封装功能。这些腔体可以提供多种用途,包括提高键合线的稳定性、增强陶瓷封装的气密性,以及实现双面组件安装。

. D" \5 G3 _ e, s5 u! b

ap2gejq3dcy6404970900.png

/ F6 B1 V @/ ^; M% u8 f

/ F6 B1 V @/ ^; M% u8 f

sygacllcoiu6404971000.png

) y6 m. D' l* F! ]

4akmmkvi5kb6404971100.png

2 H3 k. d$ V, N# ^0 F

2 H3 k. d$ V, N# ^0 F

图9展示了SiP设计中的腔体结构、多级腔体配置和嵌入式腔体实现。

/ x) [3 d; f& _/ t! W) }

# q& K; |" I$ |+ q& }0 y$ c3 B

lgwj4utwxbc6404971200.png

8 D* m- H" u! D( N( e1 N& z

8 D* m- H" u! D( N( e1 N& z

ioxoxbwjghx6404971300.png

. e9 e5 y8 f# z; N

. e9 e5 y8 f# z; N

gal01abn1hl6404971401.png

6 ~# o+ }; o; o$ v% _图10展示了腔体集成的实际应用,展示了改进的键合线稳定性、增强的气密性和双面组件安装能力。

/ B+ u. r3 V0 A" ]8 V7 T

$ w# `4 r" L2 i( d/ v( A平面集成技术

& |! {" r w& [# {& c* O: v平面集成代表了将无源组件嵌入基板本身的先进方法。这包括通过特殊材料和工艺技术制作的电阻、电容和电感,提供了更好的空间利用率和电气性能。# c4 A5 |6 P. ?& \

, Q& K, v$ w6 N0 F8 o8 S; { ; m4 \# Q! A2 Q! V( e$ L+ T7 } ; m4 \# Q! A2 Q! V( e$ L+ T7 }

图11展示了嵌入基板内的平面电阻、电容和电感的实现方式及其基本结构。

; q: Y) l6 i( y+ r; S. i$ L! q2 c& } L; h8 m5 w) O) O

! ?1 K* D0 r3 K* ^( y 3 t4 Q' h$ h0 m& |: k 3 t4 Q' h$ h0 m& |: k

图12展示了平面电阻和电容的各种结构,展示了嵌入式无源组件的不同设计选项。8 d, p$ s0 t1 p3 _! g

8 w2 c x6 B( {2 O: l% f) L

集成技术总览和未来展望5 g( C5 s1 p' `1 e G

9 ]: v T ~4 l5 a6 z" g4 b图13提供了七种不同集成技术在定义坐标系中的关系概览。3 [: W% A! \* Y, W+ R3 T. H R

3 H! M! `" E, z3 M) O! L& ]5 T$ w ! `6 d# \0 \8 | B ! `6 d# \0 \8 | B

图14展示了SiP集成技术的总结,展示了现代电子系统中如何组合不同的方法。/ X5 G+ D" Y; B( U$ V. R

+ Z! L- X4 A2 g2 q) C: A

集成技术的选择取决于多个因素,包括所需功能、成本限制和性能要求。随着电子系统的不断发展,这些集成技术将在实现新一代器件和应用中发挥更加重要的作用。不同集成方法的组合使设计人员能够针对特定要求优化系统,同时保持未来修改和改进的灵活性。

) K% ]! _/ m: [

/ ], e0 ~* u) q6 h) e( Z. ^* O% K参考文献

/ v* }$ v; x* l' X2 T8 x5 t8 p[1] S. Li, "From 2D to 4D Integration," in MicroSystem Based on SiP Technology, S. Li, Ed. Beijing: Publishing House of Electronics Industry, 2022, ch. 4, pp. 89-115.- F6 p& r" i5 P: _& X, s; d/ `$ i

/ }( f; C: Y: e

END/ ^$ n0 A) L [$ d2 a1 U5 Z$ |4 S

3 F9 t J% s+ N8 a

5 S6 F3 v: `' c( v: A3 k! c- |软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。- O- R& n: K) @5 ^$ M3 h* v1 g3 H

点击左下角"阅读原文"马上申请6 ?6 \0 N+ d/ ~8 K# L/ j; T

( c6 l5 u, a# _

欢迎转载! u% l l9 X! r

$ E+ R* S/ l' c( X

转载请注明出处,请勿修改内容和删除作者信息!' `$ }) t# E' _4 A

6 ]+ f7 ^9 O3 \ s0 T: Q! `8 j A# @) u% N

+ v( R9 T6 h; x) g, r0 X; Z

+ J/ G5 E) B [! n2 J( R c) E# u6 @0 T5 q; j- U9 I

关注我们

) c% F& x4 }7 Q2 f8 Y5 f8 B

$ P# X6 F, S2 C' m6 @" x8 }1 U6 R& @( i" r

1 J. E1 q% E6 _2 e% D/ y# H |

1 d e) X8 Y4 s3 n

6 U% m! [5 x$ J L | , w: S. i7 D: V; ^% m1 X8 B& W

+ R7 P2 M- g$ ?0 O |

* \4 i3 `' q0 B- b! d* W5 A

, h z0 ~( W' T; l+ U2 S. I6 l' R4 e% Y/ L2 z; y; U" M7 t. ~5 l

( r+ ?3 b% |, a( K关于我们:

6 ?: N4 E2 b% W2 R9 j深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

- E8 f: [5 A% D4 D' n+ P: f3 S3 Y" c

http://www.latitudeda.com/

4 m+ B, w' ]1 _) J: M(点击上方名片关注我们,发现更多精彩内容) |