|

|

引言0 J1 v9 b) H C9 B5 E4 r) d1 {" Z

高性能计算(HPC)和人工智能(AI)领域因异构系统而发生了巨大变革,特别是那些集成了GPU的系统。随着工作负载越来越受内存限制,优化系统内部的通信延迟和带宽变得极为重要。NVIDIA Grace Hopper超级芯片(GH200)代表了紧密耦合异构系统的重大进步,提供了统一的地址空间和对系统所有主内存的透明细粒度访问。

1 F7 T. [- t& _

/ o, r" `2 c) B, j0 v本文将探讨Quad GH200节点的架构(这是瑞士国家超级计算中心Alps超级计算机的基本构建块),并提供有关如何优化这一尖端系统内存操作的见解[1]。

0 J. R8 \" u: g( v1 ~

etd2yxyhk1r640131845344.png

8 b3 P$ \- k" D

0 ~1 D# n7 P$ ^( F3 @4 Z9 j8 q7 i架构概述

0 c1 a4 c8 H, N. `3 p/ eQuad GH200节点由四个GH200超级芯片组成,每个超级芯片结合了一个Grace CPU和一个Hopper GPU。这些单元通过NVLink和缓存一致性互连全面互联。让我们来看看关键组件:

/ A; ^4 w6 w; L/ D7 B# p

dn4vw1s5zfv640131845445.png

( k u J. [2 l" Q/ h( }* H图1:Quad GH200节点的架构7 M6 {; Q7 f- S" N

/ O" X6 g& b+ P( ^2 L. L0 p* f如图1所示,每个GH200超级芯片具有以下特点:: \1 z; C1 W/ z3 w/ N% z, ^6 R

一个Grace CPU,有72个Arm Neoverse V2核心一个Hopper GPU,有132个流式多处理器(SMs)96GB的HBM3内存(4000 GB/s带宽)128GB的LPDDR5内存(500 GB/s带宽)

3 o; G1 }) ~- B9 A) o) V6 O) g: L4 k% z; a9 A% @

GH200单元通过以下方式互连:

, |5 V5 e$ @+ {$ q- N! y, a3 FNVLink:每个方向150 GB/s(总共900 GB/s)Grace互连:每个方向150 GB/sNVLink-C2C(C2C):每个方向450 GB/s(总共900 GB/s)) T4 U7 z" W& s2 h

0 _4 u% E$ i8 d+ Y# r" U- k每个节点还通过单独的网络接口卡连接到Slingshot网络,每个方向提供25 GB/s(总共200 GB/s)的节点间通信。

5 a1 j" ]; o+ D* c- K, `

8 d% ?" m/ H1 W: ?- E内存层次结构和NUMA

, V8 H2 U( n. d ~+ i2 qQuad GH200系统呈现出复杂的内存层次结构,具有非统一内存访问(NUMA)特性。

# A0 \6 Z& v& j, V. z/ I每个GH200由两个NUMA节点组成:与Grace亲和的LPDDR5内存与Hopper亲和的HBM3内存

" Q% N' {3 w& [: F3 T' k1 R[/ol]

3 p7 s( `' D( \+ L0 [总的来说,一个Quad GH200节点有八个NUMA节点,四个与Grace CPU相关(NUMA 0-3),四个与Hopper GPU相关(NUMA 4, 12, 20, 28)。

8 T7 P) i5 A. _7 {$ |: ~7 g

$ g+ ^- h6 o# o# L$ I, P. |理解数据路径8 B! m- b" X/ S" a* N$ R

为了优化内存操作,理解不同类型操作的数据路径非常重要。让我们来看看读取、写入和复制操作:

9 ~7 T9 W" ^% V3 b+ t. `1 f

lbyf5202vbv640131845545.png

1 ?( j3 |8 `. b; e: p图2:Hopper操作的数据路径! ]+ ]/ i0 j+ j* u

: O6 @4 C4 W+ V8 A) c# y6 J图2说明了Hopper GPU执行的读取、写入和复制操作的数据路径。

/ Y3 e; s1 A( z4 K注意:" K3 p, r) y" F k

本地HBM访问具有最短的路径和最高的带宽(4000 GB/s)跨C2C互连的操作限制在450 GB/s复制操作可能需要多次互连遍历,影响可达到的带宽, s, B3 ~) {# N: o/ T

3 P" }+ [5 \1 x; R3 O. _内存操作基准测试& g+ f& u m) U! T' e5 b, w

为了理解Quad GH200系统的性能特征,我们将检查各种微基准测试的结果:

( [$ B( w" U }& P% W8 Y$ l1. 读取和写入操作:

1 W0 F" E& }' b; R8 e+ v

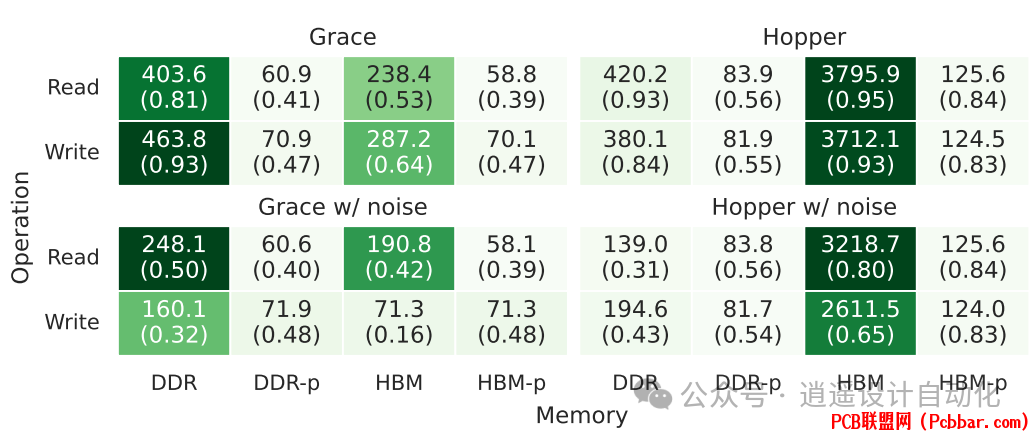

zn3tj0za4tf640131845646.png

5 z. v0 J5 Q0 w图3:读取和写入吞吐量 e9 H8 G* S: o! h) D: s9 h" Y% r

7 y+ F. \& q5 ?. @0 O

图3显示了Grace和Hopper在不同类型内存上进行读取和写入操作的吞吐量,包括空闲条件下和C2C互连负载下的情况。. L5 C( k3 Q4 q8 w- z

主要观察:

# f' D! W/ X. X3 uHopper通常在本地内存访问时更好地利用C2C互连跨越C2C和NVLink的操作会产生显著开销在负载下,对HBM的写入受影响最大,特别是对Grace而言

# M. {! ^) @/ v7 E

' P- l9 d( M7 P& F! O% B2. 复制操作:

( S6 I/ I/ p. f( D4 f1 C

lhmh55x401p640131845746.png

$ @( e; g+ @. [. W' A9 `. u0 L* [图4:复制吞吐量8 K" u! L6 p5 O6 n+ Y# l; M

1 g3 Z% s$ _% z& B" N$ A( ]3 }

图4说明了Grace和Hopper在不同源和目标内存类型之间进行复制操作的吞吐量。

: e: l$ e& ?0 x( C2 v1 ]8 E7 o) c值得注意的发现:

: C5 i& k: S. o# m/ I8 T内存传输存在不对称性(例如,Grace在从本地内存复制到对等GH200时达到更高的吞吐量)Hopper在跨越多个互连时通常能更有效地利用可用带宽

9 ~; k$ W! r; Z% k9 ]) d0 {9 W& C- |1 C2 C

3. 延迟:

9 d- g8 K: e7 i U: d) o3 h3 h

2bha1dosrmk640131845846.png

, y% ]9 E/ P4 b; `( C' F( v1 [

, y% ]9 E/ P4 b; `( C' F( v1 [

图5:主内存访问延迟! p6 x, w, j2 C! @0 W

9 @0 C! [3 T! n3 j% s9 w. r) @3 D

图5显示了Grace和Hopper的主内存访问延迟。有趣的是,跨越C2C互连的访问(Grace到HBM和Hopper到DDR)表现出相似的延迟。

. F4 c8 s- e5 n" A" V9 G' I8 b# v4 C! T* ~7 Y# A' G- C, ^

优化应用程序

) O- X, J K# _' O9 X理解这些性能特征对于在Quad GH200系统上优化应用程序非常重要。让我们来看一些示例工作负载及其基于内存放置的性能:

& ]' v5 y2 i: S6 M1 s. i6 ?2 i: j, V1. GEMM(通用矩阵乘法):

( x. B5 ~1 g5 w$ g

xwra2nee20t640131845946.png

* ]' d9 a/ Z0 c$ Z, {) N0 h: C: r

* ]' d9 a/ Z0 c$ Z, {) N0 h: C: r

图6:GEMM性能2 [ ~4 x& q7 h: p

; D6 B$ f0 P5 w

图6显示了矩阵放置在不同内存位置的GEMM操作性能。主要要点:

! j: s+ j3 d" XHBM放置对于最佳性能至关重要,特别是对于使用Tensor Cores的数据类型即使将一个矩阵移出HBM也可能显著影响性能

# _, I5 o! I. Y. ?9 v) h# e1 \! v5 E' ^- M5 U

2. LLM(大型语言模型)推理:2 T+ p o, R$ c- O# B

20014rdhvzh640131846046.png

$ s3 R+ e w1 Z$ y- b

$ s3 R+ e w1 Z$ y- b

图7:LLM推理时间" N, W8 o9 I8 P7 t0 M# K. h8 [

# d" f7 S# Y9 }: a/ X$ c

图7显示了不同模型和内存分配的LLM推理时间。观察结果:5 b+ B( Z r7 V$ l4 Q# K

内存访问速度对吞吐量起着根本作用HBM分配提供最佳性能,而对等内存访问显著影响推理时间

+ C/ ?2 j) G: u7 B# c

" r8 Z; y+ A- `% y0 c" u* c6 r3. NCCL(NVIDIA集体通信库)操作:" S, W6 _+ Z& e! n

wtcar1tazwv640131846146.png

* A. a* ]3 |* m6 {0 \$ x

* A. a* ]3 |* m6 {0 \$ x

图8:NCCL All Reduce和All Gather性能( t+ G' @' L( ]

# O2 W% A, a) J+ P; j# h- z0 k" g图8说明了节点内All Reduce和All Gather操作的性能。关键点:

* b e1 ?* x5 j" P- j超级芯片局部性比使用的内存类型更重要同一GH200内存大大优于对等访问* ^+ I P4 k* `" q/ F: v" W

* D: T; k% b& f% W5 e最佳实践和建议3 C% Y5 w3 C$ u2 F2 m7 v- s

基于从这些基准测试和应用程序示例中获得的见解,以下是在Quad GH200系统上优化内存操作的一些最佳实践:优先使用HBM:尽可能将性能关键数据放在本地HBM内存中,特别是对于GPU密集型工作负载。最小化跨GH200访问:尽量将数据保持在执行计算的GH200单元本地,因为对等内存访问会导致显著的性能损失。谨慎利用统一内存:虽然统一内存简化了编程,但要注意与显式内存管理相比的性能特征。考虑内存传输的不对称性:在设计数据移动模式时,要考虑不同内存类型之间复制操作的不对称性。优化集体操作:对于使用NCCL或类似库的应用程序,专注于超级芯片局部性以最大化性能。分析和迭代:使用分析工具识别应用程序中的内存访问模式,并根据系统的性能特征迭代优化数据放置。

! s! L) m; |" B0 r[/ol]. L9 _1 p P) j/ P. C/ N

结论 r; W2 h+ D& d

Quad GH200节点为HPC和AI工作负载提供了强大的计算能力和内存带宽。然而,要充分利用其潜力,开发人员必须理解其复杂的内存层次结构并相应地优化数据放置。通过遵循本文概述的最佳实践并仔细考虑不同内存操作的性能特征,可以显著提高在这一先进异构系统上应用程序的效率。

3 W+ @9 w0 v( r9 G- ~1 R# D# p# W6 p+ C' p; d. ~$ l4 [

参考文献

+ e/ i1 e0 m9 g% C( m. v6 A9 X/ n[1] L. Fusco et al., "Understanding Data Movement in Tightly Coupled Heterogeneous Systems: A Case Study with the Grace Hopper Superchip," arXiv preprint arXiv:2408.11556v2, Aug. 2024.( X! _+ X+ P" i7 j4 T _

7 p, J M. L; y' |- W+ \END# V, e4 N% P1 i9 J

7 C" @% \: z/ F2 b* P6 v

0 N3 M1 V3 K' B* ?6 v7 @7 I软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。

|2 O' x1 g& L4 T7 T. D0 v点击左下角"阅读原文"马上申请

. P! f$ n1 X% {+ b

3 d; i3 O6 C* u0 y欢迎转载

- S, s% Y5 K& J8 Z/ k v( j

# b. e, y N0 b3 }) ^ t% k转载请注明出处,请勿修改内容和删除作者信息!5 ]$ n& v6 P$ e

! Q: M3 P% k' i4 S, u* y# o: D5 I- Q2 `5 R- `0 B! ?

8 h( J- X8 a; Y2 q$ v; j

dwno3zivgzi640131846246.gif

, ~ I- m( s6 x: R( q. [0 O, H `5 t% T% l* b

关注我们5 t. W3 {& _9 d0 E8 l

5 J2 L9 y3 y( L6 M; Q5 Z

- R: |/ r0 d. u

4rylqec5bdo640131846346.png

6 i: R- q# r2 U0 n: q( H8 A1 }

6 i: R- q# r2 U0 n: q( H8 A1 }

| ( X3 D" Z& s: C) b0 W

dmhmyzw3c0v640131846446.png

+ f7 A |2 U2 a8 k

+ f7 A |2 U2 a8 k

| " b6 i/ ?& }- G+ K# P

vjb0ch5fihn640131846546.png

) M; A) s! S$ W0 k6 a* J+ N |

. j" c& s+ Z4 g1 F% w' t

; A9 d# G4 W( o+ C; z2 g& R0 w. L' Q2 a

% {- x0 R; v( h9 o+ [# q关于我们:8 S* J ?) o4 n

深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

, ], k) A; G Y0 s( K% z

5 D& @0 @7 r" q9 H1 ]( Thttp://www.latitudeda.com/! j1 p w- Q% S5 t

(点击上方名片关注我们,发现更多精彩内容) |

|