|

k5fch0sd1r36403774049.gif

( X6 v- E. Q$ j; U) x& k7 m( V点击上方名片关注了解更多

; A& d4 C1 ?& p/ c( o9 ?3 W0 z% H( J- C I d! C! Y

3 ~' M, K* [+ F

锁相环路,简称PLL,作用:可以锁定相位,可以消除频率误差。

1 ?+ J5 a3 J# y% ~- n2 a) o& ~1、锁相环路基本组成' j. O$ I* ]/ y, t1 Y

1t5de3nxhqc6403774149.png

9 n+ I, L) a- f+ ^ V2 U

9 n+ I, L) a- f+ ^ V2 U

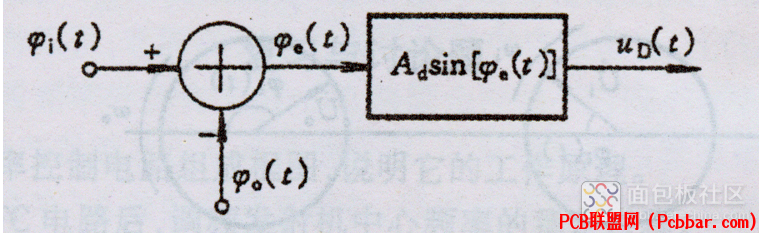

鉴相器(PD):用以比较ui、uo相位,输出反映相位误差的电压uD(t)。, H5 I6 S- Y2 d4 V, K7 M2 e

环路滤波器(LF):用以滤除误差信号中的高频分量和噪声,提高系统稳定性。

$ j2 ]" v; R7 m, D: T压控振荡器(VCO):在uC(t)控制下输出相应频率 fo。

0 b0 M ^* c+ ^1 Z2 Y3 l7 L0 Q若两正弦信号频率相等,则二者之相位差恒定;反之,只要保持其相位差恒定,即可使两信号频率相等。

7 \/ O, U$ {) M# i

smyquoj0gpa6403774249.png

: Y. ~4 v1 Q3 j; ] |

: Y. ~4 v1 Q3 j; ] |

锁相环路的基本工作原理: x6 b/ d5 M/ ?9 Y- D

若wi ≠wo,则ui(t)和uo(t)之间产生相位变化 → uD(t) ,与瞬时误差相位成正比→uc(t),滤除了高频分量和噪声→ wo ,去接近wi ;最终使 wi = wo ,相位误差为常数,环路锁定,这时的相位误差称为剩余相位误差或稳态相位误差。

8 Y7 J; f; j6 K4 m; \8 N2、锁相环路的数学模型

4 q% _! g( w' o" r鉴相器的相位模型:

/ e% \; `1 S! {2 M. ^1 ?

wa5tfbet0x26403774349.png

+ Q9 S5 p6 h" _, R1 G7 f! p! }

+ Q9 S5 p6 h" _, R1 G7 f! p! }

模型为:

( V, D6 ?/ o& M

1cf4355clpz6403774449.png

8 @# |% `, v/ e

8 @# |% `, v/ e

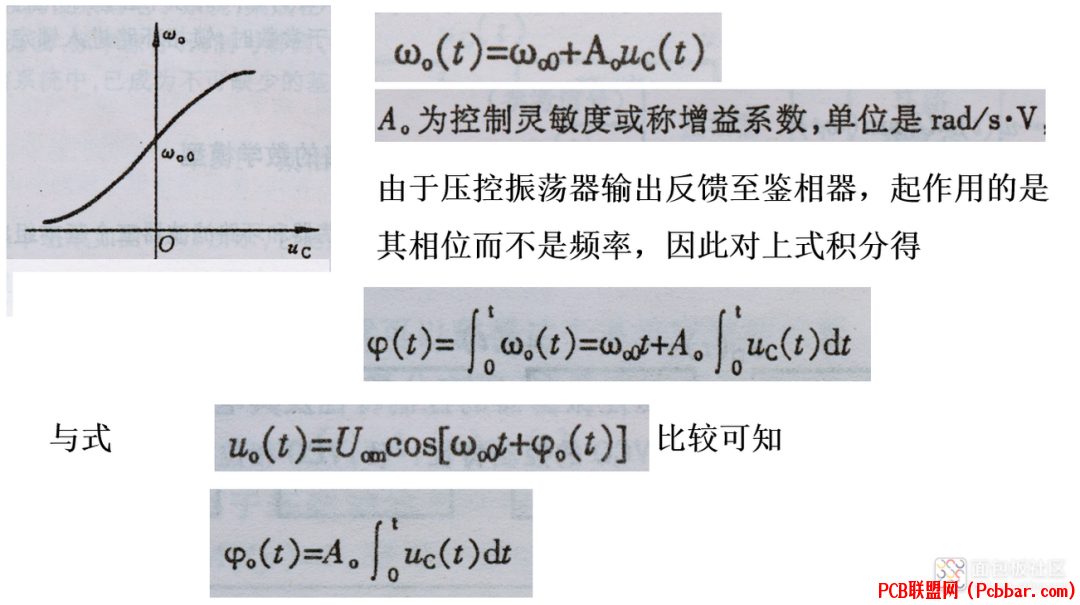

压控振荡器的相位模型:: U0 G2 D2 F @" @; w V

0qlmbagcmcp6403774549.png

/ i' v( x3 ~# A5 |$ [7 j

/ i' v( x3 ~# A5 |$ [7 j

yjjzedwhked6403774649.png

1 S. Z% G Z% K, Z3 K

1 S. Z% G Z% K, Z3 K

模型为:

9 M1 C# y" c3 k% e1 ]8 T0 ]

qiwzopse3w06403774750.png

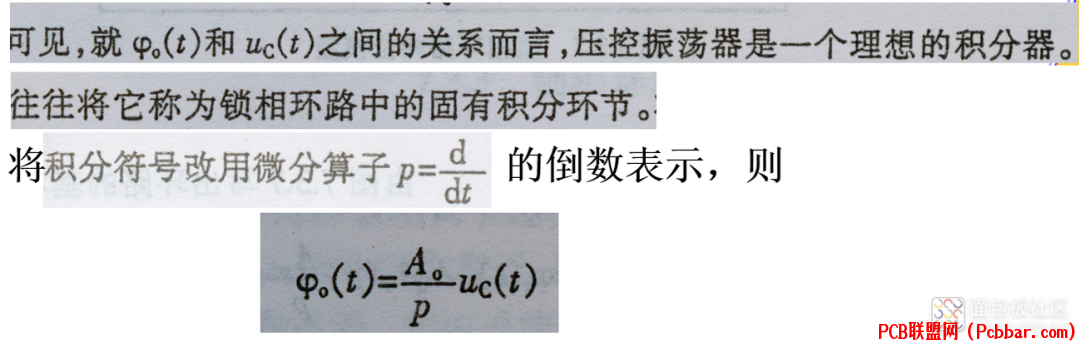

; g7 S0 U7 k: Z8 e: J8 i# C环路滤波器的电路模型:6 }- [ v+ h2 K+ |8 l" ^/ d+ J

nsnyfri5umg6403774850.png

( d2 K* V4 Z8 Q: t! L模型为:! m4 N$ W; v4 V% _$ B) Z- j5 J

tvqsrtvvytw6403774950.png

$ V0 ~' h) Y7 u6 hPLL的相位模型和基本方程:: t" Y( W( D7 Z; Z1 t% ?! o' D

p3k4crms0kt6403775050.png

7 U; @0 l! @0 N% b$ }' c上式是一个非线性微分方程,它完整地描述了环路的控制过程。+ [6 c P- d, n

yr3hmatiuyt6403775150.png

8 O# r- n, p4 h8 B. g

lyaydfuirwn6403775251.png

/ f5 C% e1 F3 w c. D) |& K锁相环路(PLL)是一个传递相位的闭环系统,只要研究它的相位数学模型或它的微分方程,即可获得该系统的完整性能。

- z' d+ a8 f' l. m# ]; G) D8 g+ W

rw11ajtlufb6403775351.png

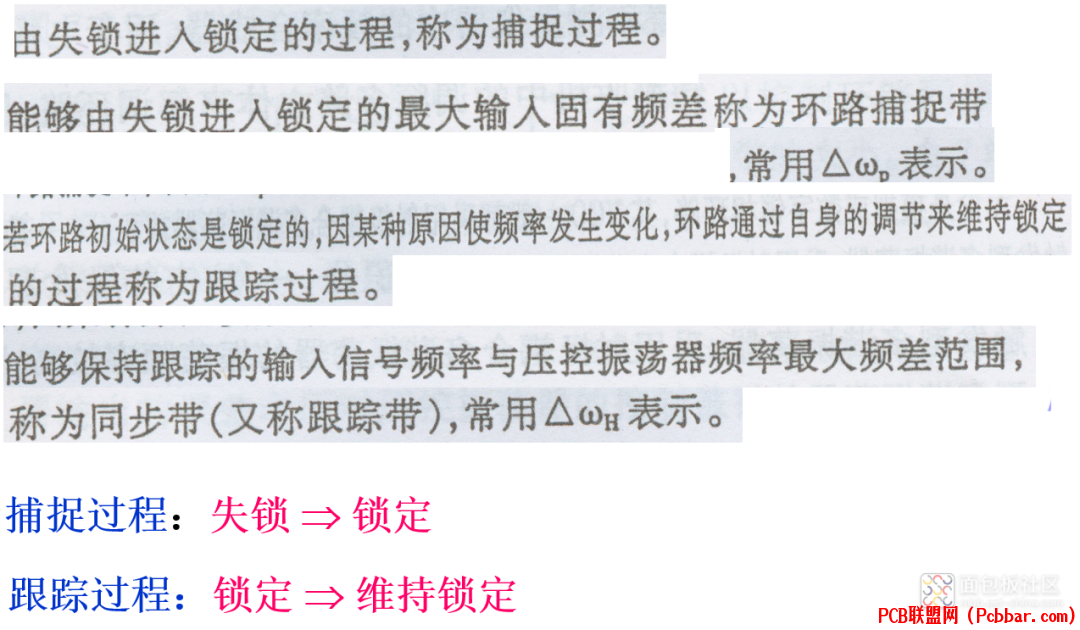

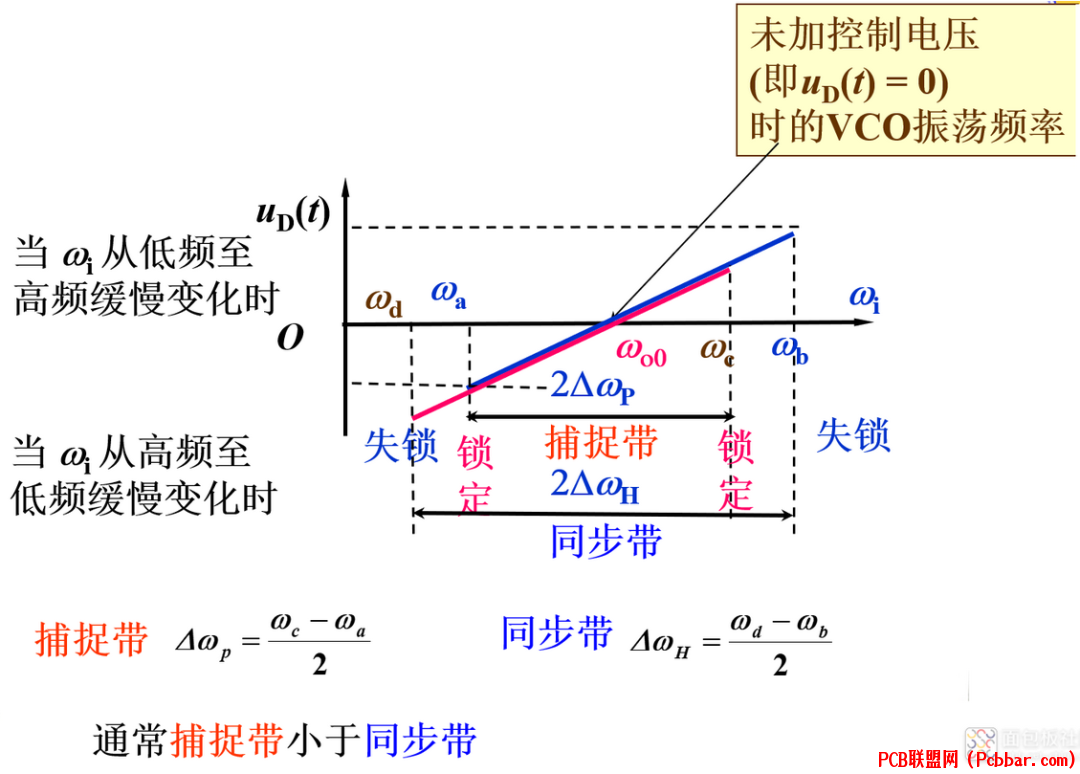

' X' Q' ^! A( T& |# N/ a! G+ p3、锁相环路的捕捉与跟踪

1 q! l/ Y, Z$ j5 n

kk2eaiogalu6403775451.png

5 F( u( V- N& E: N

5 F( u( V- N& E: N

q33fp3zahqr6403775551.png

; ^ H" [9 X! u& ~+ M1 n/ F

; ^ H" [9 X! u& ~+ M1 n/ F

4、 集成锁相环路+ m9 h9 E* C+ W2 o, c

通用型单片集成锁相环路L562简介:9 }% W2 O/ C& _1 I

为多功能单片集成PLL。内部除有PD、VCO外,还有三个放大器和一个限幅器。工作频率可达30MHz。

I2 u5 a1 l6 P鉴相器(PD)采用双差分对模拟相乘器电路,压控振荡器(VCO)采用射极耦合多谐振荡器电路。限幅器用于限制锁相环路的直流增益,以控制环路同步带的大小。

6 z4 w$ m' L4 Y3 u# _* P V只需单电源供电,一般采用18V电源,最大电流14mA。输入信号电压最大值为3V。

6 a' s+ z: i+ W/ o2 R: `& x" T9 j9 Y0 tL562内部结构与外引脚排列:

T/ `# ~6 f! V4 U9 q7 H9 m

dknbicyyfio6403775651.png

* l, |3 v0 H6 C7 t; \* }7 BL562内部的射极耦合多谐VCO:

0 s# R# S& b9 d

hherdhsbub06403775751.png

1 A4 z! ]5 t: U! h% |; h

1 A4 z! ]5 t: U! h% |; h

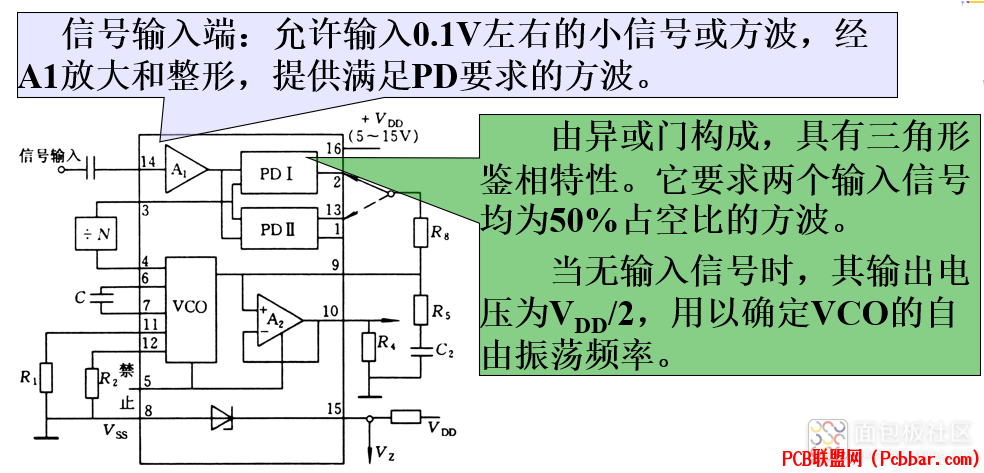

CMOS锁相环路CD4046简介:为数字PLL。内有两个PD、VCO、缓冲放大器、输入信号放大与整形电路、内部稳压器等。具有电源电压范围宽(5~15V)、功耗低、输入阻抗高 等优点。工作频率0~1MHz。内部VCO产生50%占空比的方波。输出电平可与TTL电平或CMOS电平兼容。

; L5 b0 R2 \) X

d4ta21m4twq6403775851.png

5 m4 S! B* o1 I! p4 H3 S8 _

5 m4 S! B* o1 I! p4 H3 S8 _

qjyecchwcac6403775952.png

7 y, H5 C3 |# f2 S# e0 C& w) V ! b/ G. f' w# Z; o ! b/ G. f' w# Z; o

4 B$ J: U& y* Q5 W7 @$ L) o0 T$ a

: o( U. y7 R9 R

& F, ]3 M% J/ q0 C. Q3 n0 M; P2 p声明:) r8 O' M( ~" E

声明:文章来源:面包板社区czd886分享。本号对所有原创、转载文章的陈述与观点均保持中立,推送文章仅供读者学习和交流。文章、图片等版权归原作者享有,如有侵权,联系删除。投稿/招聘/推广/宣传 请加微信:woniu26a推荐阅读▼* f+ T K8 N& z G8 q" v& L

电路设计-电路分析

% T( Q7 ]3 |- l2 d I" R0 gemc相关文章4 Q2 W% B/ r+ }5 `. d2 V( R J

电子元器件

9 i, T6 G0 [0 b后台回复“加群”,管理员拉你加入同行技术交流群。 |