|

|

|

rvspac22tbj640193858.gif

6 e: I% |) `6 v( e( m" S, E4 e* Z! t

6 e: I% |) `6 v( e( m" S, E4 e* Z! t

点击上方名片关注了解更多" f; i; y+ M# x+ m0 O2 l

( z' `; q% \ Z

+ a% D) o9 {- F" _, `4 k: E- G4 m

什么是S485?+ g) _/ ~+ p# u" D

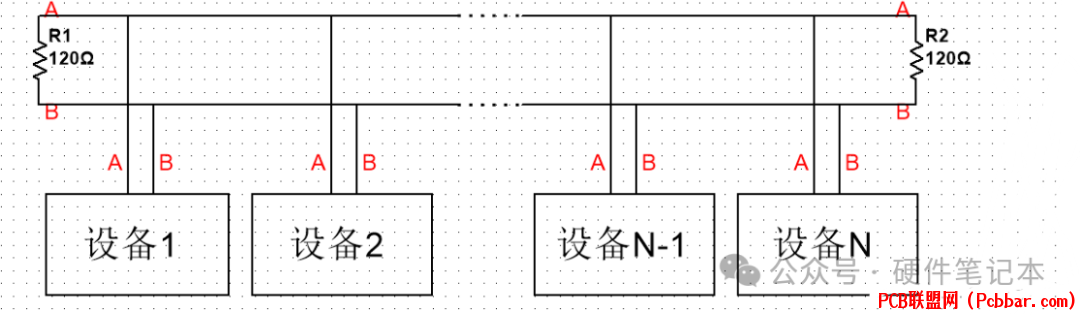

- n0 Z( H5 a" {9 W5 S9 J3 `! WRS485是半双工通信,半双工通信指的是通道在一个时刻只能处于接收或者是发送。RS485的特点是支持多节点传输、传输距离远、抗干扰能力强,RS485可以连接多个485设备,信号的速率可达到10Mbps。通过AB两线之间的压差来判断是逻辑电平1或者逻辑电平0,当AB间的电压差大于200mV时为高电平1,小于200mV时为逻辑电平0。一般会在首末两端接120Ω电阻,其作用是进行阻抗匹配,消除信号反射。4 `$ S) R. I1 b$ ]* G

jf5chckrkc0640193958.png

8 o* z& q, z5 @# q, N7 d

8 o* z& q, z5 @# q, N7 d

# A$ a) C3 A$ ~* X" t0 H$ fRS485硬件电路设计

! C* ~) f+ _, c2 \1 M* K9 p+ R. M

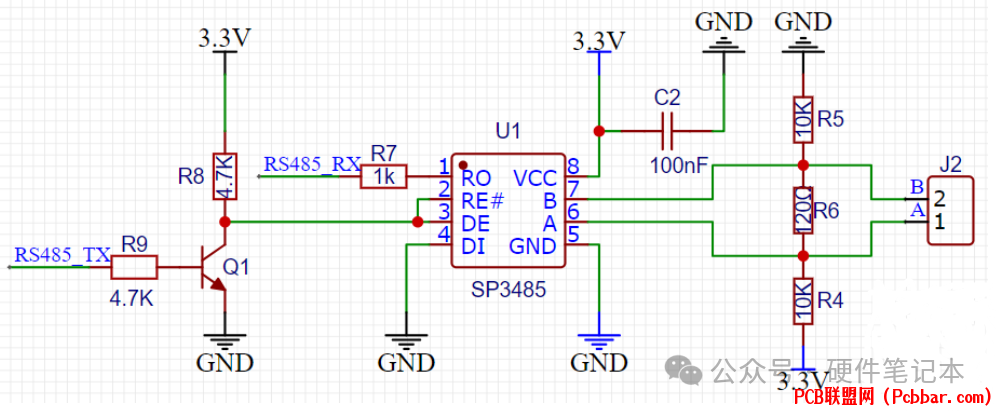

RS485电路设计可以分为隔离型和非隔离型,下图是非隔离型电路,B端接到GND下拉,A端通过上拉电阻为高电平,是为了保证A和B之间的压差大于200mV。DE和RE引脚是发送和接收使能,RE为低时,为接收使能;DE为高时,是发送使能。应用中一般是两者连接在一起,通过IO口(RS485_EN)控制,因为芯片要么是处于接收,要么处于发送,因此在发送数据前,给RS485_EN信号为高电平,接收数据就给低电平。

( E+ N, X4 x% s, x, {8 ?. w+ T* B( Y

t51tzkaqvfy640194058.png

* j/ P$ g2 u. O) H7 H

* j/ P$ g2 u. O) H7 H

RS485自动收发电路硬件设计& R! a4 @6 y' }4 N# \ C* [" R

; p1 F3 Z7 d l! ]9 P' Y) Y8 \+ Z5 {( v

自动收发电路相比较普通的485电路,区别在于多一个晶体管控制485的使能引脚。R9限流电阻一般是4.7K,R8上拉电阻一般也是4.7K,使能引脚在晶体管没有导通时被上拉。# H' ~% X/ I: ]

rkit3wsqqb4640194158.png

9 ?! E" {8 c0 Y! a: d

* u5 t9 z* B" v4 a/ Y2 N接收数据时:接收数据引脚是芯片的第一引脚也就是网络标签RS485_RX,在接收数据过程中,RS485_TX引脚保持高电平,VGS为高电平,NPN三极管Q1就导通,RE和DE相连的引脚通过晶体管下拉到GND,此时接收使能,处于接收状态。

0 k- d3 D& N( Z8 M9 B+ `6 F3 f+ Y. Q

发送数据时:发送数据引脚是RS485_TX,应该RS485_TX发送1,晶体管导通,RE和DE的电平为低,RS485收发芯片没有打开,由于常态下485为高电平,此时数据就是高;当 RS485_TX发送0时,晶体管不导通,此时485收发芯片的发送使能为高,DI由于一直被下拉到GND,所以发出去的数据为0。这样就实现了485的自动收发。

# o$ h, Y% s, b R# |: K+ x. J: a/ S) L1 P) l" R

发送具体解析:

9 v; o$ m8 t. [6 Q# n5 QRS485_TX 发送1,VGS高电平,NPN三极管导通,使能引脚是低电平,发送失效,接收使能,处于接收状态。由于SP3485芯片的AB引脚是高阻状态,R4把A拉高,R5把B拉低,所以AB传输的是1。即RS485_TX发送1时,AB引脚发送1。8 b! t9 j/ b9 ^8 o" A) T# U

5 p7 Q5 ]+ R' ~

RS485接口防雷电路设计( i/ G5 v$ J7 S$ U! `

- e& e' _$ j, _% V" p% u

a1c5ivvt01g640194258.png

9 {; z7 c2 w& g# Y接口防护电路

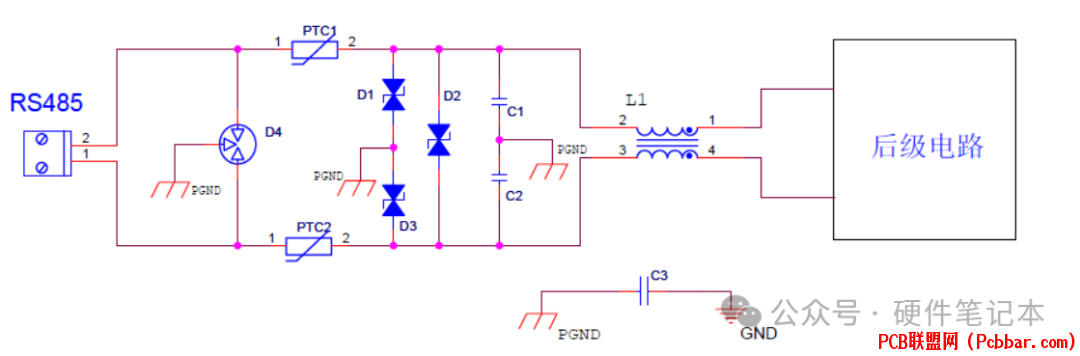

* K4 W' M/ c4 ]) @L1是共模电感,共模电感衰减共模噪声,增强抗干扰能力,一般选择120Ω/100MHz。C3电容的作用是为了隔开接口地和数字地,一般选择1000pF。为了达到emc防护要求,差模信号2kV,共模信号6kV,在接口处会预留上气体放电管、热敏电阻、TVS管组成防护电路。

8 t) o# u& [5 u

" p4 q+ b5 p, u! l+ N+ yRS485接口电路PCB的GND设计

. ~; Q7 j% j3 c2 d. @7 z& x# v6 d7 K c1 \, P

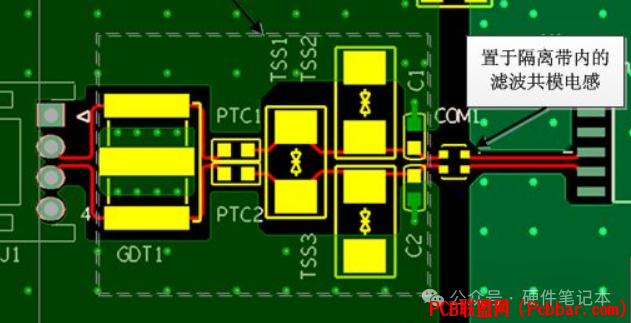

虚线处的防护器件要尽量靠近接口,摆放紧凑整齐,先放防护器件再放滤波器件。

8 { y! K$ b; X, G1 m: \4 Y

jauheujhom4640194359.png

2 E5 X- @" c# A. Z

2 E5 X- @" c# A. Z

RS485接口电路设计通常涉及到几个关键要素,包括信号传输、电气隔离、噪声抑制、保护措施以及电源和控制逻辑设计等。

9 x8 c4 B4 Z" x) J, t1 t) a# [3 t6 k- B5 h y' K" w) b. n

关键要素; z6 X7 |( t9 Y4 n9 y6 q

6 u M1 w; J/ W

信号线选择与布线? 使用一对双绞线作为差分信号线(A和B),通常选用屏蔽双绞线电缆以减少电磁干扰。? 保持A和B线长度尽可能相等,以减少信号延迟差异,保证信号的完整性。共模电感和滤波? 在信号线入口处加入共模电感L1,用于抑制共模干扰,推荐阻抗范围为120Ω/100MHz ~ 2200Ω/100MHz。? 可能还需要并联去耦电容和TVS管等元件,进一步提高抗干扰能力。收发器芯片选择? 常见的收发器芯片有SP3485、MAX485等,它们将TTL/CMOS逻辑电平转换为RS485差分信号。? 需要关注RE、DE以及RO等控制引脚的连接逻辑,通常RE和DE可以连接在一起通过单个控制信号控制发送/接收模式。偏置和终端电阻? A信号线可能需要上拉电阻(如10kΩ至4.7kΩ),以确保在空闲时的电压状态,B信号线可能需要下拉到GND。? 在总线的两端或适当位置放置120Ω终端电阻,以减少信号反射和改善信号质量。防雷击和浪涌保护? 可以在信号线上添加TVS管和/或自恢复保险丝,用于过压和浪涌保护,提高电路的鲁棒性。? 对于高风险环境,考虑加入6kV以上的防雷击保护电路设计。EMC设计? 保证良好的接地设计,特别是接口地的处理,有时单板地与外壳直接连接,通过1000pF电容耦合。? 电路板布局时注意电源和信号线的分离,减少交叉干扰,增加滤波和退耦电容。控制逻辑? 根据应用需求,设计控制逻辑电路或使用MCU控制发送使能信号,实现自动或手动切换。? 对于自动收发电路设计,可能需要更复杂的逻辑来自动管理发送和接收状态,以适应不同通信场景。

- }5 Z: V4 {. ~$ }) ], zRS485接口设计不仅关注电气特性,还需要综合考虑EMC、可靠性、安全性等因素,确保在复杂工业环境中的稳定通信。

3 I8 d4 N8 S# W- Y; c' N6 l

m54lw3dccxs640194459.jpg

& |8 F: t+ R7 _6 d# \+ B

& |8 F: t+ R7 _6 d# \+ B

vny42uey0xo640194559.jpg

9 g2 O( H: ~# [1 d H

9 g2 O( H: ~# [1 d H

声明:

2 c1 p. p4 O* @6 r# ]+ L声明:文章来源网络。本号对所有原创、转载文章的陈述与观点均保持中立,推送文章仅供读者学习和交流。文章、图片等版权归原作者享有,如有侵权,联系删除。投稿/招聘/推广/宣传 请加微信:woniu26a推荐阅读▼

8 a4 {/ K4 p" l. C电路设计-电路分析

. F- w9 u: p! T* a/ zEMC相关文章

* X' c" Q( w' |& f7 g. h7 J* D电子元器件

. H) W- l m: m. U1 @ O1 F! l; ~后台回复“加群”,管理员拉你加入同行技术交流群。 |

|