|

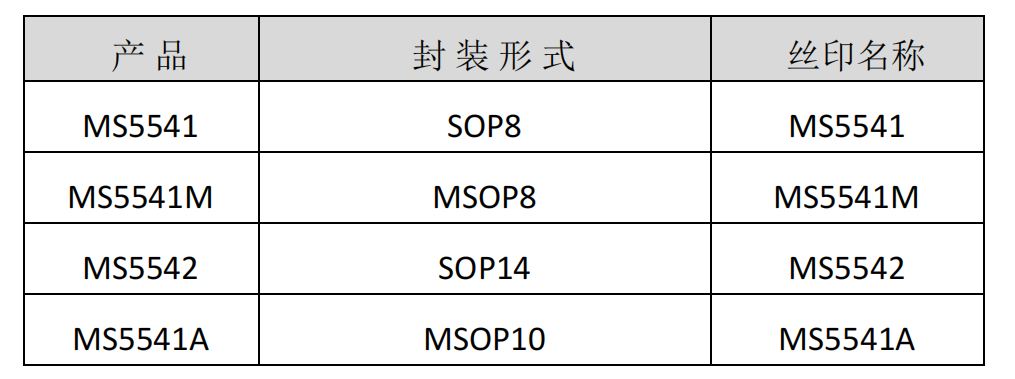

MS5541描述 MS5541/MS5542 是一款单通道、16 位、串行输入、电压输出的数模转换器,采用 2.7V 至 5.5V 单电源供电,输出范围为 0V至 VREF。在输出范围内保证单调性,在温度范围为-40℃至+85℃能够提供 1LSB INL 的 14 位精度。MS5541/MS5542 提供无缓冲输出,低建立时间、低功耗和低失调误差等特性。并且具有低噪声性能和低毛刺,适合多种终端系统使用。 MS5542 能够工作在双极性模式,产生VREF 的输出摆幅。具有用于基准电压与模拟接地引脚的开尔文检测连接,以减少布局敏感度。 特点 有效精度 14 位 3V 和 5V 单电源 低功耗:0.825mW 建立时间:1.2us 无缓冲电压输出能够直接驱动 60 K负载 低毛刺:1.1nV-s 兼容 SPI/QSPI/MICROWIRE 和 DSP 接口标准 应用 精密源测量仪器 自动测试设备 数据采集系统 工艺过程控制 MS5541替代方案 MS5541 pin=pin AD5541 封装以及功能完全替代AD5541,MS5541价格稳定交期很好,提供原厂研发现场技术支持,为客户解决替代方案。 封装图  7 Q/ s2 y7 J1 B- }5 r2 q1 q: t 7 Q/ s2 y7 J1 B- }5 r2 q1 q: t

$ p( A# C5 ?( A

; w, k8 v$ |8 ~7 W" E% X3 D& j& W' Q3 h9 s7 z" [1 G2 W

1 Y& m l/ |' g5 W6 @2 Q

% t. [3 _2 \8 I1 j# |! k: Q" A M

+ F4 T) z; ~" @1 e# w; B9 V8 W' Y4 q5 i f( M, W0 e! [% ]

产品规格

. h; z, ~/ c# L5 n

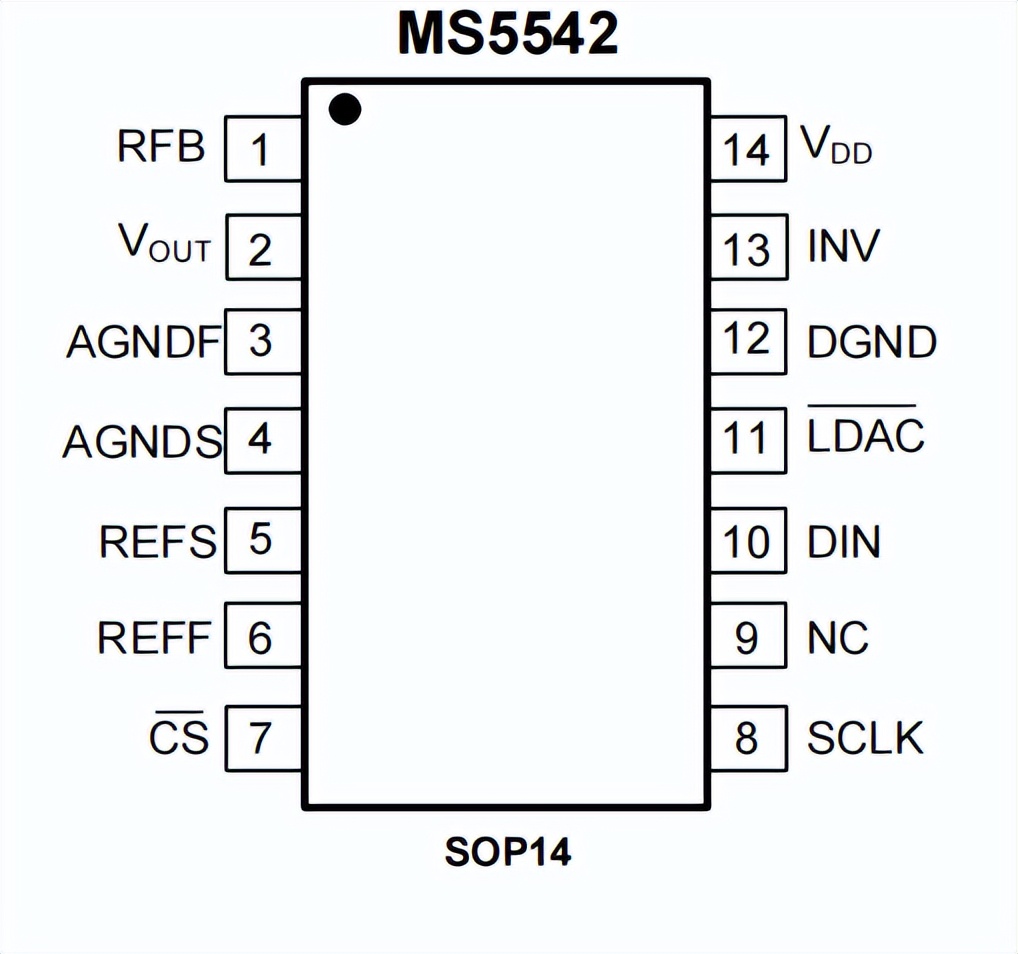

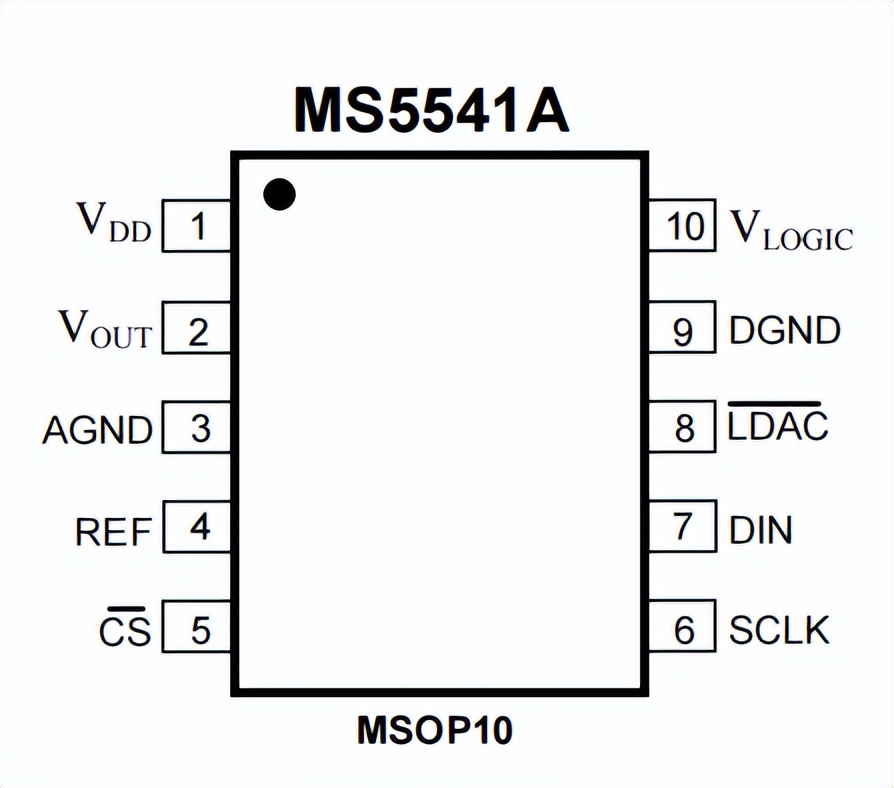

1 J& [' V, w3 c管脚排列

5 o; S: Y9 L) [- n" | / W0 k0 ^1 Z8 L / W0 k0 ^1 Z8 L

7 a: Q; F- y# B

; p1 i4 y! c$ F! u* H8 e! D

$ f6 n& f. t' W9 x ! d0 R( X: d5 n% Z5 ] ! d0 R( X: d5 n% Z5 ]

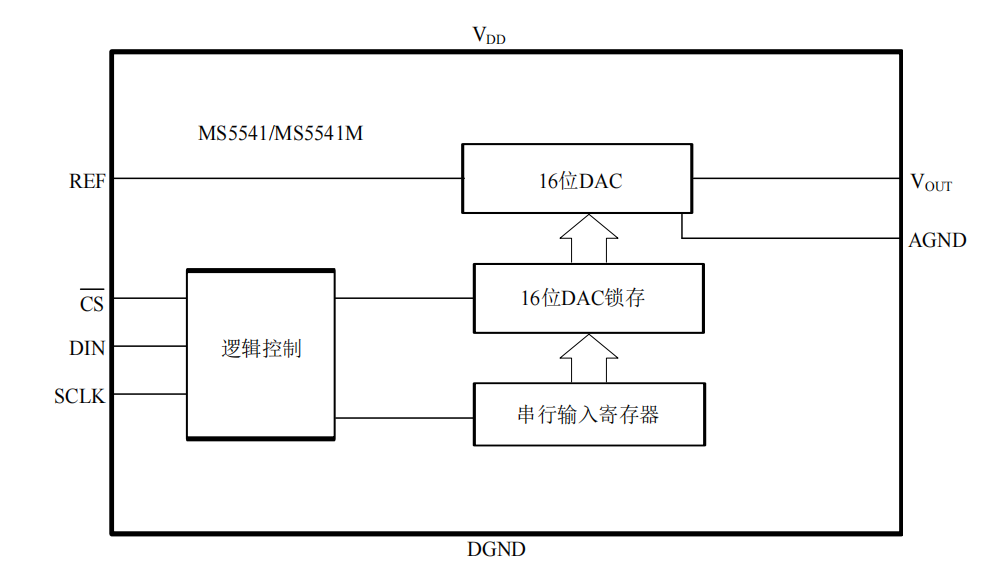

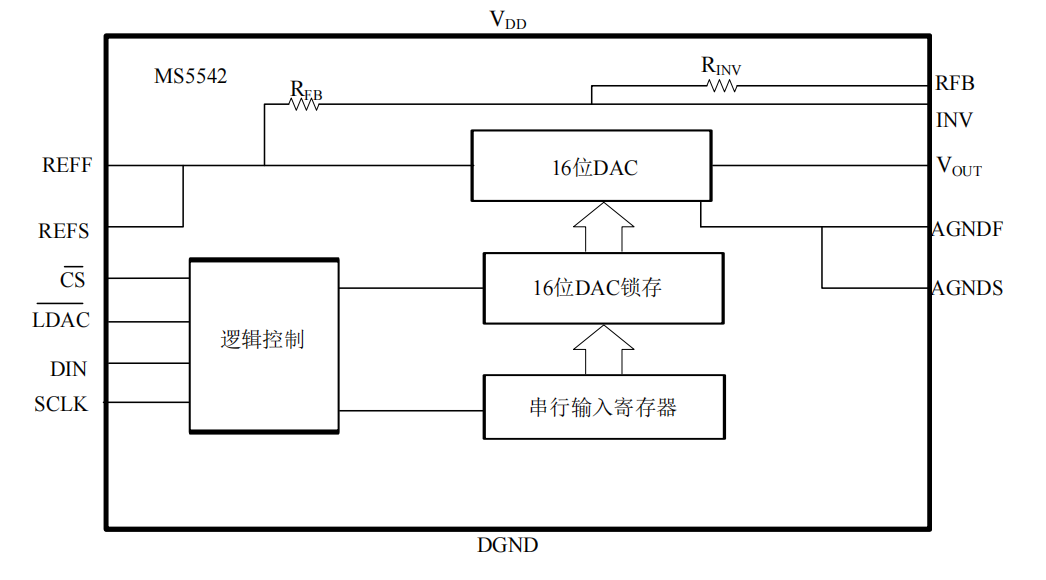

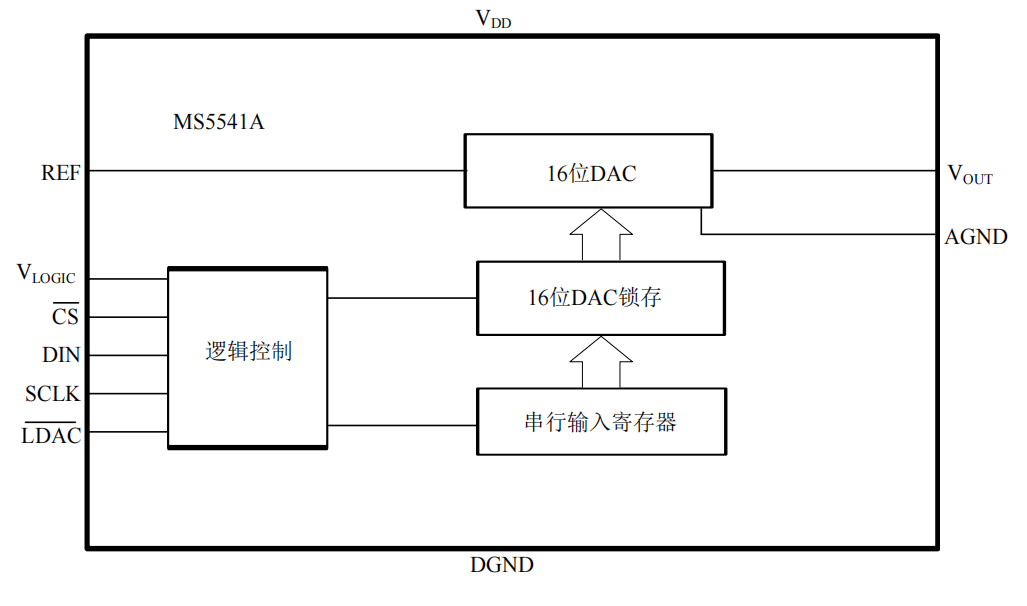

6 c* v* b9 N' s# C( X3 z内部框图  5 R7 S6 m7 j7 k2 Q( _ 5 R7 S6 m7 j7 k2 Q( _

, H. A1 y* O4 D7 N ?

r% g0 d8 z# s) |- z1 M% F4 c7 V r% g0 d8 z# s) |- z1 M% F4 c7 V

# _( J( R" y0 ^& {

9 b$ e6 t; t8 i* A1 J5 o6 Y 9 b$ e6 t; t8 i* A1 J5 o6 Y

4 I9 P) M. n" |5 T/ x

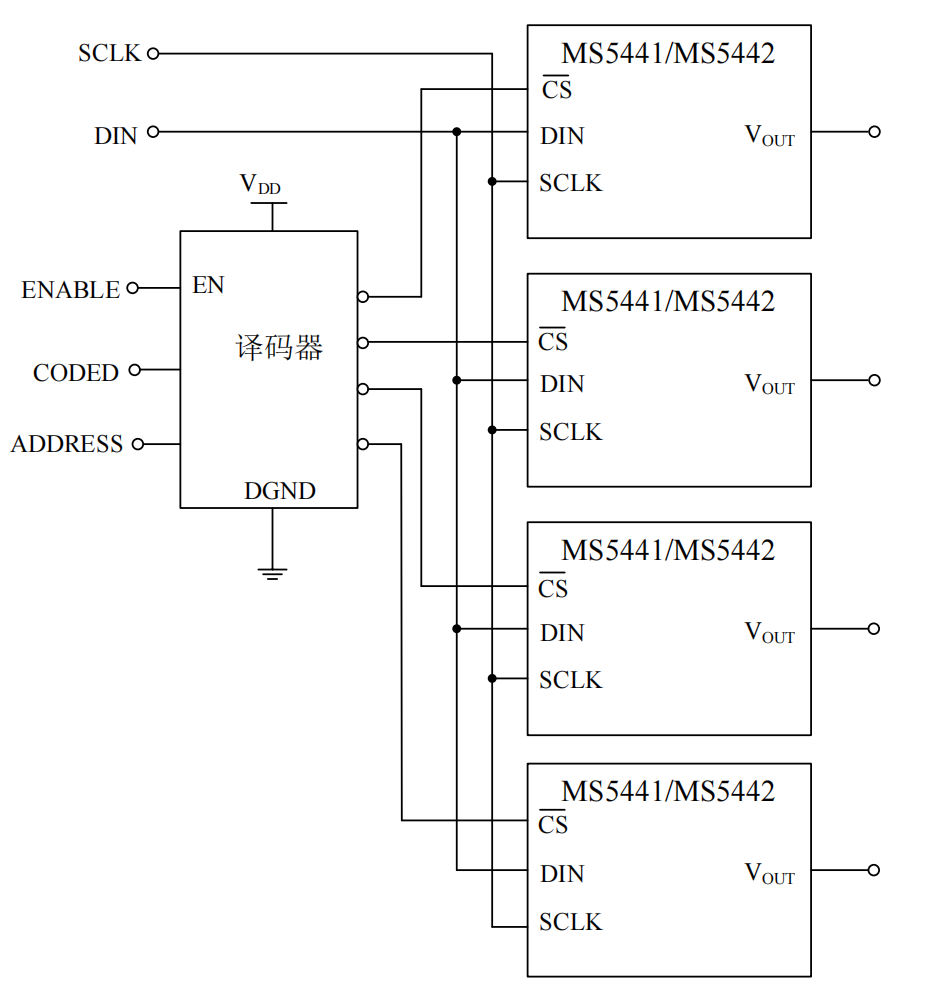

工作原理 MS5541/MS5542 是一款单通道、16 位、串行输入、电压输出 DAC。工作电压范围是 2.7 V 至 5.5V,采用 5 V 电源时的典型功耗为 165uA。数据通过三线或四线式串行接口,以 16 位字格式写入该器件。为确保处于已知上电状态,该器件设计具有上电复位功能。MS5541 单极性模式下,输出为 0V,在双极性模式下的 MS5542 输出为-VREF。MS5542 具有开尔文检测连接的参考电压和模拟地。 1. 数模转换部分 DAC 架构包含两个匹配的 DAC 部分。图 7 所示为简化电路图。MS5541/MS5542 采用分段式 DAC架构。16 位数据中的高 4 位通过解码后,可驱动 E1 到 E15 的 15 个开关。每个开关都将 15 个匹配电阻中的一个连接到 AGND 或 VREF。16 位数据中的其余 12 位驱动电压模式 R-2R 梯形网络的 S0 至 S11 开关。 典型应用 布局指南 在任何注重精度的电路中,精心考虑电源和接地回路布局有助于确保达到规定的性能。安装 MS5541/MS5542 所用的印刷电路板(PCB)应采用模拟部分与数字部分分离设计,并限制在电路板的一定区域内。如果 MS5541/MS5542 所在系统有多个器件要求模拟地-数字地连接,则只能在一个点上进行连接。星形接地点尽可能靠近该器件。MS5541/MS5542 应当具有足够大的 10μF 电源旁路电容,与每个电源上的 0.1μF 电容并联,并且尽可能靠近封装,最好是正对着该器件。10μF 电容为钽珠型电容。 0.1μF 电容应具有低有效串联电阻(ESR)和低有效串联电感(ESI),如高频时提供低阻抗接地路径的普通陶瓷型电容,以便处理内部逻辑开关所引起的瞬态电流。 多通道译码电路 MS5541/MS5542 具有片选引脚 CS,能够选择一个或者多个 DAC 一起工作。所有芯片接受相同的时钟串和数据串,但是在一个时间上只能有一个芯片接受 CS 信号。DAC 的地址有译码器决定。在数字通路上存在数字馈通现象,使用突发时钟能够将数字馈通对模拟信号通道的影响降至最低。典型电路结构如图 11 所示。

/ h" F3 p* Q# y: x- D

0 M8 b- q2 J! d! [4 }详细质料可以留言

2 x. R" o1 Y: K) Q6 G* d- \0 o. ^3 V+ y6 T m& X

|