现代的集成电路工艺加工的间隙可达0.5μm 而且很少限制数字I/O 信号的最大电源电压和逻辑电平。! \3 W7 Y: V' V* X7 K, Z! X

为了将这些低电压电路与已有的5V或其他I/O电压器件连接起来,接口需要一个电平转换器。对于双向的总线系统像I2C 总线电平转换器必须也是双向的,不需要方向选择信号。解决这个问题的最简单方法是连接一个分立的MOS-FET管到每条总线线路,尽管这个方法非常简单但它不仅能不用方向信号就能满足双向电平转换的要求还能将掉电的总线部分与剩下的总线系统隔离开来,保护低电压器件防止高电压器件的高电压毛刺波。

& e% U: ?9 o4 z 双向电平转换器可以用于标准模式高达100kbit/s 或快速模式高达400kbit/s I2C 总线系统。

" Q& _( h! L* |( u; O$ Z! L* k j% Q* L. h

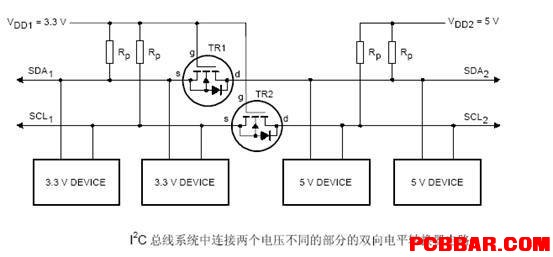

通过使用双向电平转换器可以将电源电压和逻辑电平不同的两部分I2C 总线连接起来配置入下图所示。左边的低电压部分有上拉电阻而且器件连接到3.3V 的电源电压,右边的高电平部分有上拉电阻器件连接到5V 电源电压。两部分的器件都有与逻辑输入电平相关的电源电压和开漏输出配置的I/O。

1 F8 B# o- |7 I" A6 ]2 J$ F @3 D- i. r/ Q2 J; m, i c: h

每条总线线路的电平转换器是相同的而且由一个分立的N通道增强型MOS-FET管串行数据线SDA的TR1和串行时钟线SCL 的TR2 组成。门极g 要连接到电源电压VDD1, 源极s 连接到低电压部分的总线线路而漏极d 则连接到高电压部分的总线线路。很多MOS-FET 管的基底与它的源极内部连接,如果内部没有,就必须建立一个外部连接。因此,每个MOS-FET 管在漏极和基底之间都有一个集成的二极管n-p 结。如下图所示。

) [0 L+ o8 Q3 p0 V$ r# C$ q) w

]- o' n/ Q% B" S) R

]- o' n/ Q% B" S) R

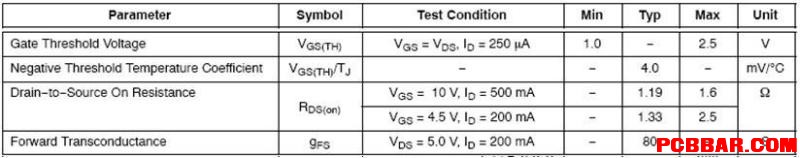

电平转换器的操作 在电平转换器的操作中要考虑下面的三种状态: 1、 没有器件下拉总线线路。 低电压部分的总线线路通过上拉电阻Rp 上拉至VDD1(3.3V) MOS-FET 管的门极和源极都是VDD1(3.3V), 所以它的VGS 低于阀值电压MOS-FET 管不导通这就允许高电压部分的总线线路通过它的上拉电阻Rp 拉到5V。 此时两部分的总线线路都是高电平只是电压电平不同。 2、一个3.3V 器件下拉总线线路到低电平。 MOS-FET 管的源极也变成低电平而门极是VDD1(3.3V)。VGS高于阀值,MOS-FET 管开始导通然后高电压部分的总线线路通过导通的MOS-FET管被VDD1(3.3V)器件下拉到低电平,此时两部分的总线线路都是低电平而且电压电平相同。 3、一个5V 的器件下拉总线线路到低电平。 MOS-FET 管的漏极基底、二极管低电压部分被下拉,直到VGS 超过阀值,MOS-FET 管开始导通,低电压部分的总线线路通过导通的MOS-FET管被5V 的器件进一步下拉到低电平,此时两部分的总线线路都是低电平而且电压电平相同。 这三种状态显示了逻辑电平在总线系统的两个方向上传输,与驱动的部分无关。状态1 执行了电平转 换功能,状态2和3按照I2C总线规范的要求在两部分的总线线路之间实现“线与”的功能。除了VDD1 (3.3V) 和VDD2 (5.0V)的电源电压外,还可以是例如2V VDD1 和10V VDD2 等的正常操作。其中VDD2必须等于或高于VDD1 。 但是值得注意的是,VDD1作为较低部分的电压,必须能够大于所选择的MOS-FET的阀值电压,也就是必须能够打开MOS-FET。此管参数必须谨慎选择。如下两种参数MOS-FET,在VDD1 (1.8V)到VDD2 (3.0V) 的电路中就可能存在截然不同的效果。 管1

: N* [7 z6 ^# S( n5 [0 C& R

4 n0 B& \" C. }: ?

4 n0 B& \" C. }: ?

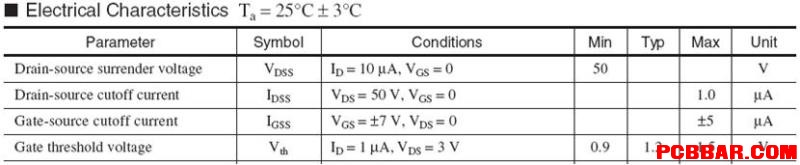

管2

0 w/ ]# U) }3 F7 J. M3 z/ v" F! X

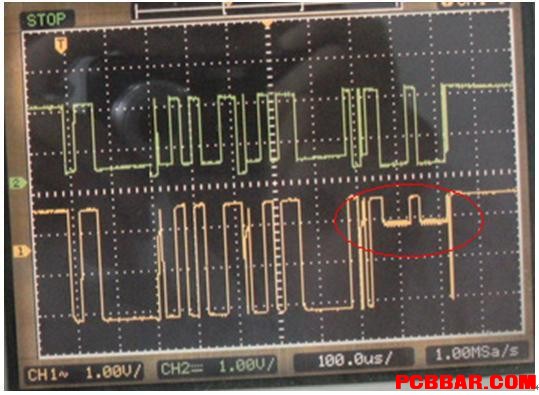

1 a& _7 M |, x+ l 选择管1,由于VGS的范围是1.0~2.5V,很有可能出现大于1.8V的状况,因此VDD1方面传输低电平信号时,MOS-FET不能很完全的被打开,导致到VDD2 (3.0V)方面的信号不能彻底为低,出现半高状态。如下图:

: l- f& {, j3 U) t* n) L

& ?- a$ ?4 Z! T( I+ T- i

& ?- a$ ?4 Z! T( I+ T- i

择管2,由于VGS的范围是0.9~1.5V小于1.8V,因此,通路才会正常工作。 其他不同电压间的转换原理如上,请悉心选择器件。 在3.3V IIC总线中用到5V IIC器件,该电路已实验通过。 / B) E8 F% |5 A6 f- L6 J0 c

+ ]& d& T" P$ f3 t3 C

( u$ L! J! d. Y s0 K' r1 R9 N4 e7 r |