Vivado下bit文件下载步骤

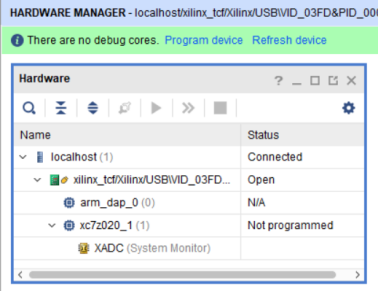

" H# \. d9 C6 R- N2 D% a0 s7 t将电源、下载器与板卡连接,打开Vivado工程,参考《基于TcL脚本生成Vivado工程及编译》文档编译工程,生成对应的bit文件。 打开板卡电源开关,找到右下角的”Open Hardware Manager”展开,右击”Open Target”弹出一个小窗口,右击”Auto Connect”选项。  $ Q, Z1 t; I s8 r $ Q, Z1 t; I s8 r

- O ^0 ?0 G+ H) f7 T' l& s等待Vivado识别对应的板卡。  ' K0 _9 [+ n+ r9 C

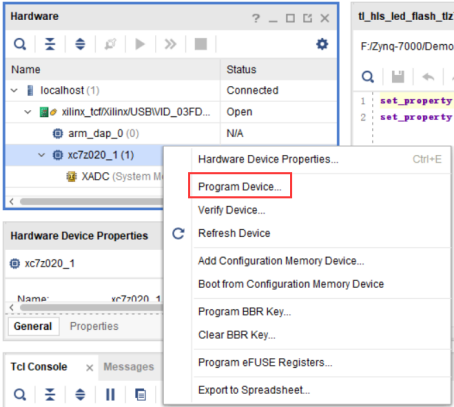

' K0 _9 [+ n+ r9 C右击xc7z020_1弹出一个窗口,再点击”Program Device…”。  1 k* ~$ e9 V! R! I8 `' A& F. N6 ^7 o

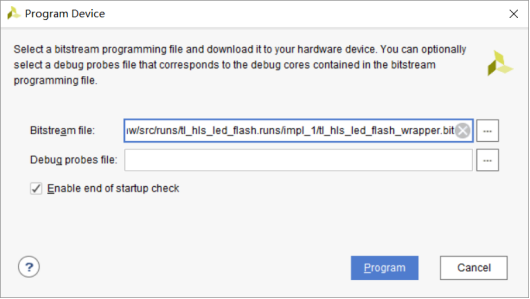

1 k* ~$ e9 V! R! I8 `' A& F. N6 ^7 o在弹出窗口”Bitstream file”栏选择编译生成的bit文件(工程编译完成后自动选择对应的bit文件),右击Program开始烧写bit文件。  6 b$ g2 t. l# N; ^3 Y* V 6 b$ g2 t. l# N; ^3 Y* V

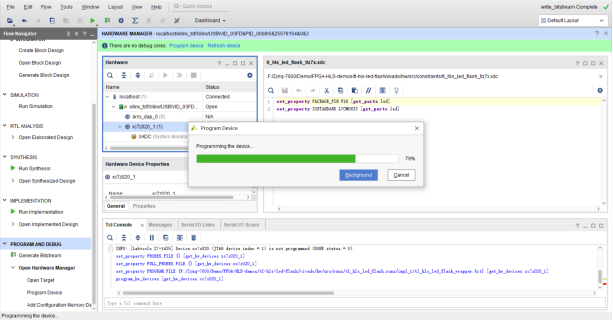

等待烧写完成。  2 J* J& n9 E& E: D5 F

2 J* J& n9 E& E: D5 F

若例程中使用PS端FCLK作为PL端系统时钟信号,PS端与PL端在上电过后需要通过使能PS-PL电压电平转换寄存器,才能使用FCLK。Xilinx官方文档ug585中”2.4 PS–PL Voltage Level Shifter Enables”章节有详细说明。修改方法参考以下步骤操作。  1 d; C3 g! q7 w q" [8 }

1 d; C3 g! q7 w q" [8 }

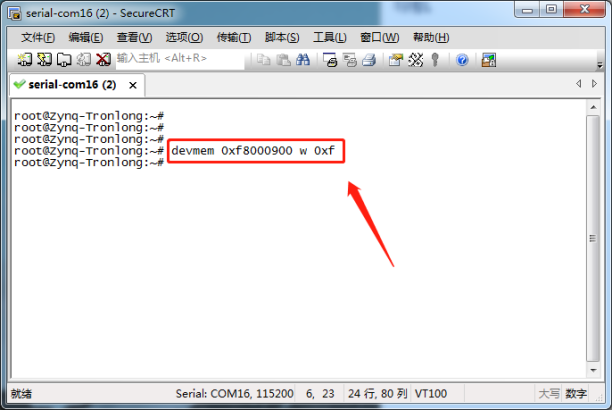

) {' ]$ o- Z1 e开发板上电,SD启动后,先加载bit文件配置好PL端,然后在PS串口调试终端输入下面命令使能PS-PL电压电平转换寄存器。 Target# devmem 0xf8000900 w 0xf  & L) E6 J7 O, D! l% R & L) E6 J7 O, D! l% R

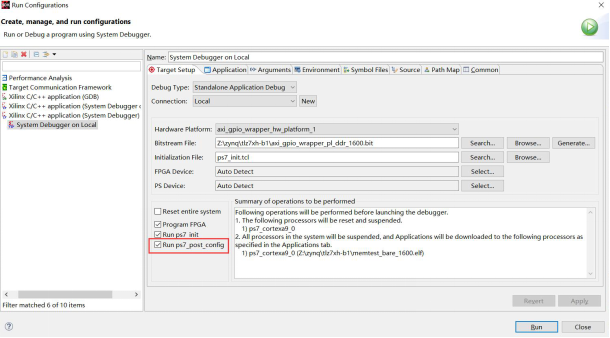

打开Xilinx SDK,点击”Run->Run Configuration”,在配置界面勾选”Run ps7_post_config”,确认需要加载的bit文件,然后点Run。  : P4 L- T) w# t; E$ v/ x; V8 R : P4 L- T) w# t; E$ v/ x; V8 R

也可以在debug后,通过Memory窗口修改0xf8000900寄存器的值为0xF,使能PS-PL电压电平转换寄存器。

$ X# s$ [: i2 Z& _ |