|

TL6678-EasyEVM是广州创龙基于SOM-TL6678核心板而研发的一款多核高性能DSP开发板。开发板采用核心板+底板方式,底板采用沉金无铅工艺的四层板设计,尺寸为200mm*106.65mm,它为用户提供了SOM-TL6678核心板的测试平台。为了方便用户开发和参考使用,上面引出了各种常见的接口,可以帮助用户快速评估SOM-TL6678核心板的整体性能。 广州创龙SOM-TL6678核心板采用TI 的KeyStone C66x多核定点/浮点TMS3206678高性能DSP处理器,采用沉金无铅工艺的12层板设计,尺寸为80mm*58mm,经过专业的PCB layout保证信号的完整性,和经过严格的质量管控,满足多种环境应用。

开发板引出了1个PCIe Gen2 x4接口(CON11),2通道,编码方案为8b/10b,总共64pin,主接口区42pin,单通道理论最高传输速率达5GBaud,即为5GBaud*8/10=4Gbit/s,硬件及引脚定义如下图: 拓展IO信号# q% ]2 d3 Z2 m. {, e' G2 B

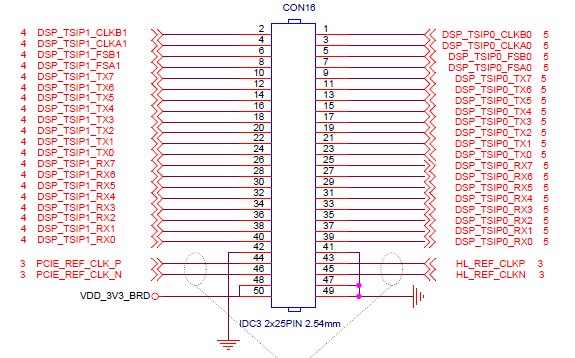

EMIF16信号通过50pin、2.54mm间距简易牛角座引出(CON9),硬件及引脚定义如下图: SPI、I2C、TIMER、GPIO等信号通过50pin、2.54mm间距简易牛角座引出(CON10),硬件及引脚定义如下图: TSIP信号通过50pin、2.54mm间距简易牛角座引出(CON16),硬件及引脚定义如下图:9 V; g) c' i2 D+ w1 Y/ L* |5 r

- o& @3 |) v9 G3 a+ i S : l& @0 b. z) l0 a) i : l& @0 b. z) l0 a) i

: d R+ U# ^$ o2 y

|