|

|

引言* F$ z; B" B8 c+ ]& p

0 w9 F/ H+ L( x0 E/ b6 ]

随着大型语言模型(LLM)规模和复杂度不断增长,对能够高效处理这些模型且同时最小化功耗的专用硬件加速器的需求也随之增加。传统的AI加速器通常将张量收缩映射到矩阵乘法单元上,这往往无法充分利用张量运算中固有的并行性和数据局部性。由FuriosaAI开发的RNGD处理器采取了不同的方法,使用张量收缩作为原始计算单元,而非矩阵乘法。这种创新的5nm芯片专为提供高内存带宽和密集计算能力而设计,同时保持LLM推理过程中的功率效率[1]。- w( p/ B- a8 H

i2espi4t5cl64097953204.png

! H6 j. j/ d: O2 a+ H架构概述

6 O# J9 x" S& m* ^4 _9 R$ d) V4 A, U9 ^* D

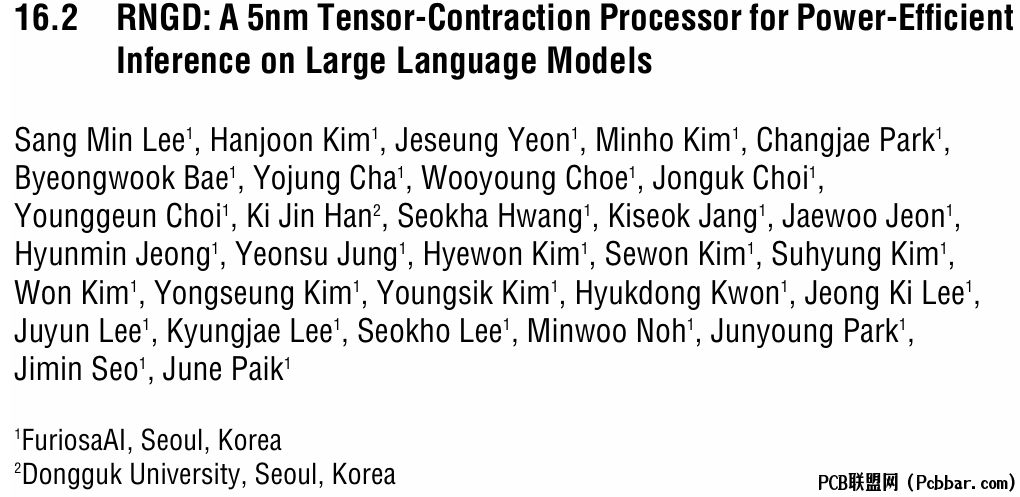

RNGD采用独特的架构方法,将大型粗粒度处理元件(PE)分割成称为"slice"的更小计算单元。这种设计启用了大规模并行性和类似于向量处理器的时间轴流水线。根据连接这些slice的获取网络的配置,这些slice可以作为一个大型处理元件或多个独立计算单元运行。

$ f1 ~* H+ Y* \7 u; g

ofpp4yj2u1464097953304.png

. D' R# A6 e% z+ E8 e& I- t

. D' R# A6 e% z+ E8 e& I- t

图1展示了张量收缩处理器的处理元件结构,包含四个slice、多上下文操作示例及芯片规格概要。

+ G- g X9 n3 D7 p- }

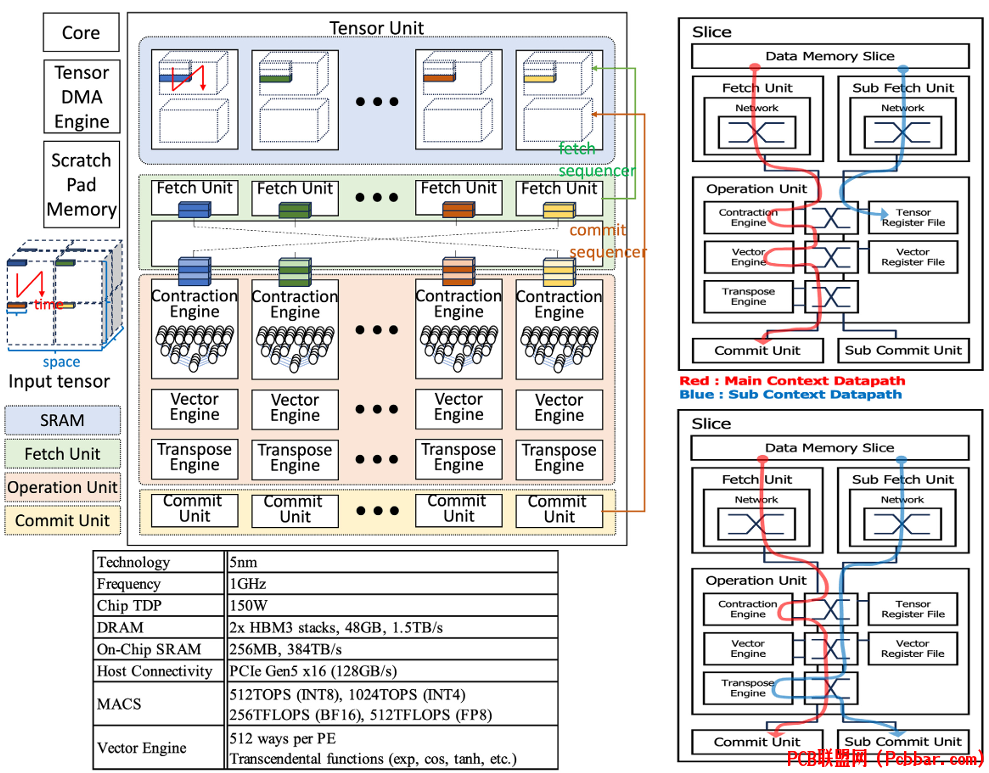

& R' C% T% g* u1 I2 d \RNGD由两个PE集群组成,每个集群包含四个PE和路由器。每个集群的片上网络(NoC)以1GHz的频率运行,提供高达1TB/s的内存带宽,最大限度地减少多个PE同时访问高带宽内存(HBM)时的瓶颈。单个PE可以独立运行,或与最多三个其他PE组合形成更大的PE。# z ?: k+ u1 K

e1qtrfokgsh64097953404.png

1 m B. Q9 }' Q7 P$ g9 c4 V& J& g图2说明了芯片的框图、处理元件平面图和设计中采用的时钟布线策略。6 E) E8 Y7 M3 v6 g! m" d

8 A" a0 m6 ^8 R7 O% H# y

每个PE包括一个CPU核心、一个带有32MB SRAM的张量单元(TU)和用于张量传输的张量DMA(TDMA)引擎。TU能够提供64 TOPS(万亿次运算每秒)的计算能力,持续从SRAM获取输入张量,处理这些张量,并将结果存回SRAM。对于超出单个芯片容量的大型模型,RNGD支持PCIe点对点(P2P)通信进行芯片间协调,测得的吞吐量分别为不带PCIe交换机时32GB/s和带PCIe交换机时52GB/s。

g( W- m1 n$ M3 `- C处理元件设计

% G: X4 e7 k j6 T7 @6 m+ g/ d0 F4 p8 Y6 }% L4 {+ f4 ~

RNGD的处理元件是其架构的核心。每个PE包含65个slice,其中一个保留作为备用以提高芯片良率。虽然这些slice在功能上相同,但由于PE内位置不同导致的I/O位置变化,存在8种不同的物理形状。& T! q7 a; h/ W# }7 \9 h6 O( M4 g

$ n, O- Q2 a* f! E. y1 i, E+ M& i

这些slice通过TU片上网络(NoC)互连,该网络由65个路由器节点组成,排列成双向环形拓扑。从每个slice的SRAM中获取的数据通过获取网络顺序传递到操作单元,包括收缩引擎(CE)、向量引擎(VE)和转置引擎(TE)。 N0 C7 N$ g/ q+ O- ~3 ]

) j' R/ T. \8 V0 ^CE包含8个点积引擎(DPE),执行逐元素乘法并通过深度可配置的归约树产生可变数量的输出。VE处理非线性函数、逐元素操作、归约和类型转换,而TE则将张量的最后一个轴与其他轴转置(例如,将b × l × e转换为b × e × l)。

9 b5 Q( I, |7 _+ Q j" W

( B& V, `: y; pTU控制器(TUC)通过访问TU控制和状态寄存器来管理和监控这些slice。CPU核心可以通过直接写入这些寄存器或通过TUC的命令队列发送命令来配置张量操作。这种设计实现了异步张量操作和数据移动,使CPU核心能够与张量计算并行执行其他任务。

# S9 s1 k; L/ \+ Y内存系统与集成. f0 t2 {0 |4 p. k) @+ N2 v& q

u# x! X; y- S; A0 xRNGD配备两个HBM3堆栈,提供高达1.5TB/s的内存带宽。内存NoC通过地址哈希交织有效地将流量从PE分配到32个HBM通道。

5 [5 B* O. s, x$ C1 }

vf30m1uhxav64097953504.png

7 q `4 p1 [6 Z

7 q `4 p1 [6 Z

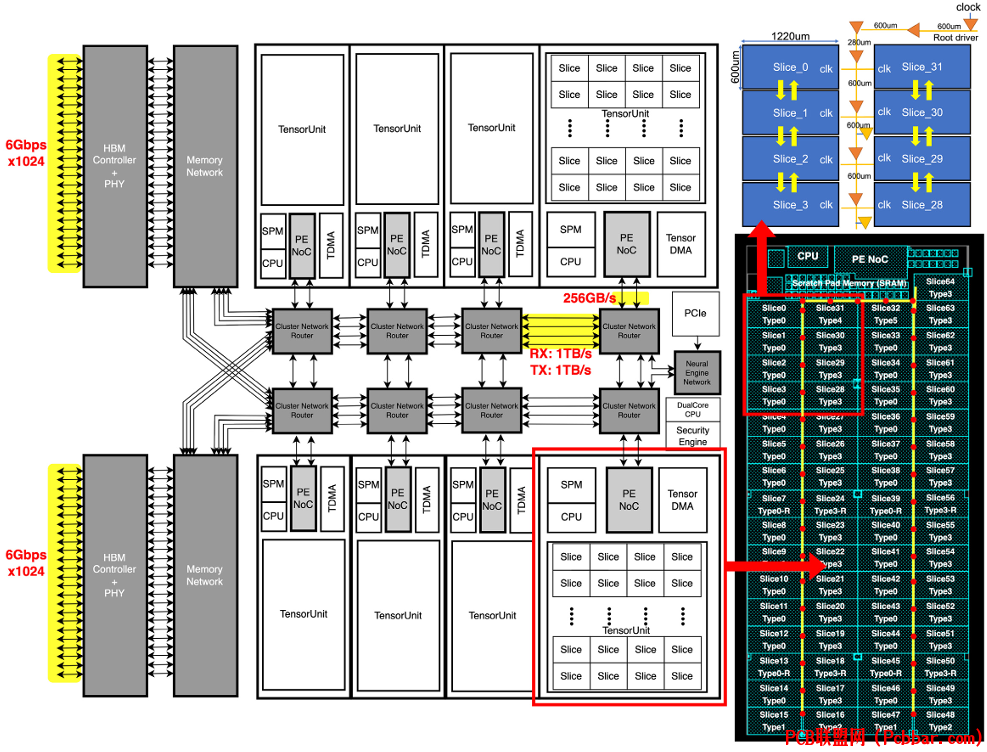

图3展示了HBM集成方法以及为确保可靠运行而进行的信号/电源完整性分析。

7 Y# S0 p- Q5 r/ V* ~" }6 W

: J) v5 N3 w* s( O1 H设计师使用硅中介层的3D全波电磁建模进行HBM信号完整性(SI)和电源完整性(PI)分析。考虑了各种HBM切换模式以激发片上和片外共振,确保电源分配网络(PDN)阻抗在数据频谱中得到抑制。通过广泛的系统电源瞬态模拟和PDN优化,团队在0.4V VDDQL时实现了3.65%的Vpp,在0.75V VDD时实现了7.48%的Vpp。

0 h+ `+ O$ R) V, |* g0 U6 g& Y' u; [* ~2 Z

硅中介层上HBM PHY和DRAM之间的高速互连经过精心设计,以最小化串扰和电容负载。互连通过S参数和瞬态模拟进行分析,显示在RX I/O焊盘处的眼图优于0.76UI。( X% _: w% I& H

电源管理与可靠性( K* I6 \/ A+ A0 B' j5 c& l

" Z/ E7 o( a! n4 uRNGD实施了复杂的电源管理技术来平衡温度和性能。动态电压和频率调节(DVFS)有效控制总板功率,在运行期间保持在150W以下。

" [- f, B% S+ p, }$ v( ]3 I1 t

s00ivrwkktx64097953604.png

9 V: e5 _, i1 P. s

9 V: e5 _, i1 P. s

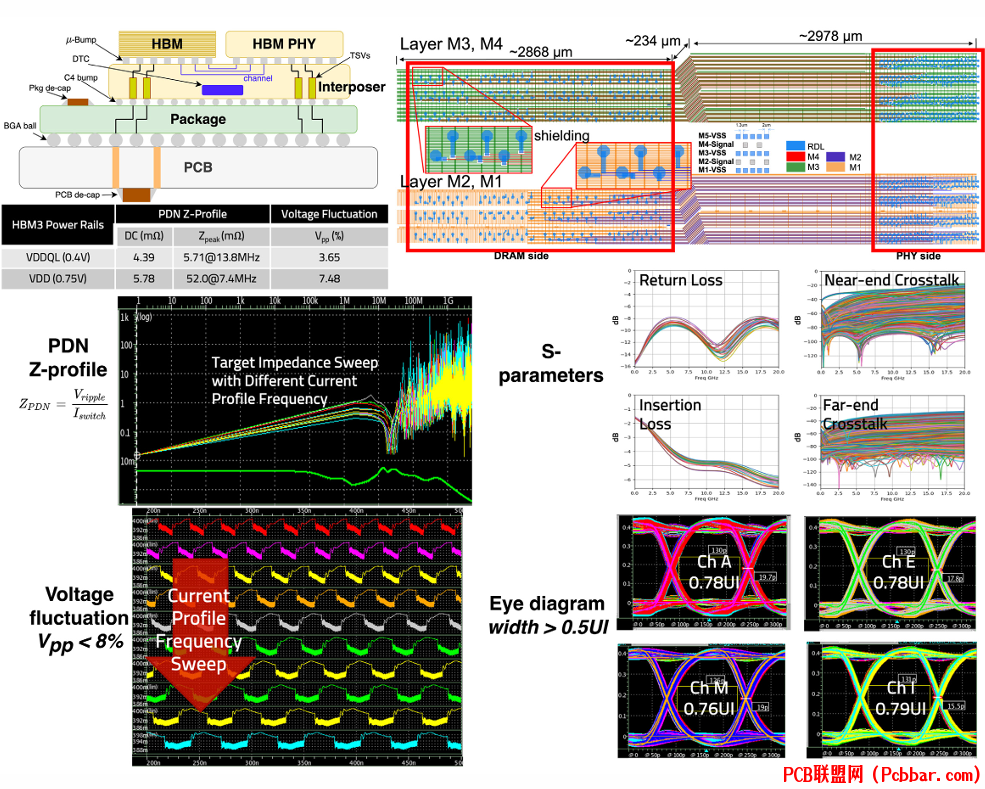

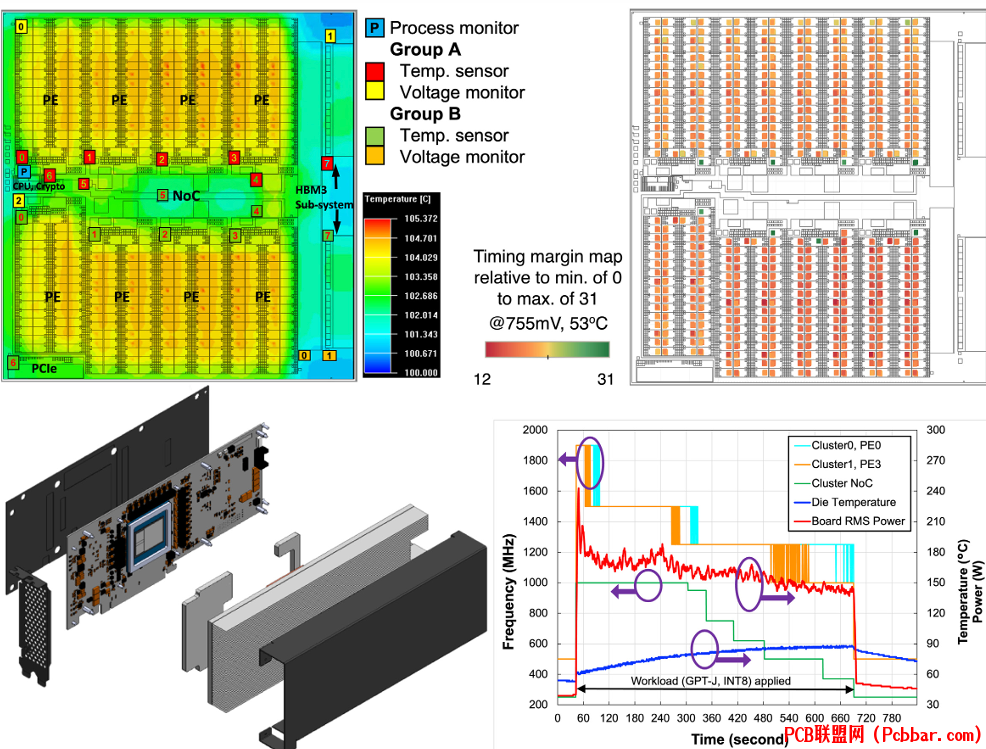

图4展示了带有片上监视器、时序裕度图、DVFS图和定制散热器设计的芯片热模型。# C+ \% x4 C4 f1 [8 C

5 d7 j4 J; K; |, R8 m" X温度传感器分布在整个芯片上,并在运行期间定期监测。为管理高峰值电流,设计包括各种去耦电容,如片上、金属-绝缘体-金属(MiM)和中介层深沟电容(DTC)。每个集群的DTC量为24.5μF。全数字宽带电压下降检测器监控局部快速供电电压下降,如果电压低于预定义阈值则触发中断。! M) t0 [5 a# G0 N8 J* j

) ^9 y% H$ g1 u, \0 v1 p" A/ T

时序裕度在不同的芯片位置持续监测,同时也监测长期老化,这对数据中心可靠性非常重要。芯片支持加密进行安全启动,确保系统完整性。数据内存和SPM的控制逻辑以及HBM控制器支持单错误纠正和双错误检测。单比特错误被计入统计数据,双比特错误则触发中断。+ A+ S" \. P2 h2 m6 I

, C7 v$ _" t* u+ w) X( i+ u! J

为提高先进5nm工艺节点和653mm2大芯片面积的芯片良率,分级过程允许用备用slice替换有故障的slice。在晶圆测试期间,所有slice都经过测试,状态记录在片上保险丝中。在启动期间,读取这些值,PE内单个有故障的slice可以用备用slice替换。但是,如果PE中有两个或更多slice失效,整个PE被视为失效PE。如果集群中任何一个PE失效,整个PE集群被视为失效。; y" y1 a6 \9 e

性能分析0 D' F* F8 a0 F! t5 Q3 _

/ X) A( S* F; J, `" ` h, V4 H

RNGD采用的张量收缩方法最大化了并行性和数据重用,这对LLM推理特别有益。

3 K" e5 X+ \# M

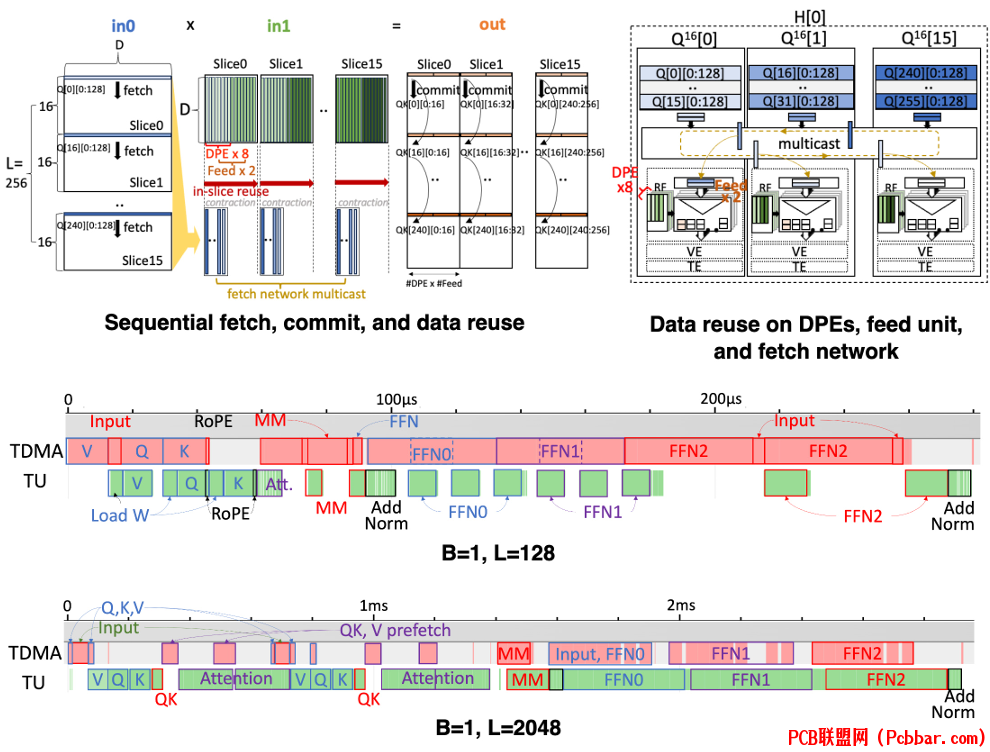

4mam1u2snct64097953704.png

: q1 |/ o# F6 ^) p" e图5展示了张量收缩如何最大化并行性和数据重用,同时显示处理过程中如何隐藏计算或传输时间。

8 f: w+ P4 }( y/ g+ P2 F% b/ I/ Q3 Q8 B9 u A$ |' {% Q* s( G

该图说明了一个注意力头的查询(Q[0:256][0:128])和键(K[0:256][0:128])矩阵的乘法,以及矩阵Q在16个slice上的分布。还显示了预填充阶段编码器块的TU和TDMA活动跟踪,展示了短序列长度下计算时间如何隐藏在权重传输之后,以及长序列长度下计算占主导地位时权重传输时间如何隐藏在计算之后。! ?( N; Q+ y/ G+ s& g7 f

" L7 g$ }' B& X* Y

与其他加速器相比,RNGD显示出令人印象深刻的效率。

1 d, T4 e/ c2 f

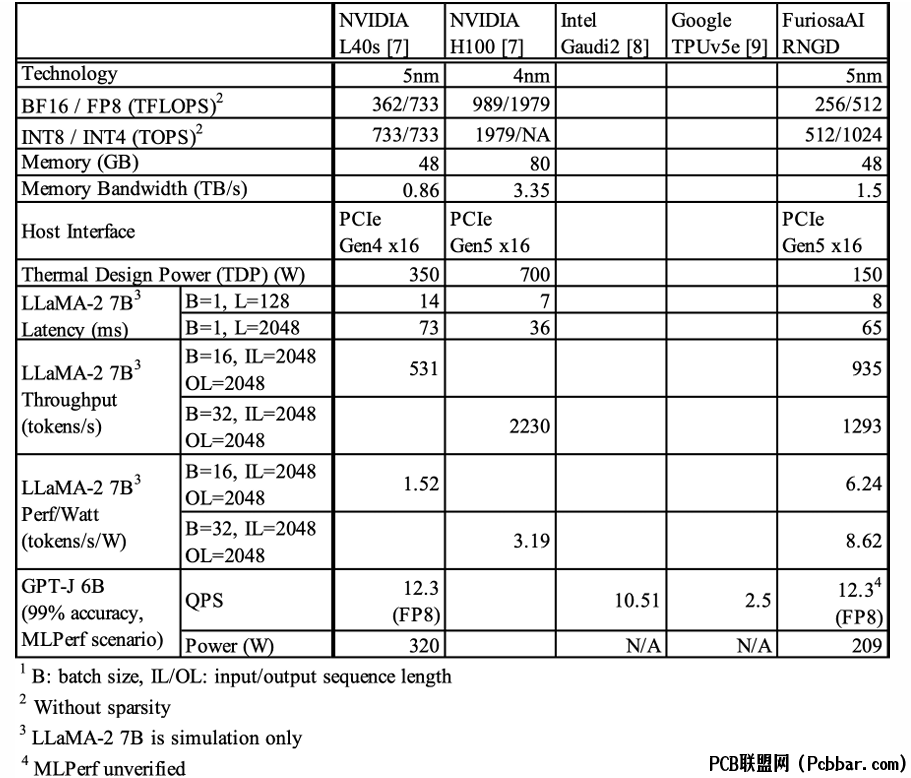

bgjdyxraxhy64097953804.png

! f8 i+ M; j5 b; G5 a2 n+ P0 f

! f8 i+ M; j5 b; G5 a2 n+ P0 f

图6提供了RNGD与其他加速器在延迟和大型语言模型性能方面的比较。

( G- j7 h/ Z& J( G+ |9 N- k7 h1 U' n6 K' C5 n9 C

RNGD的峰值内存带宽比NVIDIA L40s GPU高1.7倍,吞吐量快1.76倍,而热设计功率(TDP)低57%。虽然NVIDIA H100的速度快1.72倍,内存带宽高2.2倍,但其TDP比RNGD高4.7倍。这种比较凸显了RNGD相对于其功耗的卓越吞吐效率,这归功于其有利的内存带宽与TDP比率。测量的GPT-J 6B每瓦性能在99%准确率下比L40s高53%。- v- ^( T4 v3 C4 n

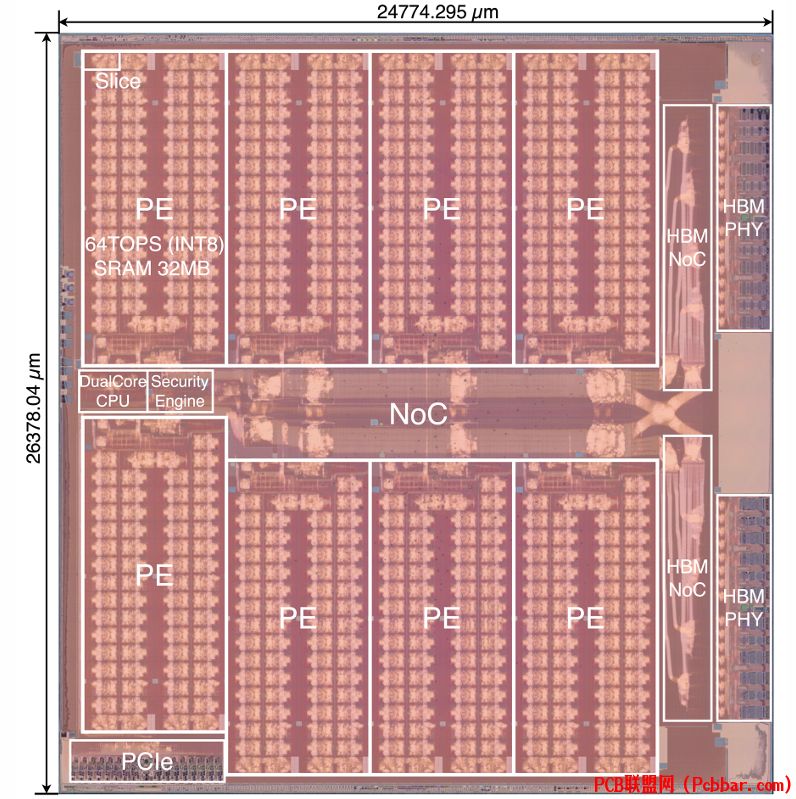

uiccfkxomut64097953904.png

! w& n! t5 s& W1 P: @9 V0 w图7展示了RNGD处理器的芯片显微照片,说明设计的物理实现。' [8 c2 u5 u7 d% v6 {

结论 L* H: B- S2 _4 X. q& e, G. [

1 Z2 A7 u7 B, z& z/ GRNGD处理器代表了大型语言模型硬件加速的重要进步。通过使用张量收缩而非矩阵乘法作为原始操作,实现了高计算效率和功率性能。其创新架构,具有灵活的处理元件和slice,实现了大规模并行和高效数据重用。结合高内存带宽和复杂的电源管理技术,RNGD为LLM推理提供了令人印象深刻的性能,同时与传统GPU加速器相比保持较低的功耗。随着LLM规模和重要性的持续增长,像RNGD这样的专用硬件加速器将在使这些模型更易于使用和更加节能方面发挥关键作用。; \6 b, g' a% r0 I6 b6 Y9 I) H/ w

参考文献% z' `0 D! A$ R0 W3 B5 s8 w( _

+ H) \ M* H( x! A/ e$ d[1] E. Medina and E. Dagan, “Habana labs purpose-built AI inference and training processor architectures: Scaling AI training systems using standard ethernet with Gaudi processor,” IEEE Micro, vol. 40, no. 2, pp. 17-24, 2020.

, Z, p# e! R2 |$ n! s5 o4 h" q' ?4 q* y) @9 A/ E7 s

[2] S. Knowles, “Graphcore,” Hot Chips 33 Symposium (HCS), 2021.

7 T/ Y) B% F( {* s3 p

9 s# X% _, y: t( E' q[3] K. Chatha, “Qualcomm? Cloud Al 100 : 12TOPS/W scalable, high performance and low latency deep learning inference accelerator,” Hot Chips 33 Symposium (HCS), 2021.

4 f% i6 F4 _; F6 J9 g$ D3 p8 L* A" v: ^3 g3 j" Z8 T- w

[4] N. Jouppi, et al., “TPU v4: an optically reconfigurable supercomputer for machine learning with hardware support for embeddings,” ISCA, 2023.$ ?4 x1 e9 Q' m2 B" P$ [# K7 ?

+ r9 y" H: F: C2 I! l[5] M.-J.Park, et al., “A 192-Gb 12-high 896-GB/s HBM3 DRAM with a TSV auto-calibration scheme and machine-learning-based layout optimization,” IEEE JSSC, vol. 58, no. 1, pp. 256-269, Jan. 2023.

1 w3 g6 E' }9 c5 ]0 _6 M. V5 [9 x, _' {( s7 Y9 s% z

[6] V. Sze, et al., “Efficient processing of deep neural networks: a tutorial and survey,” Proc. IEEE, vol. 105, no. 12, pp. 2295-2329, Dec. 2017.# Q% ^, Y4 m& V

1 ~* x4 `; ^; f: C" k6 \% V! l. E# ?[7] NVIDIA, “NVIDIA AI inference performance,” [Online]. Available: https://developer.nvidia.com/deep-learning-performance-training-inference/ai-inference.

+ Q. w b& O L6 _! ^% h- I% [1 `( n3 Q, Z% n U" ]" T: w

[8] MLCommons, “v3.1 Results,” [Online]. Available: https://mlcommons.org/benchmarks/inference-datacenter/.

. F: B3 j8 a+ \/ o/ X( B7 ?: Q+ q8 J) l8 Q

[9] MLCommons, “v4.0 Results,” [Online]. Available: https://mlcommons.org/benchmarks/inference-datacenter/.

! z$ D* `9 Y5 @; qEND

2 H4 w) v1 S9 M/ i5 w软件试用申请欢迎光电子芯片研发人员申请试用PIC Studio,其中包含:代码绘版软件PhotoCAD,DRC软件pVerify,片上链路仿真软件pSim,光纤系统仿真软件pSim+等。更多新功能和新软件将于近期发布,敬请期待!3 b3 y; U2 D1 @: d0 ^" u9 O

点击左下角"阅读原文"马上申请

5 r+ `, N0 Y# U) B* K

+ v6 g1 j: Z4 u& {/ v欢迎转载' \/ J$ `% ]% d5 k( n/ ^

4 I8 F# d" G! r" {' ~转载请注明出处,请勿修改内容和删除作者信息!1 \" O( d! F! o! Y7 v

% E7 L# h' R8 `) `( ]7 i; R1 ?

( r8 v9 A, Y! a( G K4 k- ~ R- Z2 P% {5 |

xc3a3vgl1uw64097954004.gif

( u. j- U- O+ j. x

( u. j- U- O+ j. x

8 v0 ]) G1 K1 M @* L

关注我们

3 y3 a' v/ b$ C7 s( Q5 n6 K+ y

/ S$ x( _: F; R: L7 X* C2 E! _2 S% P. Q4 u! \8 O

qarqon4zdjl64097954104.png

4 U; f p* K+ Q$ @ | " x# C; W9 f, w' _

xdejhf3d41r64097954204.png

9 W5 ~* a2 |* U4 L- t4 ~ |

) h, M( |8 T, R! Q) O

cawryn5mmm364097954304.png

# u1 H% }( o& P, M, U, u |

" ^# C5 h- [4 k5 N3 L1 s( ]/ W3 P. P1 e, F; U

' y) s5 U/ `4 X3 P7 g

& D5 C- l+ p4 d6 k关于我们:) f6 ]( @0 z' B: p8 H" p. Q1 _

深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

! g) E j$ O) g& J# ^6 _; u7 f7 R: R# z' e; [" b7 h+ w/ [) s2 N

http://www.latitudeda.com/

, ?0 Q; t4 e0 a* w( C, `5 c(点击上方名片关注我们,发现更多精彩内容) |

|

/1

/1