|

xhqpn1cafcw64032199110.gif

1 c. n7 n- y+ j; ?) F7 H4 |点击上方名片关注了解更多

6 Y: B% A1 |0 |/ I' {. q

" e0 L) m; d/ H- [+ |5 `' O5 G" I7 G6 Q

3 l+ m% u* @8 l9 c) G8 r9 Q大家好,我是王工。

% @. G: o& r: e. H% Z% z

4 |2 w, E' T' B* F5 w" X& @- m近期在公司PCB layout评审过程中,关于USB3.0背面接口区域是否需要做掏空处理的问题,团队中存在一些不同的见解。今天我想借此机会与大家一起探讨交流这个技术细节,看看大厂都是要求怎么做的。

+ O& m, Z( ~! j# S& v011

1 \9 A& R, V9 I6 B0 w7 Z- F大厂对高速接口的设计要求/ y. Q8 h w9 P% x* ~8 ^' Z

在高速信号接口,如USB3.0、HDMI、PCIe、SATA等的设计规范中,一些知名芯片厂商都会提出明确的设计要求。3 o2 |0 {1 Z' S

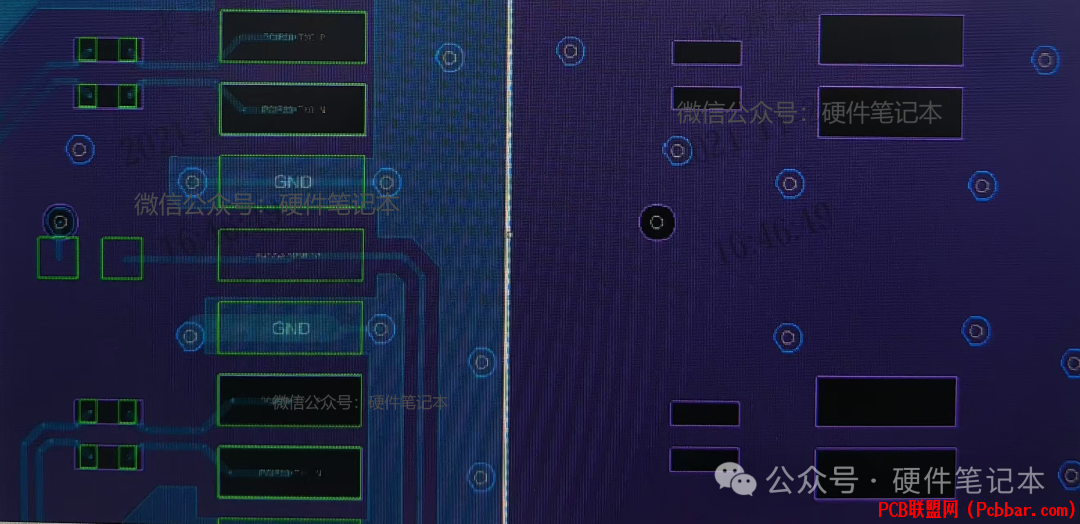

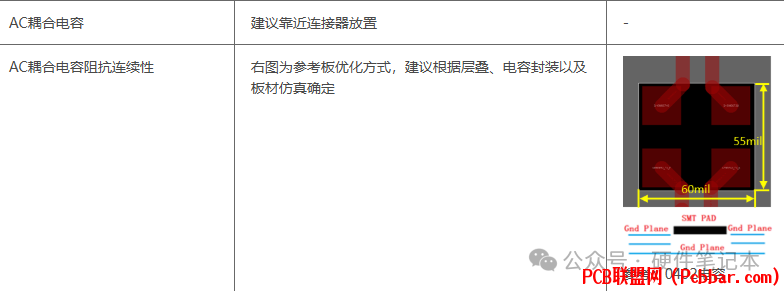

USB3.0座子的焊盘和AC耦合电容的焊盘下方必须挖空一层来保证阻抗的连续性,挖空的大小,不小于封装焊盘尺寸。8 `5 T* c9 Z! t% \: O0 n' q

x00lurw5ysf64032199210.png

: v9 `; ]7 a3 n' N' i+ L$ i3 ~

: v9 `; ]7 a3 n' N' i+ L$ i3 ~

b+ e3 Y$ |0 y* I

! k5 d$ k2 w; d5 [! j; b

HDMI座子的焊盘和TVS管的焊盘的下方必须挖空一层来保证阻抗的连续性,挖空的大小,不小于封装焊盘尺寸。

6 y8 V6 l: ]" X& y7 W" i: K& w

3333njnfmz564032199310.png

" r" H; }; f7 d7 g: L. W6 X

0 _* j3 k# p9 |+ O, l" ?2 w

+ v( Q1 h. f2 U8 L) T3 M8 GPCIE Slot的焊盘和AC耦合电容的焊盘的下方必须挖空一层来保证阻抗的连续性,挖空的大小,不小于封装焊盘尺寸。

! S. r! a- O2 L- L8 O# @

rzptgzpify364032199411.png

" F0 R6 q+ Y8 `' z8 b+ B0 h

" F0 R6 q+ Y8 `' z8 b+ B0 h

+ z, b$ J% H: |7 ]" G- g( _

8 x- q; p* t4 A2 W% y: S+ b

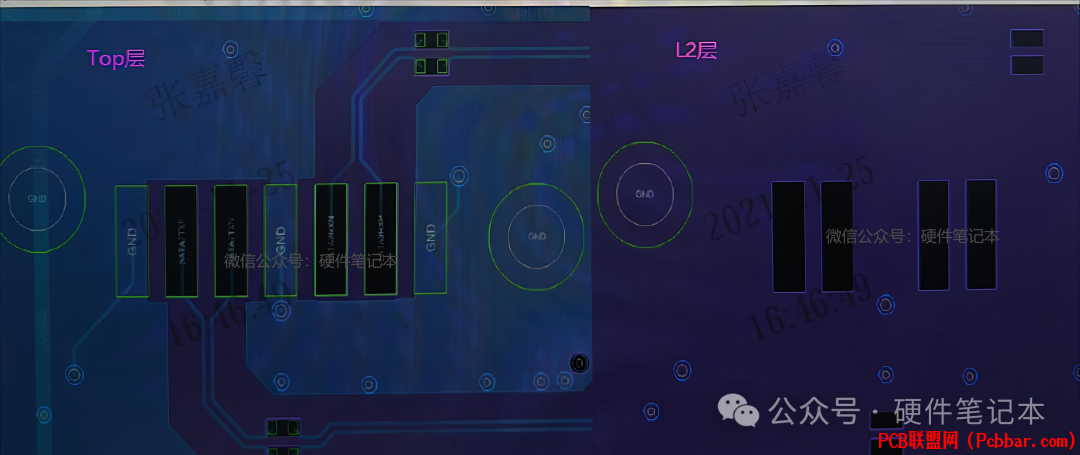

SATA座子的焊盘和AC耦合电容的焊盘的下方必须挖空一层来保证阻抗的连续性,挖空的大不小于封装焊盘尺寸。

+ K G+ P- y9 ]& q/ [7 H4 I

paubdfr0gtu64032199511.png

6 g6 I3 k6 m3 J! W

6 g6 I3 k6 m3 J! W

9 ?; t% m K3 w8 H6 }6 z& H8 Q0 c7 n9 O$ j% C# L) v. D: W

. d' s# Y& M& ~/ G' I, B7 Y- i

0212 N4 h- }+ {. l' p

从原理上来理解挖空参考层的要求

, v# p8 W% k5 \; E, R7 u3 H为什么需要挖空参考层?上面其实芯片大厂也有提到,高速接口信号(如HDMI 2.1的12Gbps速率)对阻抗连续性极其敏感。焊盘和TVS管(静电保护器件)的焊盘区域由于以下原因会导致阻抗突变:1 X, h9 u/ ]. ~& C! x

焊盘厚度增加:相比普通走线,焊盘更厚,导致局部电容增大,阻抗降低。0 b |) J6 N- U. m& e& D

TVS管寄生电容:TVS管本身有寄生电容(如0.5pF~2pF),会进一步降低高频信号阻抗。+ ^4 I+ r" J1 u9 f! F# [

# d" Y/ g7 m. s: g' \

以下是各高速接口的传输线阻抗要求HDMI接口,传输线阻抗差分100ohm,±10%。

9 ^% r) C- b1 S

qun5hq1qtq364032199611.png

% b" W- @6 C) e' h

; `& j. G. d0 f8 ^4 e+ R; \8 U+ S. c$ P) @

PCIE接口,传输线阻抗差分90ohm,±10%

$ B E, ^* {9 C

bg5pbaewyyl64032199711.png

( i3 n9 X) W6 H( y% Q% u2 o! T9 X

( i3 n9 X) W6 H( y% Q% u2 o! T9 X

6 D( j& l! |; }+ Q! ]' h% F; N

SATA接口,传输线阻抗差分90ohm,±10%3 P+ B/ E# f! L6 M( F

jch0wgyafen64032199811.png

/ v* x* n- r- h, K0 d

/ v* x* n- r- h, K0 d

! V# g3 x' Q& h3 V7 k: c: d6 Y: K

) s8 A- n, N/ T& g8 I7 e, L' KUSB3.0接口,传输线阻抗差分90ohm,±10%! j$ U+ M; ~6 g; ~2 B4 |

iggbyhlcnsu64032199911.png

4 v/ \( Y! u, I p ~

' z7 x0 {9 }3 j. \- F7 n1 W( c; R挖空相邻参考层(如GND或Power平面)的作用:# S* J0 N) C5 {5 U. |9 h

减少寄生电容:去除参考层后,焊盘与平面间的电容减小,补偿因焊盘变厚或TVS管引入的容性负载。( J+ F' c7 L: t

维持阻抗匹配:使信号路径的阻抗尽量接近设计值。

( A3 B& a, z3 Z" F. a# X" [1 z6 g" k- b- w$ Q

为什么挖空尺寸≥焊盘尺寸?电场分布影响:高速信号的电场不仅分布在焊盘正下方,还会向外扩散(边缘场效应)。若挖空区域小于焊盘,参考层边缘仍会引入额外电容。

: _) E5 @$ o, @1 b8 U4 [7 l( r制造公差:PCB加工存在对位误差,挖空稍大可确保覆盖实际焊盘区域。! ]- J- U1 c# j3 |" [8 _

( I+ N4 ^5 v3 D) ~ r. j* A q4 \6 Z

- P- K# m) O- \8 ^" O总结:挖空HDMI焊盘和TVS管下方的参考层,本质是通过控制电场分布来优化阻抗连续性,是高速信号完整性的关键设计手段。4 B1 W. H4 ~: z, v0 f5 x( h

" D7 K; F2 p9 y% ^7 D( w4 Z5 n3 u9 V. Y8 ]/ s

参考内容:

% i9 ?' y- I( mhttps://support.huawei.com/enterprise/zh/doc/EDOC1100304822/16ac287

6 J/ B- q. v! o1 E0 R3 z% r

+ n. W. a' A7 j7 w+ M' J2 P& Z如果这篇文章对你有帮助,别忘了点赞、收藏,并分享给更多需要的人!; Z* F" g) X' C; R! d1 F* M

1 b' u5 \4 j" F( P; f. @写在最后都说硬件工程师越老越吃香,这句话也告诉我们硬件也是需要积累的,王工从事硬件多年,也会不定期分享技术好文,感兴趣的同学可以加微信,或后台回复“加群”,管理员拉你加入同行技术交流群。

6 ^& _0 O$ H1 Q- F: ]& j9 Z推荐阅读(点击图片直接进入)# {5 f) f) N8 {: y/ a0 d0 h

ex3iswkv5sl64032200011.png

W0 Z, E' `3 n

be5yrvu313w64032200111.png

, Y* c5 r$ E ]* i! i3 u8 \5 w投稿/招聘/推广/宣传/技术咨询 请加微信:woniu26a

' Y7 D' t6 n2 I8 b

liresxrw5ce64032200211.jpg

( |1 b! j/ D) p- l! b

2lbvx3mfgbz64032200311.jpg

/ ?* `% _" Z# r' y3 }

/ ?* `% _" Z# r' y3 }

声明: Y8 y5 c' B. _$ ]# L

声明:原创文章,转载请注明出处。本号对所有原创、转载文章的陈述与观点均保持中立,推送文章仅供读者学习和交流。文章、图片等版权归原作者享有,如有侵权,联系删除。推荐阅读▼, B* @' n. F: e" @- N+ u: i$ F5 x

电路设计-电路分析' |1 e% u8 b2 v

emc相关文章

' u! H3 _! c, T电子元器件! J* _$ O0 A& a' W9 p

|