|

|

引言

1 t4 l2 @% p. q4 d随着现代数据中心对数据吞吐量要求不断提高,需要能够处理超过100 Gb/s数据速率的先进收发器技术。基于DSP的PAM-4收发器在保持功率效率的同时,能够在复杂信道条件下提供优异性能。本文探讨了在先进FinFET工艺节点中实现的基于DSP的PAM-4收发器的架构和关键设计考虑因素[1]。1 a; D: v+ y+ Q

x4y31yo0kxt6409157726.png

* \5 j# ]2 B; W4 U

( F4 B* s7 t& t/ ~. V. r15 W9 f" u/ k8 o# u7 O1 ~' T

发送器架构8 A* {* J9 X J' y# G3 \

发送器设计在实现可靠的高速数据传输中发挥着基础作用。让我们来分析现代发送器架构中的关键组件和创新。) a+ H& x7 k4 X3 F1 Z, ]

jizt0ihk1rn6409157826.png

- m) }0 Y S f( z6 w6 [5 C3 B

- m) }0 Y S f( z6 w6 [5 C3 B

图1:112-Gb/s发送器架构框图,展示了TX DPLL、脉冲生成器和驱动级等各个组件的集成。0 {9 S8 D9 N& t1 J$ `( k0 A/ R

! D3 E5 G* L' u$ `& t

发送器每个通道都采用专用的分数频率数字锁相环(DPLL),支持灵活的数据速率和通道交换功能。DPLL生成14-GHz时钟信号,输入到采用数字控制延迟线实现的IQ生成电路。产生的四相输出通过脉冲生成器转换为非重叠时钟,驱动4:1高速多路复用器(HSMUX)。+ K1 D |$ O5 m! X

6 L# O) r3 o: ` X# L2

8 f; b" G# G9 s5 r: b时钟偏差检测与补偿

6 y# `1 y; \' y0 u$ r- M

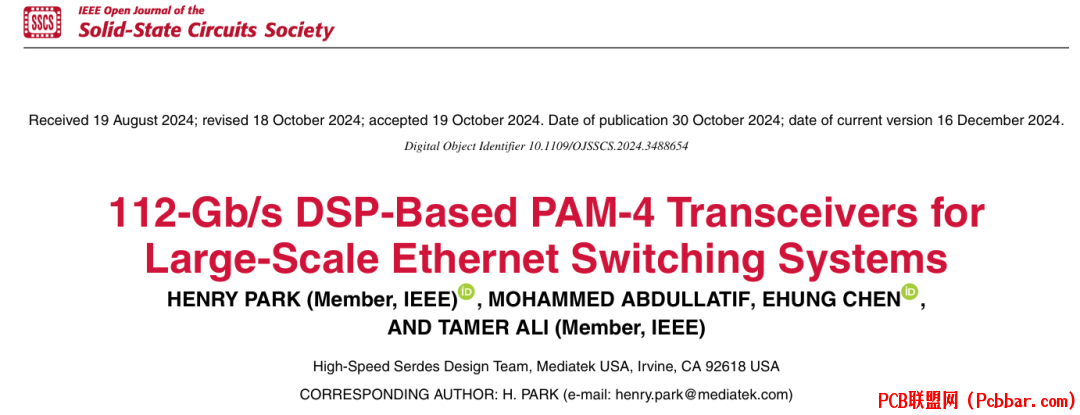

gayegpvtk4h6409157926.png

$ F2 O* r, O; s, V7 V% B9 C# E图2:用于时钟偏差检测的复制MUX实现,显示了精确相位对齐的时序图和控制表。; Q/ j6 j: K6 H. k

* N6 a+ d0 Z+ B5 l4 z

高速发送器设计中,管理时钟相位偏差是一个关键方面。系统采用基于复制MUX的检测方案,将时序信息转换为误差电压。这种方法最大限度地减少了器件失配效应,提供了准确的时钟相位间偏差检测。

4 \0 P; y. w5 u$ q9 H/ Y3 S8 V8 M# N# d7 Y

3

5 E- Z5 L6 i8 ^5 Z i数据相关抖动管理

T- g8 {# ~# Z4 U4 q2 b K- ~

iijesdkmngf6409158026.png

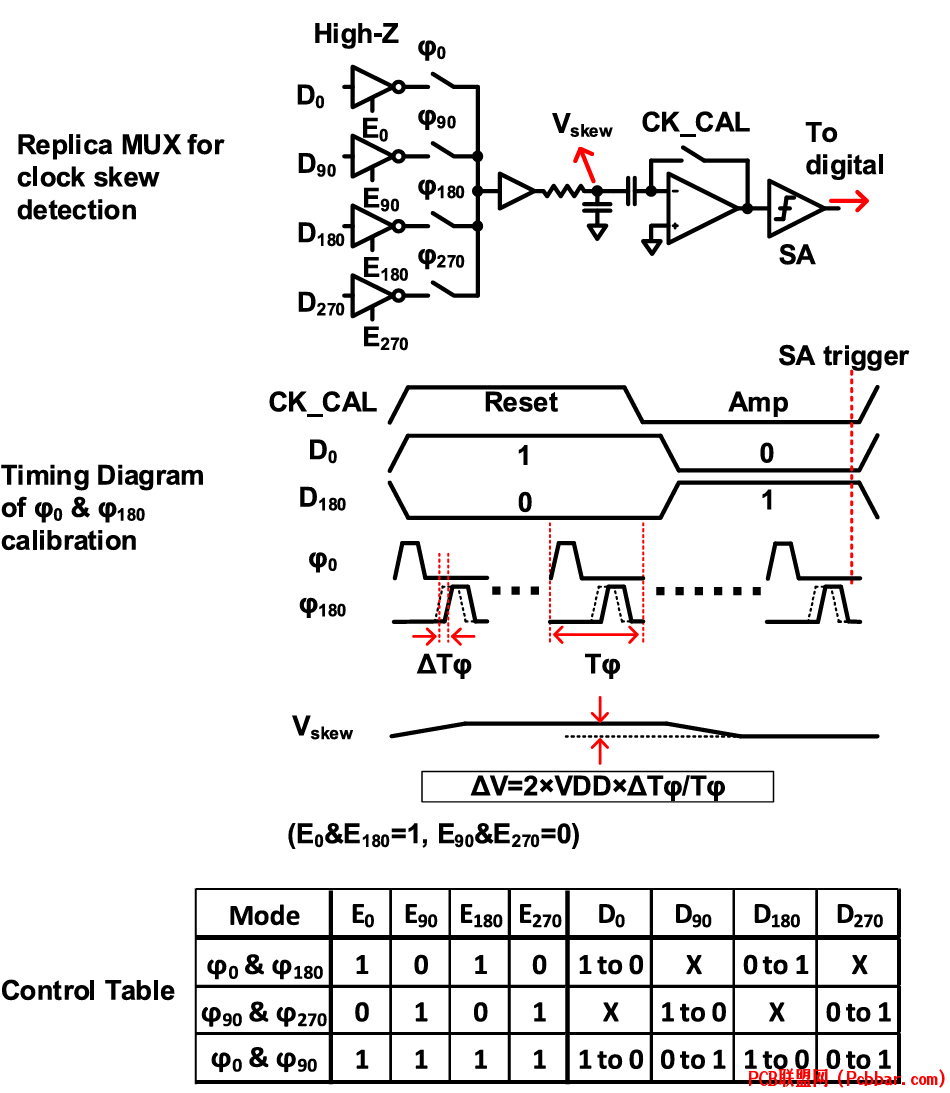

B2 e9 y7 n0 B D4 ^! W8 {9 k图3:TX动态非线性分析,包括DDJ建模及其对信号质量的影响,展示了DDJ与SNDR之间的关系。

. M; [$ S" ?2 y0 m- [

0 B4 n9 M: c: }数据相关抖动(DDJ)对发送器性能有显著影响。该设计在7位DAC实现中包含了复杂的DDJ效应建模。仔细分析了DDJ与信噪比失真比(SNDR)之间的关系,以优化发送器性能。# J, @: U9 ?* U

6 X! d* y1 u3 o4 L4

8 n& J- b1 R! `& f先进发送器实现

/ @+ P, I& @' ^* A, k

xjhqzbjy0r26409158126.png

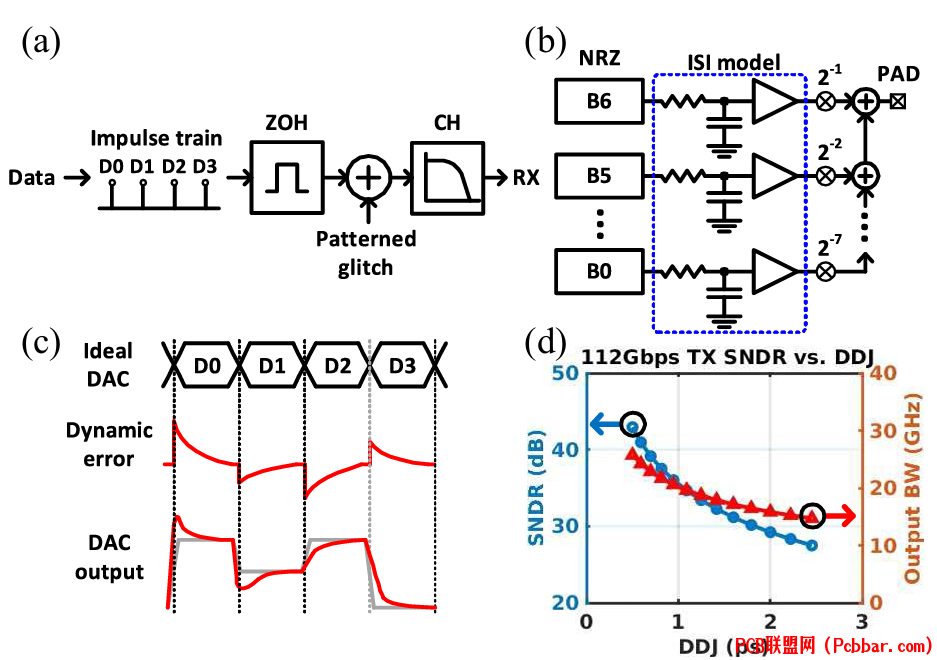

2 F/ U/ U! Y* m. a9 s& l2 W2 [, }图4:7nm TX架构的详细实现,展示了带尺寸优化的反馈均衡器和前驱动器配置。

1 k3 S4 k9 W/ \0 W8 z; x7 o: z! j, V$ [/ `

发送器实现了创新的反馈均衡器系统,以扩展带宽并提高信号质量。设计通过多个级联逐步缩小尺寸,在保持信号完整性的同时优化功耗。4 Q8 E0 S1 c2 J3 `4 V* v" f

( h/ e' Z. ]6 @: K+ D- F

5

# ^$ b/ _$ c0 e5 U! S9 i接收器架构与挑战

D0 j: `6 t% V7 l) I, `

h1n4qjzoa1l6409158226.png

6 o2 Z: V' `" ], F* n0 [

6 o2 Z: V' `" ], F* n0 [

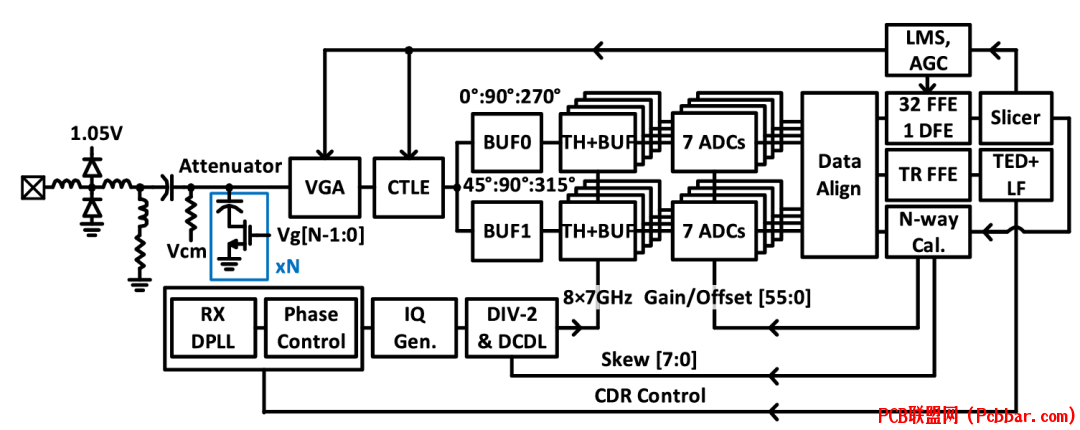

图5:112-Gb/s接收器的完整框图,显示了从输入网络到DSP处理的信号路径。

" Y. g) {8 W) e- u8 r/ J3 W" X& \, z8 w

接收器架构包含多个复杂特性,以有效处理高速信号。T形线圈和并联峰值网络优化输入级,后接可变增益放大器(VGA)和连续时间线性均衡器(CTLE)。设计采用工作在7 GHz的8路交错采样保持系统。. g& H M; E. d9 v, h, i6 y6 @. |

% Z {' E% M, y& U) `$ R6% [) m" K7 V. F) A

电源噪声管理( W5 _2 a8 b- S z. J

rlf3fsdloby6409158326.png

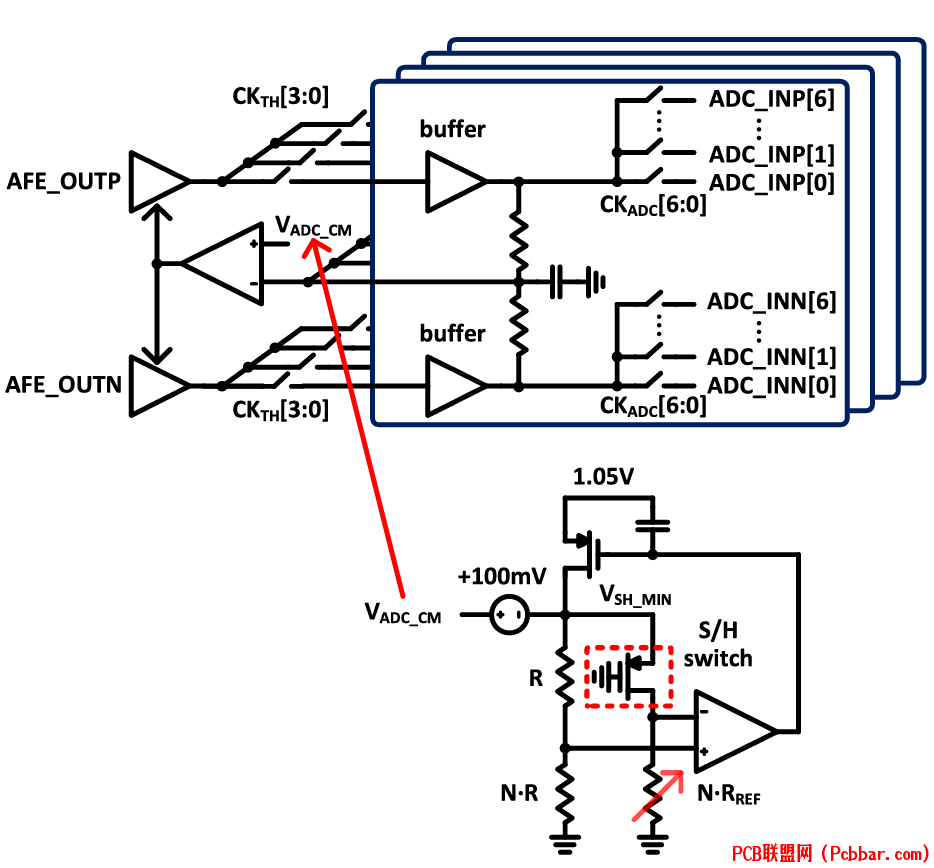

& } k6 [2 j6 x- V9 c- B图6:数据路径CMFB线路实现,具有自适应VADC_CM生成器,可在不同电源条件下稳定工作。

- c! K$ Q( o, K; T' P. v) M1 A( `& D2 _$ X1 Y$ m. l

电源噪声在大规模集成中是一个重大挑战。该设计采用了具有复杂偏置生成的自适应共模反馈系统,以在不同工作条件下保持稳定运行。

" t$ ~( T' b6 l2 r

* Y% P0 D- R/ E' n7+ M$ L8 E, n6 Q% p( S7 s

数字锁相环架构

( f2 Q3 j$ a+ B6 d

xq5viluvluv6409158426.png

, c- ]: C. F3 f- L8 m

, c- ]: C. F3 f- L8 m

图7:DPLL框图,显示了TDC校准、数字环路滤波器和正交生成组件的集成。

2 X R! R5 O6 ^/ @- ]. E+ O; F+ u0 {- Z* q0 T `( s: V

数字锁相环实现为现代收发器需求提供了灵活的时钟解决方案。该架构包括TDC校准和优化的环路滤波等先进特性,可实现优异的相位噪声性能。( O$ u& i, [, N* v0 B g

0 v' H3 k2 s; G, ?7 p* d

8) {% y; Q( [0 l) F. c

性能结果

! q% c& S7 E( y! D* @

ffjuu5khrd36409158526.png

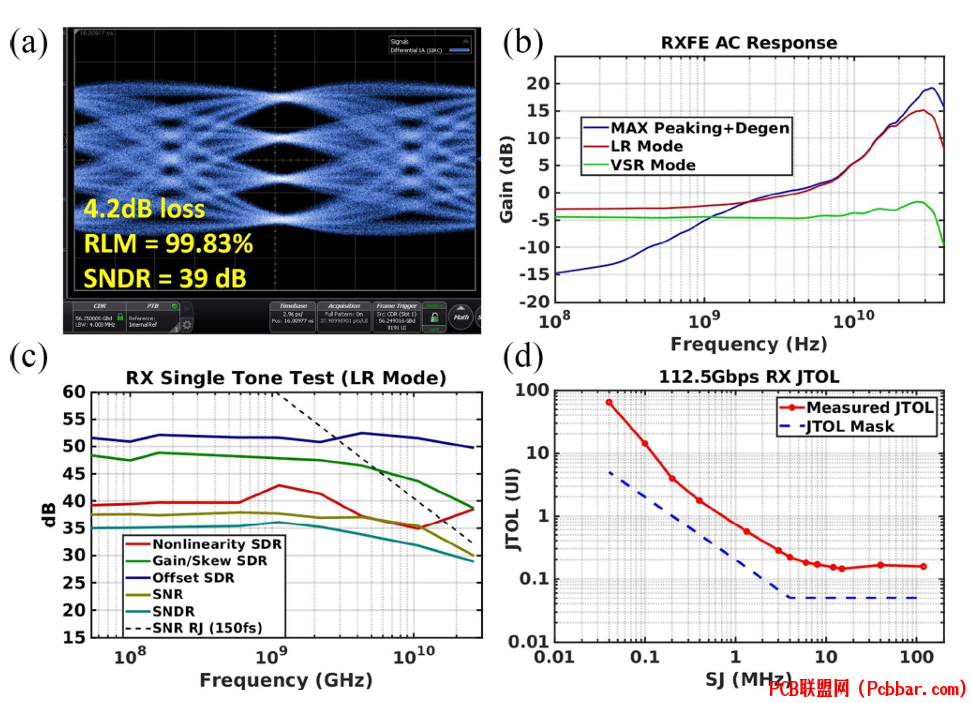

( D5 |: @# v7 S- w: x图8:全面的性能图,显示TX/RX特性,包括眼图、频率响应和抖动容限测量。) m6 L' M! y% |& `: @$ d

- v2 v$ Y0 M; d" \

测量结果证明了所实现架构的有效性。收发器实现了令人印象深刻的性能指标,包括在各种信道条件下的稳健运行和优秀的信号完整性特性。8 j; o5 \. P. Y! u& w) h' B

& H6 H- u) N' M7 J- l+ `6 L; `9

7 L0 Y3 R; o- C3 ~* p ^/ q( c系统集成与缩放

! W3 |1 z) u h0 z9 f& ]2 i2 L

r4eozwylzuc6409158626.png

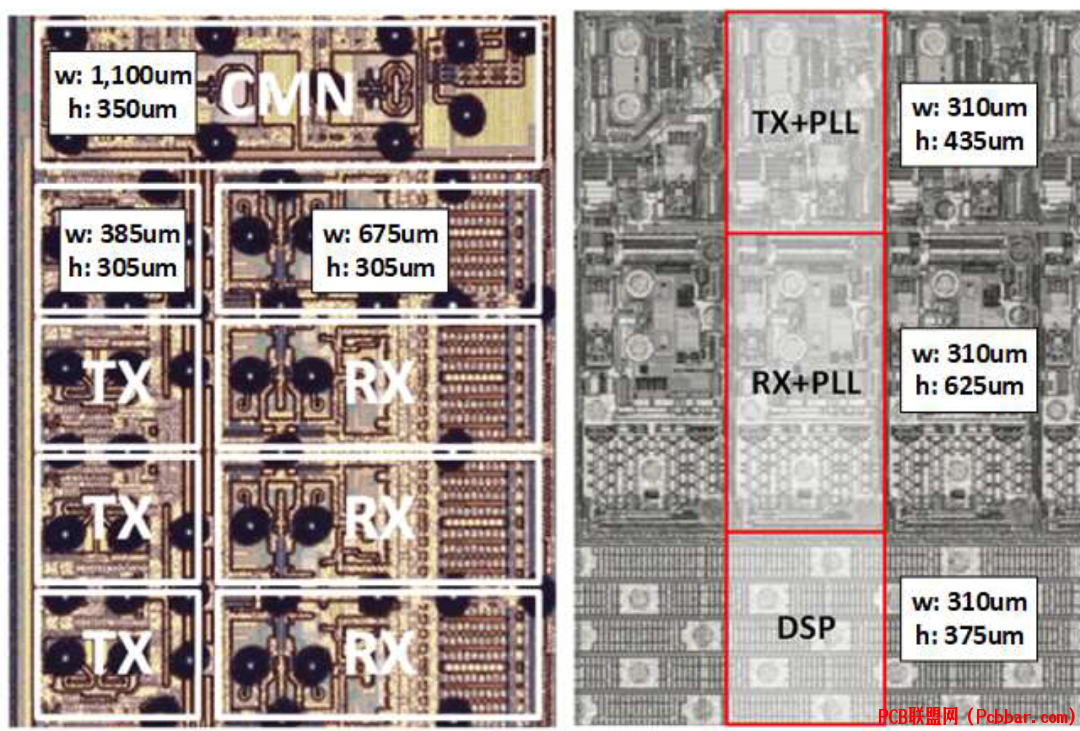

2 J/ }$ Y1 M0 x图9:7nm和5nm收发器实现的芯片照片对比,展示了集成密度的演进。

# k# V- O* {+ d9 ]

4 u! |) f {1 [ i# B这些设计已在7nm和5nm工艺节点上成功实现,展示了优秀的缩放特性,在减少功耗和面积的同时保持高性能。

0 n" Z* Y) S: d, P' B/ _

5 Y: H6 V! C* n X ~0 j10

* c; c4 e8 K1 I. H结论: Y0 Z4 [& N. s* Y

基于DSP的PAM-4收发器技术持续发展,推动高速数据通信的技术进步。数字和模拟技术的复杂集成,结合先进工艺节点,使这些系统能够满足现代数据中心不断增长的需求,同时保持功率效率和信号完整性。3 D. l* ]+ [# Z7 H+ u0 D

: d8 n& O9 Z4 C# Q! e6 H* [% ~

参考文献' n. P: X* M9 x) j9 T! E

[1] H. Park, M. Abdullatif, E. Chen and T. Ali, "112-Gb/s DSP-Based PAM-4 Transceivers for Large-Scale Ethernet Switching Systems," IEEE Open Journal of the Solid-State Circuits Society, vol. 4, pp. 277-289, 2024, doi: 10.1109/OJSSCS.2024.3488654.

# s" l2 g- R3 S9 Y w# E/ p: C: \, j& CEND

. V0 n- W. T/ T" x! g

# f1 z% G0 z5 |: i软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。

* m6 Z. p! Q7 }5 A/ L点击左下角"阅读原文"马上申请 l% f; W6 j6 J( A' v8 K

|7 b$ y2 O n% [5 o

欢迎转载

6 A J1 b& O# a7 h+ G

6 k6 [* c+ M" p5 ^# I+ P o' S, f- D' S转载请注明出处,请勿修改内容和删除作者信息!% f' A& M+ n% G8 ?2 I$ M

w' a1 ]; l. I5 T

* v. e( c* c; v7 H o2 A

0 G* [% Z9 R1 \" C; x# U' m9 Q

gs2o1igue0x6409158726.gif

0 F% h0 S Q& R C3 ~& d4 [. n4 K x+ u [. Q7 c! ]

关注我们3 l r5 l+ i! }4 h4 s) Q' t, `+ B# X

& }& A2 [! ]0 R2 ?

4 d& d) E/ c( A; R

knxespmi0wx6409158826.png

' }& E: E$ b! o | # h; Z7 ?5 y8 K. _3 p5 U

3sh0aqodzgl6409158926.png

. ]2 R: |$ u' _) j; c3 f

. ]2 R: |$ u' _) j; c3 f

|

6 l/ ]7 K9 |9 n) i9 `

ctuyoua3c026409159026.png

$ X2 }; S, U' L6 x8 Q- b

$ X2 }; S, U' L6 x8 Q- b

|

, o& C, t& D: }3 {6 S

3 h: A! l) x0 r! O, @( @- S0 } z/ H8 M- Q5 |. i

( p4 i* u3 I% C [

关于我们:

2 g" i, p# j5 t9 M7 \深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。7 [: N, U* b6 _; ]& ^5 @, b R

2 }7 b! o4 D& p

http://www.latitudeda.com// f9 K5 a$ t g$ U- O

(点击上方名片关注我们,发现更多精彩内容) |

|