引言

1 Y- [* [ i0 [) x6 M# j随着摩尔定律接近物理极限,半导体产业正在向2.5D和3D集成电路等新型技术方向发展。在2.5D集成技术中,多个Chiplet通过微凸点、硅通孔和重布线层放置在中介层上。这种架构在异构集成方面具有优势,但同时在Chiplet布局优化和温度管理方面带来了挑战[1]。8 c; z' U, n& _5 Q+ z9 {

qlbbwrss2en6401829458.png

$ s5 O& p/ o4 A) X+ z2 U+ q6 l1 |

$ s5 O& p/ o4 A) X+ z2 U+ q6 l1 |

s13dscwsgzz6401829558.png

4 K* M0 Y5 T2 n& d s图1:2.5D集成电路的分层架构和各种互连组件。$ e8 v- V; t* H

: t+ f7 o6 j8 D. F1" V; \' K2 q: T# N6 C

布局优化框架# v* D( v I% C$ A1 t6 ]) o7 L$ G* Y

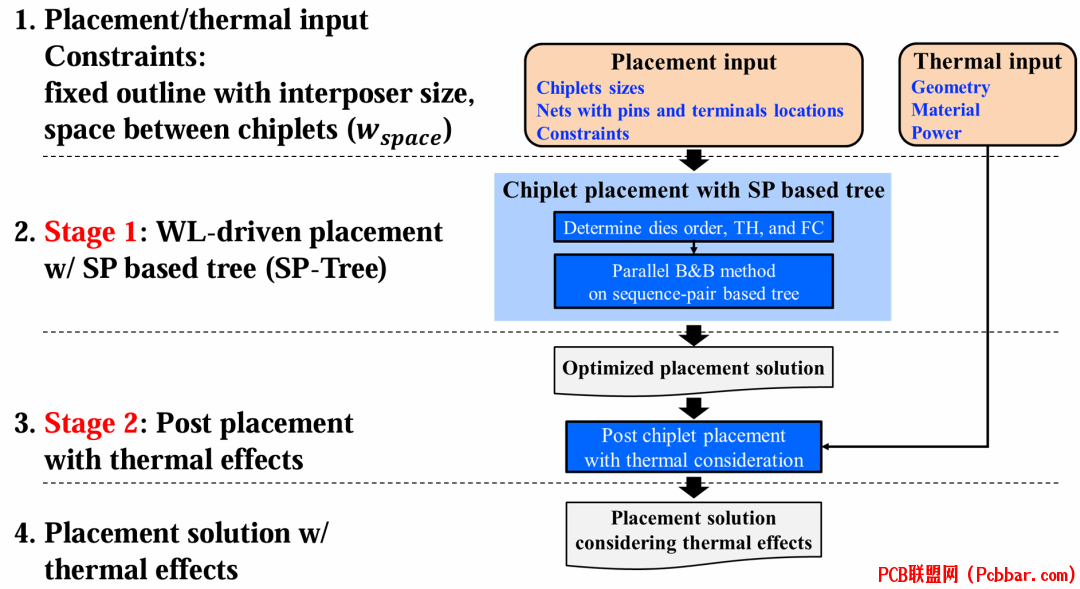

该框架分为两个主要阶段:第一阶段使用基于序列对的树结构(SP-Tree)进行布线长度优化布局;第二阶段进行考虑温度效应的后布局优化。系统首先处理输入约束条件,包括中介层尺寸的固定轮廓要求和Chiplet之间的必要间距。这些约束条件构成了后续优化决策的基础。0 G' x/ x, V( R" T0 x

3t0rkgnubql6401829658.png

. J5 M! N3 }* u' E2 v; S5 ^+ i) n图2:从输入约束到最终解决方案的完整处理流程。

0 T2 k# O% y, D8 q

, [' }! @1 I q/ X# }% ?! V* F2# p5 m/ x$ R* s! |

基于SP-Tree的布局方法: _& M/ Z4 C* T

SP-Tree方法相比之前的CSP-Tree方法有显著改进。其主要优势在于能够高效表示和处理布局方案,同时消除冗余或无效配置。该方法确保生成的所有布局方案都能在物理上实现。6 R$ ]) n6 z1 t5 X: S

9 R8 ?% p; `) {& E

布局过程采用复杂的并行分支定界(B&B)方法。从树的根节点开始,通过深度优先搜索系统地探索潜在解决方案。在此过程中,算法分配旋转节点指定方向(北、南、东、西),并确定Chiplet排列的部分或完整序列对。- V+ G" d0 k$ I6 C

1r24plgqjve6401829758.png

, v* n2 e8 [0 ?8 }! Y6 |

wf3bzbwvcct6401829858.png

( Q- V9 C6 h& [" e% V图3:比较SP-Tree和CSP-Tree结构,展示SP-Tree方法更高效的组织方式。: z1 H. ]2 {" S

) y9 v9 s' o6 u% v3

* [/ e. D3 g) |6 b7 u考虑空白区域的分析优化: d/ D' E+ b" @" }9 R

空白区域优化过程包含四个步骤:

/ l9 z6 X+ D# y1 O$ R1. 首先,系统处理虚拟Chiplet移动,允许在不考虑物理约束的情况下进行初步位置优化。: i g% z8 P# q

8 x5 o3 j6 e8 }2. 其次是单个Chiplet优化,调整各个组件以获得最佳位置。

8 k# x1 }0 n$ m$ B8 J

' A/ O0 C' B; r9 I$ Z3. 第三步引入了固定和自由Chiplet移动策略,某些Chiplet保持静止而其他可以重新定位。

- X) B+ Q5 A% Q. v% e f; ^" V

0 K3 o4 L0 [. ]9 l1 V4. 最后,系统执行多Chiplet组优化,同时考虑多个组件的集体移动。这种分层方法确保了解空间的充分探索。. f9 b) M5 c9 ?

antxhm2me016401829959.png

5 E T% g7 ?; F0 l4 e

5 E T% g7 ?; F0 l4 e

djerssrwi5h6401830059.png

0 w. I# G& k. W/ e3 Y% q

0 w. I# G& k. W/ e3 Y% q

图4:顺序优化步骤展示不同的Chiplet移动和空白区域利用方法。3 L* n% {! ~( B$ L0 L' h

9 `9 Z& U2 u, H3 p4

9 p1 U: P$ y, p4 B1 _- B. y. C7 x后布局温度效应考虑

7 `, ?/ l; I7 f& u3 C% e温度优化阶段采用精密的温度管理方法。系统使用64×64×5网格进行热仿真,提供整个设计的精确温度分布建模。温度计算使用SuperLU 5.3.0矩阵求解器,确保高效和准确的热分析。

. d4 Q+ T6 X, v1 o% O

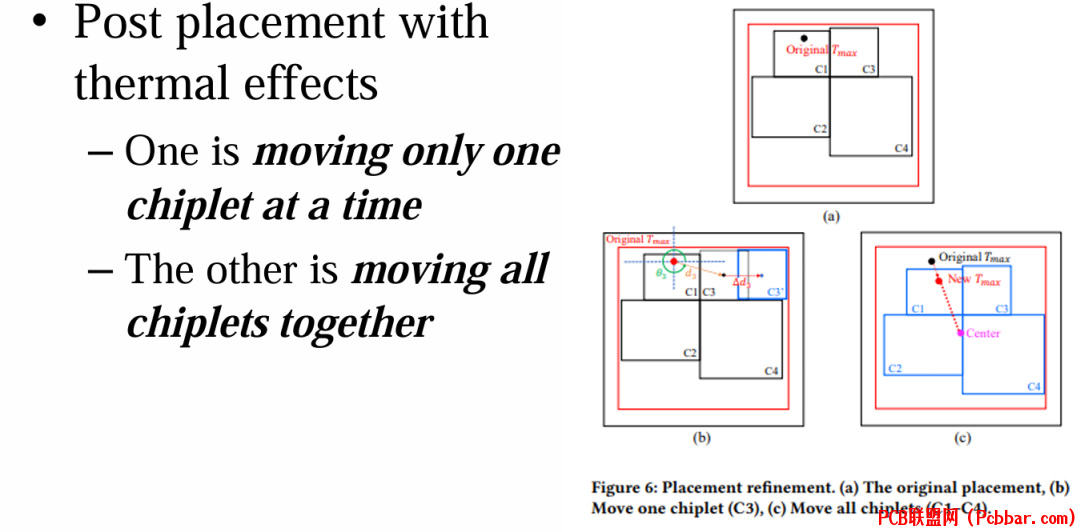

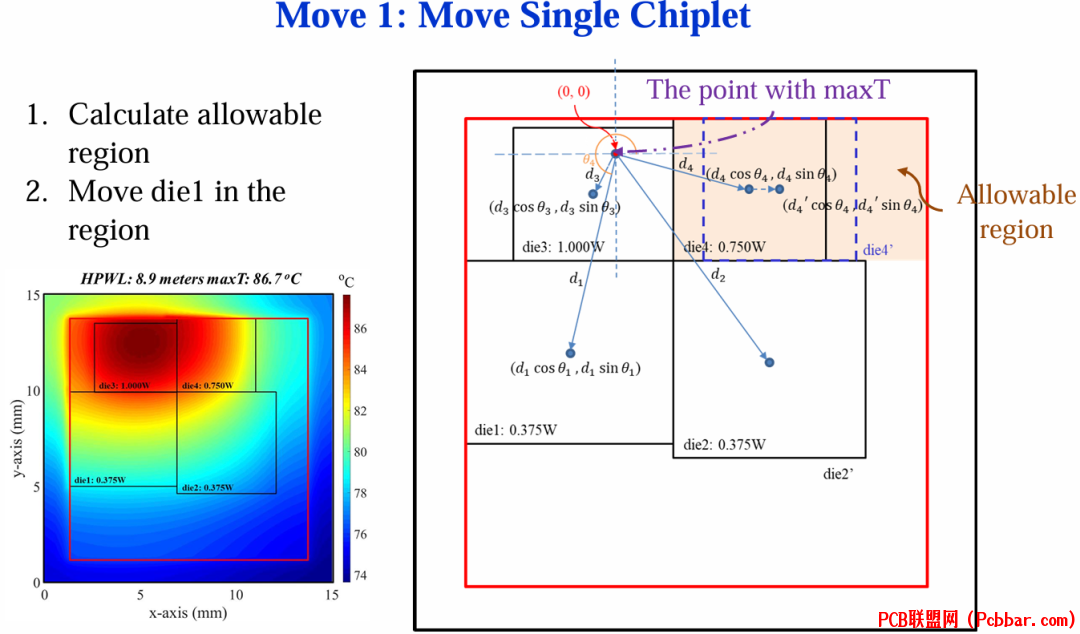

1 c1 s1 ?% H# ^6 y优化过程实施两种不同的移动策略:第一种策略专注于在计算的允许区域内进行单个Chiplet移动,第二种策略考虑整个Chiplet组的协调移动。这些互补方法能够解决局部热点和整体温度分布模式。

8 P2 t3 I# K4 e& B+ R7 J7 z

0hhyv5qivv46401830159.png

6 N. V1 S$ h. {+ F. M1 r

jdlmyqzy5ce6401830259.png

- t, x9 g' u0 S1 ?! p

- t, x9 g' u0 S1 ?! p

图5:展示单个Chiplet和整体布局组移动策略的热优化方法。. ]. W! N3 }" }; c

2 j* s$ O$ W3 j+ G& W5 z" ?

5

/ { }! J: P3 [/ g% ?实验结果- W# Q1 }/ B% [0 F; J g$ A

使用C/C++在配备Intel Xeon处理器的Linux工作站上进行实现测试。结果显示在性能指标和处理效率方面都有显著提升。在布线长度优化方面,系统相比现有方法实现了高达1.035%的总布线长度改进,同时处理速度提高了156倍。

7 P$ a5 y& s' V' [5 |. ~& X

3 p+ D) I S: a! V; [+ M温度性能结果同样显著,在保持合理布线长度指标的同时,实现了高达8.214°C的温度降低。在大多数测试案例中,系统成功满足了85°C的温度约束,仅需要5.376%的平均布线长度增加即可实现温度合规。

9 N- |$ y1 l5 w5 l7 ~/ j% N

1ctznwdeznh6401830300.png

, H. R8 O0 y E! q' ~

, H. R8 O0 y E! q' ~

图6:温度分布图展示不同布局配置下的温度改进情况。! l9 j- p* B9 @: T

" o7 V0 V0 e5 n

6

/ r7 G' H( n) ~/ o1 q2 M结论* x5 B1 L; c3 P4 O6 `6 u

基于SP-Tree的布局方法结合温度考虑,代表了2.5D集成电路设计方法的重要进展。该框架成功结合了高效的组合搜索技术和实用的温度管理策略,形成了理论完善且实用的解决方案。( x1 R2 q0 C; e, T# D

$ \" z* q$ I2 q4 F U# R该系统在处理约十个或更少Chiplet的设计时表现特别出色,这与当前工业需求高度吻合。通过有效平衡布线长度优化和温度约束,该框架为现代2.5D集成电路实现提供了全面的解决方案。# F& O1 K- V% W( F9 p

9 f+ t" N$ M9 h- M0 O' x参考文献9 o1 k0 h2 t, T' |

[1] H.-W. Chiou, J.-H. Jiang, Y.-T. Chang, Y.-M. Lee, and C.-W. Pan, "Chiplet Placement for 2.5D IC with Sequence Pair Based Tree and Thermal Consideration," National Yang Ming Chiao Tung University, Jan. 17, 2023.

9 c4 p2 l& K, |4 sEND

+ c8 J7 b5 T$ `( N4 o/ l# o0 I' F( Z. Z U2 b

软件申请我们欢迎化合物/硅基光电子芯片的研究人员和工程师申请体验免费版PIC Studio软件。无论是研究还是商业应用,PIC Studio都可提升您的工作效能。

6 i! u- Z& X! I" V点击左下角"阅读原文"马上申请

, I) e8 y4 n* g: h' ~4 X, _' |4 g, |

* E' v/ S! e: r, `, d+ z6 q欢迎转载/ T% t0 }4 t2 u$ Q# k F( I

# I' n$ q X5 D; d' T% x) `( g

转载请注明出处,请勿修改内容和删除作者信息!

! T) n; |1 f8 h: d) Q! \, J5 }' R! U% D. M7 b

* S/ @0 r7 Y" U0 n

' j8 t. D" k0 `

i50ibcoqlit6401830400.gif

+ e1 \ Z; k" y" P( _/ D" M

+ e1 \ Z; k" y" P( _/ D" M

) J9 n7 m+ R* C3 f6 F! v. o, f0 B

关注我们% ?$ V: a# |7 Z

t7 Y# M- ]+ L; H

# M, i* I6 d( Q$ B9 e

kuga5pbw3506401830500.png

% X3 b3 w+ {6 ~8 ^3 M: Z | 7 |2 x7 `2 B1 O1 x$ g \

3xgorq2xpcu6401830600.png

# D3 e, m: Y8 H- W9 ]

# D3 e, m: Y8 H- W9 ]

|

$ ?& q. ?. y' p @9 g8 E

0ehqqdggurj6401830700.png

- J4 X$ M9 F }! P$ ^9 y |

( J- L9 r1 H( J( K+ K% ~

; M7 a8 {. x% C! P

" |, e+ j2 r8 y

8 q; t! ^$ A" ]8 t

关于我们:' w6 q1 R3 k' X4 T* @

深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

7 k/ A; H5 W. N' ]2 O/ o

8 H3 M; `2 p7 L* D. R zhttp://www.latitudeda.com/

4 T* o* U/ y1 b5 F! I(点击上方名片关注我们,发现更多精彩内容) |