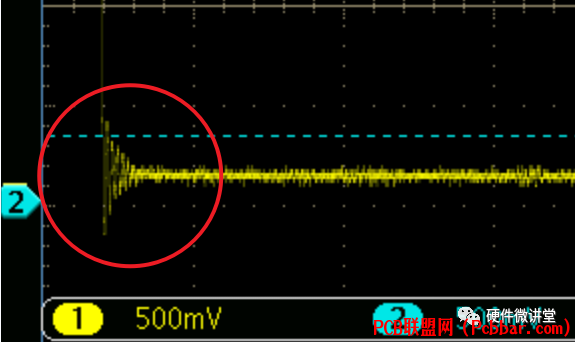

前两天做测试,碰到下图这样的波形。其实,在信号线或者开关波形上,经常会有类似振铃出现,不晓得你有没有思考过为什么。今天我们就在这里聊一聊振铃。

/ ?- g& \5 y6 |6 K$ q! ~1 |1 f0 {

omndpoq125b64018681742.png

$ g! `- U% p, e3 r

$ g! `- U% p, e3 r

( i! i" k: W( Q$ d: N

8 w7 d! N) j) |4 `; O0 F# z

一道面试题

( K$ m+ F2 G: o% v: Z( X9 U* t6 k9 ?5 U

照例,先抛出来一道面试“信号的振铃有没有遇到过?有考虑过为什么吗?” 怎么样?看似随口一说的问题,但往往暗藏玄机。1 D3 u& f0 P9 k1 V

) }. _$ M* A5 e# a. Z7 m

自我感觉良好的答案( {0 |4 ]0 T+ ] }

$ L) Z4 W/ m) J; U8 ~! Y4 `

有些小伙伴会觉得:这个问题简单,当然不在话下。信号出现振铃,当然是信号反射,是阻抗不连续导致的!

7 a; v1 I1 z% W' C6 S8 V当然,这个答案绝对没问题,但只能说是中规中矩,并无特色。那么你的得分也不会和别人有什么差别。而面试官凭什么要给你pass呢?# E' Z. p5 V3 ]& j0 Y$ P" B

上面是从传输线理论维度出发,估计有个几年研发经验的小伙伴都能想到。如果你能另辟蹊径,从不一样的角度给出不一样的解释,那special offer估计就在向你招手了。

* h. F; g+ K& l {& k# ?# N7 U' E

不一样的维度6 c7 J+ M7 B0 T+ L

# C5 R* }" `9 {$ f U振铃多出现在数字电路的信号跳变的边沿处,从0到1,从1到0。比如文章开头的波形图片,就是从1到0切换时发生振铃。

' g. w8 u# f0 N+ g. q. I4 V2 A( h那为什么总是在电平切换时发生?- n" P6 I. B, Q+ f3 @/ D" k3 n

数字信号在电平状态切换时,陡峭的上升沿或下降沿,其中蕴含了非常丰富的频率分量,而且带宽极宽,频率覆盖范围很宽。这个,如果你学过信号与系统 或 研究过傅里叶变换,都会比较清楚。

+ P5 }- g; g, r# Z/ ]. p当然,仅仅是频率范围宽并不会发生振铃。

' \6 j4 C% u) U% }# z9 u/ ^但关键是,数字信号电路都是通过PCB导线、芯片IC、阻容感等电路搭起来的。读过我前面文章的小伙伴应该知道:PCB板上的layout走线,一般都会有寄生电感,nH级,而芯片端IO管脚也会有寄生电容,pf级。

, d: C5 _3 h* @! N电路中有了L和C,可能会发生什么?

( w# _! A- m" W1 l) u7 QLC谐振! q7 e! d9 ^+ ]0 `: k W% B) e

! I$ O1 f# ^. [6 }. a+ Q' p) ~8 H) f发生谐振会怎样?- M6 L5 j% ?4 g4 W

选频特性,会使谐振点上的频率分量放大,而且是很多倍!再和原来的信号做叠加,就形成了振铃。1 e% r r x" c' d( M! W

只是文字描述,你可能不太信服,那咱们仿真看看哈……

% e, t. m! K# ^- F' k. j7 z- \6 \$ G. S

仿真分析

3 G! `% m+ v% G# H* }- W) h1 {9 a5 h/ z/ E

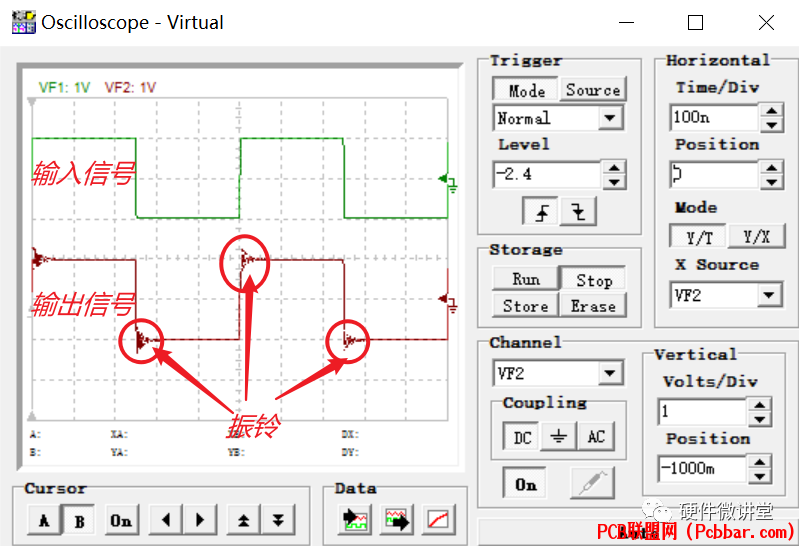

根据经验值,1cm的PCB 走线,寄生电感大概为10nH。而芯片点输入端的寄生电容,姑且按5pf来估算(并不是很严谨)。如此,我们把数字电路发送和接收的模型搭建如下图所示。VG1为数字电路发送的激励源,设置为频率2MHz的方波。

+ l1 T/ N$ d: r$ ]+ |" a5 _) L- Q& {$ a2 z2 n0 k9 V

p0ih3pob4es64018681842.png

. B& U2 w) U$ l/ j; g

. B& U2 w) U$ l/ j; g

$ d2 C$ d/ K" K/ B t% q5 s# I: F用示波器看下波形,如下图,输出信号画圈的部分,明显可以看出有“振铃”。

6 w1 n) v" w1 a/ U4 ?; @5 e$ X7 @+ O5 g8 q

xufs3kibido64018681942.png

8 P& N% ?; D6 p& w9 r9 ^9 P/ Y( ~. ]

4 x! e ]2 q# p7 @) A! j把时基从100ns调整到5ns,波形放大,如下图,可以看到明显的振铃波形。

. K( R! | D1 J9 w- H8 D- ^2 a+ j4 W, z; I5 E' @

co1rk41b3bd64018682042.png

% p5 `' ?) w9 [, z+ y) i" |$ c. W9 \! x/ e

当然,如果仅仅分析到这里,那只能说是有振铃出现,并没有找到我们想要的原因。浅尝辄止?不是我的调性。继续把波形放大哈…

8 D3 H# T4 x, z! w% y1 |: Y1 N! h

capac02aiab64018682142.png

% B( ~7 ]9 u3 F! ]& s

% B( ~7 ]9 u3 F! ]& s

/ t! C" f* K3 j+ l( {) o

继续放大波形,可以看到振铃波形呈现为一定周期的阻尼振荡。用光标卡一下时间,Xa=5.83ns,Xb=4.34ns,dX=1.5ns,由此可以计算阻尼振荡的周期f。7 B: L5 W; q. _3 Z4 G3 u

f=1/dX=666MHz

9 K& X" X: R' P

) c% ?! s8 B2 D* [6 A2 R( l3 c666MHz,是什么?不晓得,继续往下分析。

9 B0 A. E( _# X0 N$ V. W6 {* B1 t3 k3 `6 l* y0 h

ohjnmzpgjxa64018682242.png

' r5 l7 W& ^7 x8 _$ @: m

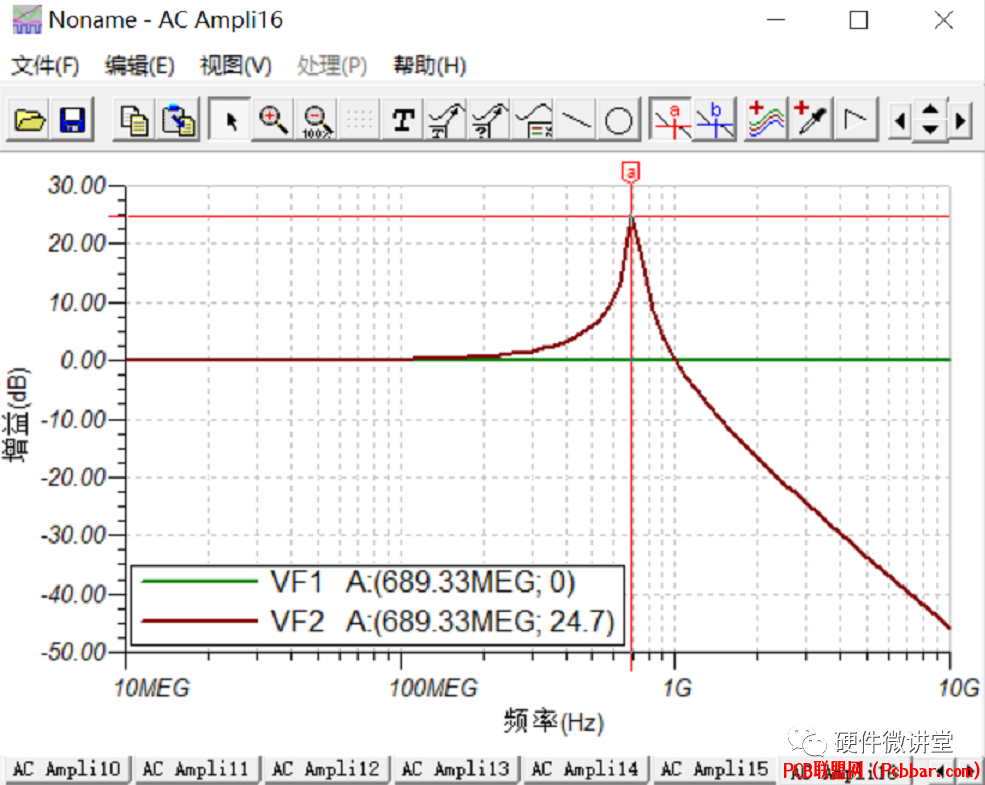

% i6 z3 e$ }# m8 v% `' e1 R7 @# [/ s我们用交流分析看下这个电路的频率增益曲线,发现高频处有谐振点,谐振频率为689MHz,接近666MHz!) r0 P3 d# l3 c* U3 \( P; H

说明LC有发生串联谐振,并在该电路中充分展示了LC谐振的选频特性,把基频2MHz的666MHz的高次谐波分量选出并进行(将近)24dB的放大,再和原来的基波叠加,在输出信号上体现出振铃波形。

- R7 P4 ]7 y( k! d$ ^; q6 n3 s说到这里,再回过头看看前面说的:' i |/ l2 `7 _3 H

①总在信号电平状态切换时发生;6 i! w0 D2 m: ]3 i( m5 b& y d! V

②频率覆盖范围很宽;8 o( J, k }2 G- p. N- n* }

③寄生电感和寄生电容;- S2 q l; `8 V( S1 [

④LC谐振,0 g% b& R$ R% R: b8 _+ Q

⑤选频放大特性,9 y8 k4 M$ L' |- H1 P

把这些都串在一起,理论分析结合仿真数据,这个问题是不是就很清晰了?( q8 q6 { U$ w: U e1 k

/ _" G( x7 V! ^4 @! @- V# s7 M总结% Q, B) d- I$ ?- [ }$ }" N( R

9 d' f7 \& z3 ^( _& ]2 j( f信号出现振铃,为什么?

9 n8 x% E8 q8 V2 y, ^维度1:从传输线理论维度,信号反射,是阻抗不连续导致的!# S1 s2 @5 @9 t, ]

维度2:从LC谐振维度,LC有发生串联谐振,LC谐振的选频特性将信号状态切换时的高次谐波频率分量选出并放大,叠加到基波上进而形成振铃。

+ q/ w6 f1 p& L8 l) ]. V; ^, J. X0 ]" v0 H) Z

这里另外抛出两个附加题:9 c5 q7 R, T7 g$ M2 J# `

问题一:为什么是这个666MHz的高次(333次)谐波,那670M(335次),674M(337次)等其它高次谐波呢?

1 P! G% F7 D8 F, u K: M3 {! f) p; B0 q问题二:振铃波形为什么越来越小,呈阻尼趋势呢? |