" 本文介绍了 KiCad 9 开发周期中重要的功能更新。感兴趣的小伙伴可以下载 8.99 的 Test Build 尝鲜。另外,KiCon Asia 2024 将在深圳举行(11月15~16日),支持 KiCad 的小伙伴有机会当面和 KiCad 的开发者和资深用户当面交流了!官网链接:https://kicon.kicad.org/asia2024/zh-cn/"

8 |5 b a0 o- m) G

' p, k) \& K9 `6 i" |

xtchbhjik3d64013502435.png

& r' g9 V4 g; _

& r' g9 V4 g; _

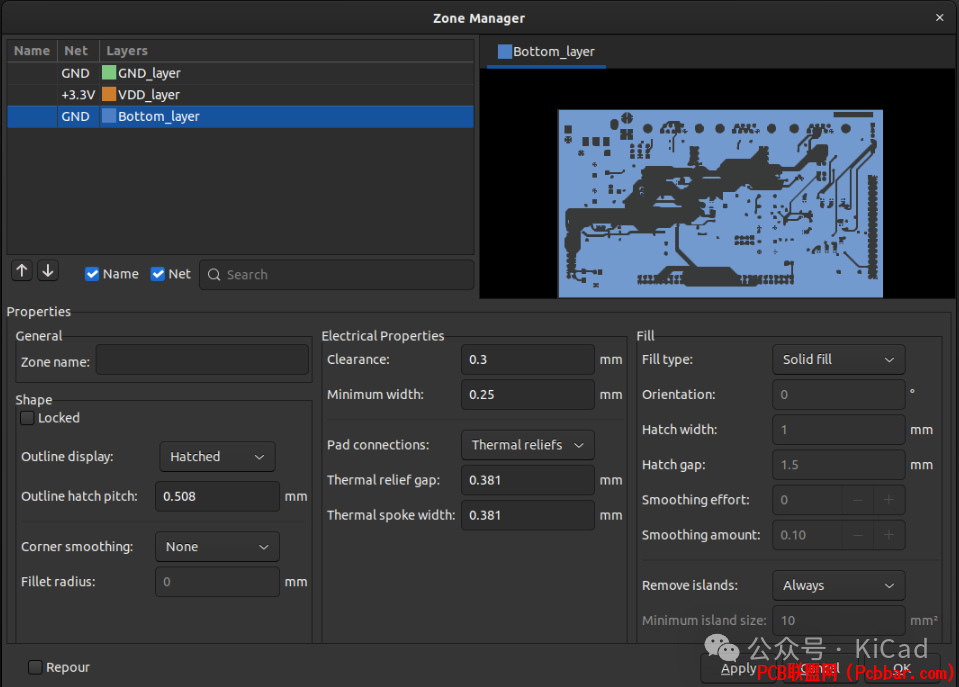

+ z9 w( z' ?: Q& E. x# I4 S0 Y敷铜管理器由华秋电子的 Ethan Chien 贡献。可以在敷铜管理器(Zone Manager)中查看所有的敷铜,并修改其属性及优先级。

9 u/ y2 x# r0 U E7 e* K' r" N6 ~4 T5 k

ndkofly1eig64013502535.png

# a' B$ j+ u1 [1 r& N j

# a' B$ j+ u1 [1 r& N j

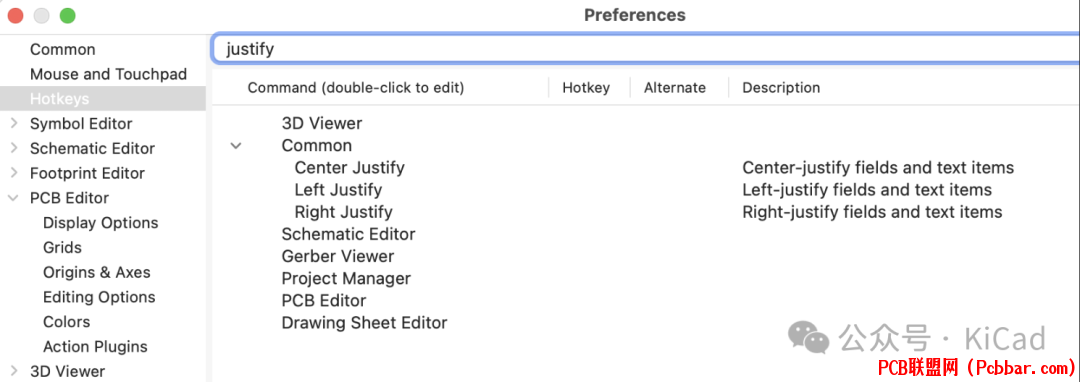

添加文本对齐操作

6 r8 b" N5 C' f' O7 z由 Jeff 大佬贡献。可以为文本对齐操作设置快捷键。

+ S' {7 y: g$ H

raj3micwehg64013502635.png

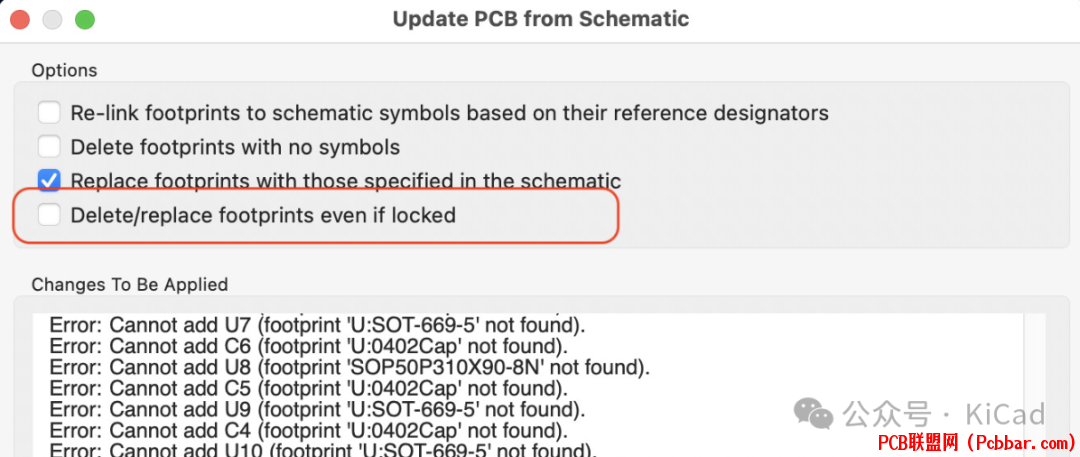

8 F7 B" m" U4 u( h( ?更新PCB时允许删除锁定封装

8 ]% l u0 r, K# }. I, H( b4 M由 Jeff 大佬贡献。可以在原理图更新到PCB时选择删除或替换锁定的封装。

) v* j* f/ I7 M

5lq1eyttp4y64013502735.png

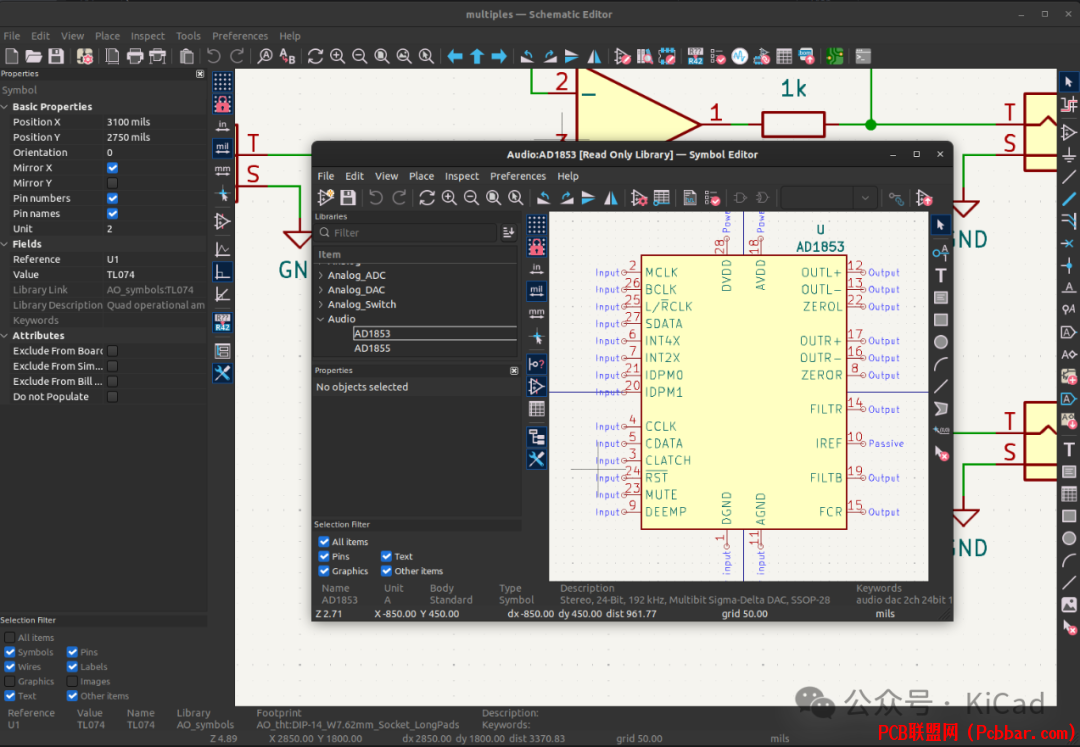

5 _$ {3 Y6 x: i! J, H# p4 b2 C' q全部展开/收起

1 W' c' d4 J7 [6 j/ C由 Jeff 大佬贡献。可以在原理图编辑器及封装编辑器中展开或收起所有内容。

2 j# X; V; `0 Q& N4 }1 K+ {0 j9 E/ |+ w0 f0 }

隐藏“不显示字段”

5 ~! `" F3 c5 |; S: F, M由JP Charras贡献。增加了从符号编辑器中隐藏 “不显示字段(hidden field)”的功能("视图">"显示隐藏字段"。

8 ^3 E/ _8 m. r5 F/ K" t/ [1 l4 Q, |, |" E9 E: D

e00j2maank464013502835.png

& L& G& o2 r6 S8 @' P之前在符号编辑器中无法隐藏,显得比较乱:

2 G$ Z% f$ R+ M

uwqdxithm5l64013502935.png

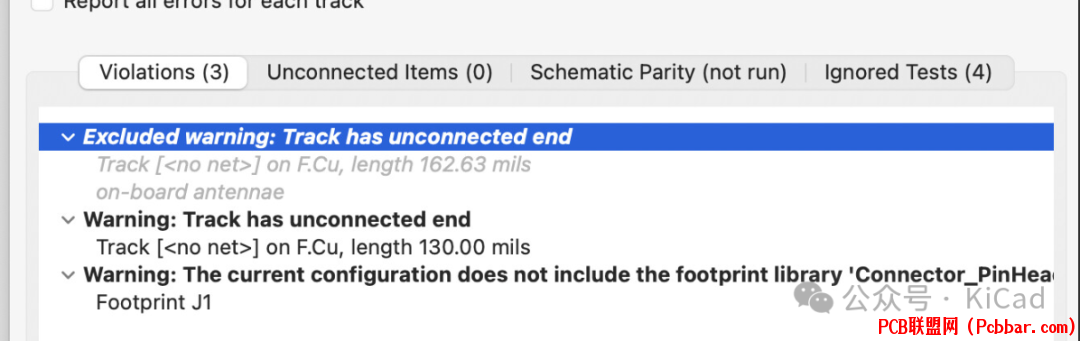

7 S* ^$ E1 f: ?- wDRC 排除项添加注释

7 G" D; f/ a% R+ C: O/ g& y由 Jeff 大佬贡献。能够为 ERC 和 DRC 排除项添加注释。7 y1 |3 c4 k! ^4 c

wi1m3ssdfjg64013503036.png

1 H" f1 o* `" H B; S( v

1 H" f1 o* `" H B; S( v

3 U R H# d5 k1 ^8 \

y2z21ocbwtz64013503136.png

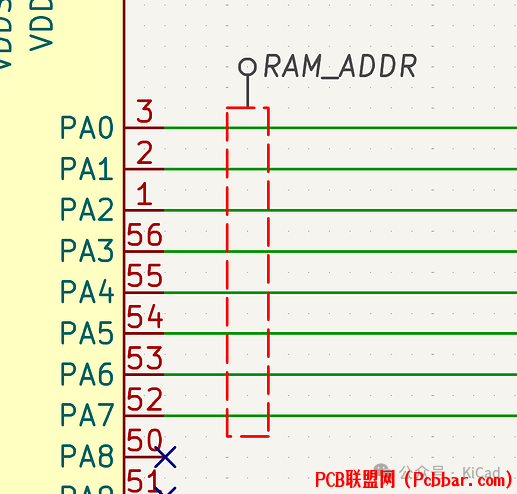

" [" G3 v3 i0 S6 _& ^1 M为原理图添加选择过滤器

4 F/ ?& ^( l. G4 Q9 |由 Jon Evans 大佬贡献。为原理图及符号编辑器添加选择过滤器,便于快速选中引脚、文本、图形等对象。# J, x; _/ e: ?+ e, l9 `! t

kmacjpyofta64013503236.png

" j$ E* k& d7 X) l# Q; S$ V V7 X层次原理图引脚与子图端口的同步3 Z: e3 T" J' u* U1 N/ y: z+ N% I

由华秋电子 Ethan Chien 贡献。可以为层次原理图引脚与子图的端口进行双向同步而无需来回切换。支持在层次原理图符号中直接摆放层次引脚(之前版本不支持),并将引脚自动生成子图的端口;也支持从子图的端口自动生成层次原理图符号中的引脚。- A; g1 _: i3 C4 m% t" j+ m

Altium ASCII 格式文件的导入3 |. o% c2 i! f9 Y9 P+ e

由 dsa-t 大佬贡献。已反向移植至 8.0.2。1 h% t1 t7 N( ^ ~# V2 d0 v

CLI 导出 3D 图片+ ~7 o$ F9 y4 x& ]+ y. n4 A

由dsa-t大佬贡献。添加了从 CLI 进行 PCB 3D 图像光线追踪渲染的功能,支持透明背景。% K4 \2 h4 Q& T, K) X, Y# E' j7 G# x

kicad-cli pcb render --floor --zoom 1.4 --rotate '-45,0,45' -o render.png video.kicad_pcb) D6 w1 @# z) p4 @1 J5 n

02qw4wpl1af64013503336.png

v2 O" u% u9 m& k1 d4 P, E8 F

v2 O" u% u9 m& k1 d4 P, E8 F

网络查看器升级为可停靠面板由 JamesJ贡献。网络查看器(Net Inspector)升级为可停靠的面板(docked panel)。该功能包括改进的过滤和分组、显示/隐藏和重新排序列的功能,以及保存/恢复所有设置的功能。新的面板支持网络类分组或自定义分组。# |8 d' c, R0 }6 x V, \9 _

njrxvlru40d64013503437.png

* c: {- s( _5 k/ T" u' o$ _& yRegulator 由 Jan Wichmann 贡献。在Regulator计算器面板中添加了公差计算。

+ E* M$ d; x; c* X" k9 A$ }

oxhtwu0dfpe64013503537.png

) S0 G, [3 s8 ~在层次浏览器中修改图纸名称Miklós Márton 在原理图层次结构导航器中添加了更改图纸名称的选项。3D 模型导出的更新/ k+ N) Z6 z% G! s! f9 z

实体 3D 模型导出改进:可选择将铜几何形状融合在一起可选择将内层铜导出可选择排除PCB本体或元件网络过滤器(可用于导出单个网络)使用圆弧进行区域几何近似,以便更快地处理并减小文件大小以 BREP 或 XAO 格式导出XAO 将焊盘表面定义为平面组,可导入 SALOME 或较新版本的 Gmsh 进行 FEM 仿真: ?, _8 i8 m/ X, F$ Y

hmmwfqa2gwl64013503637.png

. @5 w$ `& C3 O: G; l增加敷铜与封装Courtyard间隙规则

, e; n. y* ^% c7 r n6 P* |2 T扩展了 physical_clearance 规则,以检查敷铜和封装Courtyard之间的间隙。(rule "No copper pours under Capacitors" (constraint physical_clearance (min 0.1mm)) (condition "A.Type == 'Zone' && B.Reference == 'C*'"))以上规则 Query 语句表示所有敷铜与“C”开头封装的 Courtyard之间的最小物理间隙为 0.1mm。

4 _! S5 Z: V4 o; q- Q1 M8 A% W支持原理图规则区域

, b; ^0 B9 Q( y/ e! \" }3 {4 lJamesJ 增加了对原理图规则区域的支持,允许用户绘制一个区域,该区域可以附加网络类指示符。

8 T6 P, L% \8 Z/ d& z$ J' a4 r9 q

4hjbh5lbouq64013503737.png

( t1 O8 X4 Q6 i+ I* C简化敷铜形状

3 l* ]. Q( R- Z上下文菜单中添加了小工具(由 S.Hillbrand 提供):形状修改 –> 简化多边形。3 M* J9 X' Z5 A6 p8 P7 A' }$ ]6 ~

jx4mvblfge364013503837.png

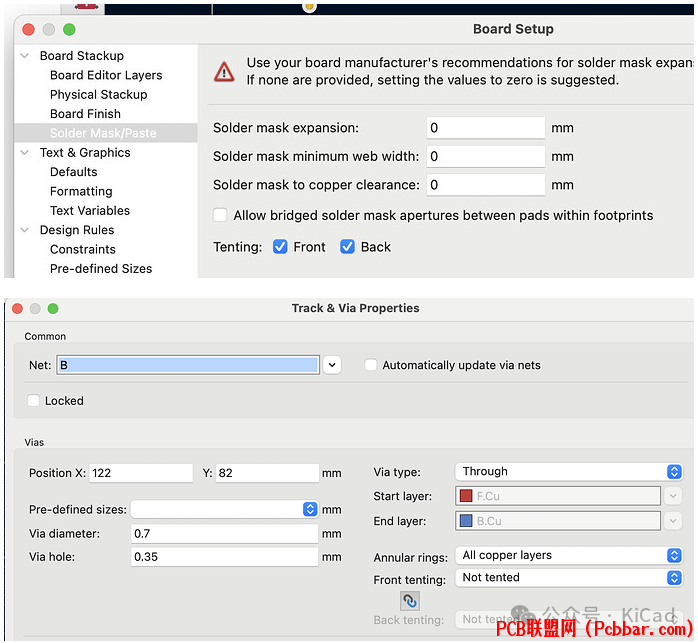

* M7 k; D3 d" _5 J: p, g" `3 Q控制过孔盖油的层: v6 }5 R4 a; w" M7 B

在整个电路板上控制顶层和底层的过孔盖油。也可以对每个过孔的设置进行覆盖。: ?( W y- u. O( W& ?3 O, u! G

snckc0bxpdh64013503937.png

5 b$ X) m9 T( b; L# F+ f: g

5 b$ X) m9 T( b; L# F+ f: g

注意:这将取代“绘图”对话框中的 “tent vias” 复选框,该复选框已被移除。

3 m, M" n1 l) f# ^, d' \ B% y增加“表格”对象

# n5 C T4 P2 E- l, y7 i在原理图编辑器、封装编辑器、PCB编辑器中支持摆放表格" ]% v) v0 K3 [% F+ j6 P/ F8 Z

rwhku0rvvbb64013504038.png

' |9 {: J/ R7 h: L# F- u8 z

' |9 {: J/ R7 h: L# F- u8 z

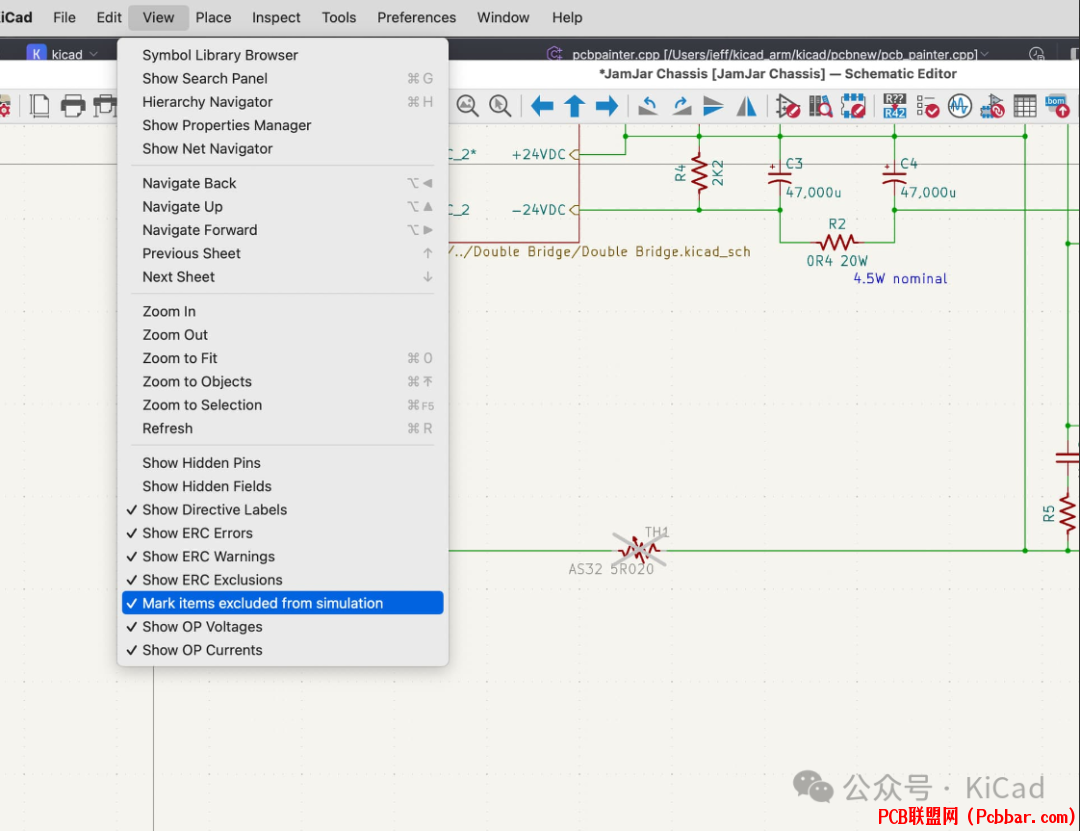

将对象排除在仿真外1 F7 w7 R( ^. O- {( y4 X

仿真时排除选定对象:

/ A0 X4 i$ b% }, }3 W

ezcj2xjb5pu64013504138.png

" Q; r4 f9 t& _将子图设为DNP

7 d. n5 q6 j' v4 f/ ~将这个图纸(Sheet)设为不安装(Do Not Populate)" j- T z9 | k

zfkcib2onr064013504238.png

3 ^9 J8 W3 W5 Q7 J+ u) I+ [' C

3 ^9 J8 W3 W5 Q7 J+ u) I+ [' C

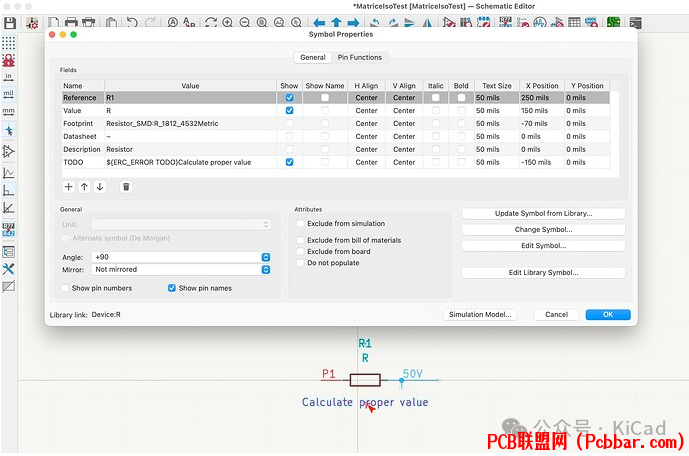

从文本变量创建 ERC/DRC 8 `8 i1 t' c" z8 e7 `' H# J+ y

@JeffYoung 添加了一项功能,可让您从文本框和字段创建 ERC/DRC 错误和警告:新文本变量:

' d( W4 r4 a6 l9 h${ERC_WARNING }${ERC_ERROR }${DRC_WARNING }${DRC_ERROR }变量必须位于字段、文本对象或文本框的开头,才能被 ERC/DRC 识别。

, }5 e0 ~/ b5 C它们被解析为画布上的空字符串。' z9 }6 C& G3 _' i

xzzvd5gpcyt64013504338.png

9 q! Y* |! B: c- }

9 q! Y* |! B: c- }

; E+ [" x7 n! e3 l4 m $ B3 n# H; d* h2 ^% q( y $ B3 n# H; d* h2 ^% q( y

允许在位号编辑窗口编辑 Unit! Z( p, U/ t& y" k+ n% o

$ P+ j1 g1 i; j; p3 B" H7 L $ P+ j1 g1 i; j; p3 B" H7 L

在制造层绘制焊盘轮廓及编号

+ r+ h/ f; ~5 l! Z

$ x- B) B( H, I% i从 ERC/DRC 中移除忽略的测试

2 s9 I7 r- V" G. `- p右键单击操作可从 ERC/DRC 对话框中删除忽略的测试:

/ r- W. m: \5 ? C$ i9 K' d 9 G# a4 r3 b9 Y- D* Q" _& P 9 G# a4 r3 b9 Y- D* Q" _& P

支持内嵌多种对象

+ a' {! H D' E l6 Y9 }您现在可以在原理图、PCB 、封装和符号中嵌入多种对象:1. 图框

8 X* C! E2 h7 U: w; ] . O6 E+ v0 H; u' y . O6 E+ v0 H; u' y

2. 数据手册

( s1 b. U( W+ H6 O. j( x $ n* |9 d4 v& ^ $ n* |9 d4 v& ^

3. 3D 模型8 f( t) e) e |0 O, B. L

w' y% C! g/ f: W t' ]$ h w' y% C! g/ f: W t' ]$ h

4. 字体3 {: V( H- k/ ^

4 U8 w& |8 P. w3 S- o' {9 J$ L/ m 4 U8 w& |8 P. w3 S- o' {9 J$ L/ m

STEP 支持导出丝印及阻焊平面

8 v$ K/ [% V1 O) R将丝印和阻焊层作为平面导出至 STEP / GLB (二进制 glTF) / BREP / XAO。# A: F. C6 e0 C% F' Q1 E

" a* h1 }4 b; K# t7 c " a* h1 }4 b; K# t7 c

4 k" T! X+ J# ~' p

; b: J+ x5 m( a( L2 n8 m ; b: J+ x5 m( a( L2 n8 m

ERC 检查本体和全局同名的标签

, \- o) Z \) g4 H" b' T8 g对具有相同名称的本地和全局标签进行 ERC 检查(来自 Wishlist: ERC local/global net name collisions (#9461) · Issues · KiCad / KiCad Source Code / kicad · GitLab)1 m$ U9 \" K) Z( E5 U/ C

, J- \- h, h7 F& T , J- \- h, h7 F& T

ERC 检查未连接的端点

9 o- ^& l% e9 U) B& m9 j $ [2 `. J% i- k7 y2 ` $ [2 `. J% i- k7 y2 `

同一网络分配给不同网络类

& C6 i/ g% F1 i/ Y% `/ R; B现在可以给网络分配多个网络类。这可用于调线长、模块化、自定义 DRC 规则。新功能包括:引入网络类排序允许网络类具有空属性(默认网络类除外)有效网络类由非空网络类字段按网络类优先级顺序构建(始终使用默认网络类参数作为后备)DRC 检查网络类等效性,要求两个项目具有相同的组成网络类集修改设计规则检查(DRC),以测试网络类别名称(A.netclass == 'my_netclass')是否与按优先顺序排列的构成网络类别列表相匹配。添加 DRC 函数 A.hasNetclass(‘my_netclass’) 以测试给定网络类是否已分配给对象从网络的有效聚合网络类中获取的原理图和 PCB 网络类颜色请注意,我们还整理了以前默认网络类可以分配原理图颜色但不能分配 PCB 颜色的情况。现在,默认网络类不能分配任何颜色。如果需要定制,则应在全局颜色设置中进行设置。4 ]: c7 J O5 C; A( m! x

; f3 x3 p( s4 _0 V7 u ; f3 x3 p( s4 _0 V7 u

' @/ U! I/ [) L0 f9 W

) N$ s6 z+ t" ?: a( ~& v8 O5 A6 G" e- a9 U/ W

6 B& z0 F$ ^: v$ I+ N0 jSTEP 支持仅导出指定的器件, ?2 q& N! E: t

STEP 导出现在支持根据 PCB 编辑器中选择的内容或位号列表(支持通配符)导出组件子集:2 A' V. ^1 N( Q

|9 ~' v( j$ @6 A) D6 p$ H( D9 N后者现在在 kicad-cli 中通过 --component-filter 选项支持。DRC 对 Skew 检查的增强% L. c; a- ~; }) W/ `, L- @* P

DRC(设计规则检查)中的skew规则现在有一个可选的标志(within_diff_pairs)。当设置此标志时,DRC规则将独立地应用于所有符合规则条件的差分对中的走线。当省略此标志时,当前的DRC行为保持不变,即skew是跨所有匹配的网络运行的(例如,用于检查总线的skew)。例如,对于以下原理图:, L7 o# q6 b- K6 t" ?

" j. t6 l2 J7 Y2 Y1 a9 y/ r1 U " j. t6 l2 J7 Y2 Y1 a9 y/ r1 U

对于以下的 PCB layout:

' }. C$ V0 u! _/ j* u & l6 _0 ?% p8 U) o% `! ^3 f! i & l6 _0 ?% p8 U) o% `! ^3 f! i

使用以下的 DRC 规则:! [( S" i+ C+ A6 |2 K) p- I/ I3 d

(rule diff_skew (constraint skew (max 3mil) (within_diff_pairs)) (condition "A.hasNetclass('DIFF_PAIR')"))产生的结果为: @0 D `8 q4 S- ` [( E

+ W" U1 M" t8 }( c + W" U1 M" t8 }( c

此外,布线器和 DRC 对 skew 的定义已统一为始终相对于 skew 集中最长的z走线进行测量(是每个 diff 对中最长的走线,还是所有走线中最长的走线,具体取决于是否设置了 (within_diff_pairs)。布线器还将选择正确的 skew tuning 约束,其中skew是使用 (within_diff_pairs) 规则定义的。3 U+ _% s P- T: t* W0 S

层对添加到预设列表

$ N" g+ Y: y+ t+ R/ o* R层对可以被添加到预设列表中。“启用”的层对以及当前设置的层对(如果它本身不是预设的),可以通过 “Shift+V” 快捷键进行循环切换。

$ P6 a) @! w' i$ g9 |0 y5 N / h# H8 w! Q$ M4 K / h# H8 w! Q$ M4 K

# j0 a3 I, Q G7 v& D9 u% }

9 W2 L' v' ~: |2 N! c% ]) K新的形状修改工具

P. z" G- r: |. ^8 {; P5 H& }在圆角和倒角工具旁边,有一个新的形状修改工具:“狗骨”(Dogbone)角部缓解,用于那些必须适配具有直角(特别是:比边缘路由铣刀更锐利的角落,通常是1或2毫米)的切口。, Z' e( e0 [" A" p8 Q2 I4 u$ \

& ^# u3 l: ?5 [1 @ x相对位置工具的优化8 z+ r: }0 J! @: F

位置相对工具现在可以使用任意点作为参考(可以捕捉到对象)3 @2 M+ o; t1 h; b) {4 q" ]( [

; @9 f' T! m) O高亮显示网络颜色1 S# M% G: B# _0 e+ I

在 eeschema 中,现在可以以高亮显示的方式显示由网络类定义的网络颜色,方法是选择网络类设置面板中的“高亮显示网络颜色”

1 A T; [. m v6 { . w! G' H/ B& L5 X+ d, A+ X4 L . w! G' H/ B& L5 X+ d, A+ X4 L

“高亮显示网络类颜色”选项移动到“显示设置”页面中:

7 ^: H3 W" x- }. w) H1 K2 E " r/ L# G3 s9 s " r/ L# G3 s9 s

结束语期待更多的中国小伙伴为 KiCad 的进步添砖加瓦!

6 f4 l$ |# x( y+ ]& i1 ^& A4 I/ H, X

注意:如果想第一时间收到 KiCad 内容推送,请点击下方的名片,按关注,再设为星标。% r& t) N! M6 j) {

常用合集汇总:

; i0 c) N& C9 k! ?# }. b# s1 J/ S和 Dr Peter 一起学 KiCad8 ?7 K% [: c9 T# M9 t2 v/ r

KiCad 8 探秘合集

8 b' X3 |6 ?) v+ @5 @KiCad 使用经验分享KiCad 设计项目(Made with KiCad)常见问题与解决方法KiCad 开发笔记插件应用

: m7 b6 P! N0 Z% n发布记录 |