|

c0emyanxtoy64029381833.png

1 {# L! x8 c/ ], Z

1 {# L! x8 c/ ], Z

一、DMA简介1、DMA简介DMA(Direct Memory Access:直接内存存取)是一种可以大大减轻CPU工作量的数据转移方式。CPU有转移数据、计算、控制程序转移等很多功能,但其实转移数据是可以不需要CPU参与。比如希望外设A的数据拷贝到外设B,只要给两种外设提供一条数据通路,再加上一些控制转移的部件就可以完成数据的拷贝。DMA就是基于以上设想设计的,它的作用就是解决大量数据转移过度消耗CPU资源的问题。有了DMA使CPU更专注于更加实用的操作--计算、控制等。

7 n, z) r: U* M* e+ L! I2、DMA的工作原理 DMA的作用就是实现数据的直接传输,而去掉了传统数据传输需要CPU寄存器参与的环节,主要涉及四种情况的数据传输,但本质上是一样的,都是从内存的某一区域传输到内存的另一区域(外设的数据寄存器本质上就是内存的一个存储单元)。四种情况的数据传输如下:外设到内存内存到外设内存到内存外设到外设当用户将参数设置好,主要涉及源地址、目标地址、传输数据量这三个,DMA控制器就会启动数据传输,传输的终点就是剩余传输数据量为0。换句话说只要剩余传输数据量不是0,而且DMA是启动状态,那么就会发生数据传输。

1 x% D# ^ F/ v1 T3、DMA是否影响CPU的运行在X86架构系统中,当DMA运作时,DMA实际上会占用系统总线周期中的一部分时间。也就是说,在DMA未开启前,系统总线可能完全被CPU使用;当DMA开启后,系统总线要为DMA分配一定的时间,以保证DMA和CPU同时运作。那么显然,DMA会降低CPU的运行速度。. |; n7 x# O( Y; N3 ^2 s

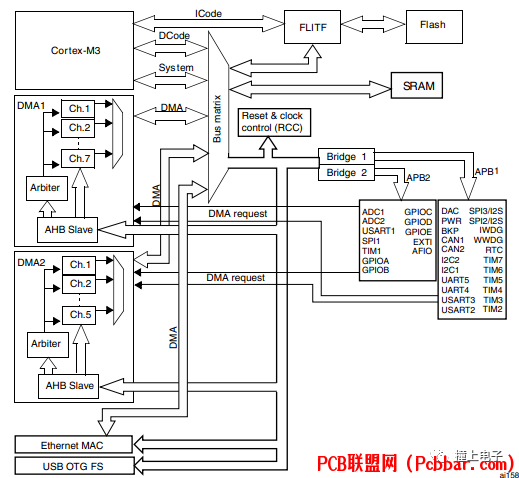

在STM32控制器中,芯片采用Cortex-M3架构,总线结构有了很大的优化,DMA占用另外的总线,并不会与CPU的系统总线发生冲突。也就是说,DMA的使用不会影响CPU的运行速度。2 F* y) P! s/ m- a Z. E( S2 F

4 r* }0 S- ?9 S# K. t! N& |

二、STM32的DMA结构1、DMA的主要特性● 12个 独立的可配置的通道DMA1有7个通道,DMA2 有5个通道 6 c5 e8 |; w/ m, x) ^

● 每个通道都直接连接专用的硬件DMA请求,每个通道都同样支持软件发。这些功能通过软件来配置。 9 K0 |$ Z) F" h7 r& e$ v

● 在七个请求间的优先权可以通过软件编程设置(共有四级:很高、高、中等和低),假如在相等优先权时由硬件决定(请求0优先于请求1,依此类推) 。 ( j9 b( p: ^5 H9 {

● 独立的源和目标数据区的传输宽度(字节、半字、全字),模拟打包和拆包的过程。源和目标地址必须按数据传输宽度对齐。

1 K$ A& z5 F1 D, z( G& w* X● 支持循环的缓冲器管理

- P! w% N0 h- w! \( N● 每个通道都有3个事件标志(DMA 半传输,DMA传输完成和DMA传输出错),这3个事件标志逻辑或成为一个单独的中断请求。 4 B/ A* N! p, w+ w* G7 |

● 存储器和存储器间的传输 & v' d4 \( X0 Y. B- q1 u; |. c

● 外设和存储器,存储器和外设的传输 1 c* ]6 U3 i1 ]6 E9 q: u, Y

● 闪存、SRAM 、外设的SRAM 、APB1 APB2和AHB外设均可作为访问的源和目标。

* E L! v5 Z, {7 p# I$ l# L● 可编程的数据传输数目:最大为65536

$ o# h) G* c% P" X( K1 C1 g2 @; x下面为功能框图:9 m- w8 v4 M$ L/ z5 B$ {

h34tsoyqefv64029381933.png

/ p- \# E3 W7 a0 I# {

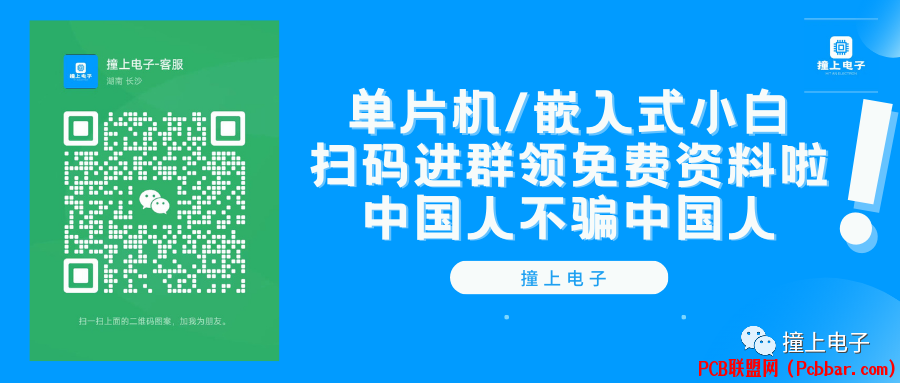

5 z5 ?- u. r4 k1 E" |: w& O2、两个DMA控制器结构① DMA1 controller d2 Z/ c0 o- u

beostn2jr4l64029382033.png

& f1 O) @' t* L- d② DMA2 controller

' y5 |1 B1 H, _3 O4 l! M

m3qtcpt5ady64029382133.png

( g" v: f. G. w2 y

( g" v: f. G. w2 y

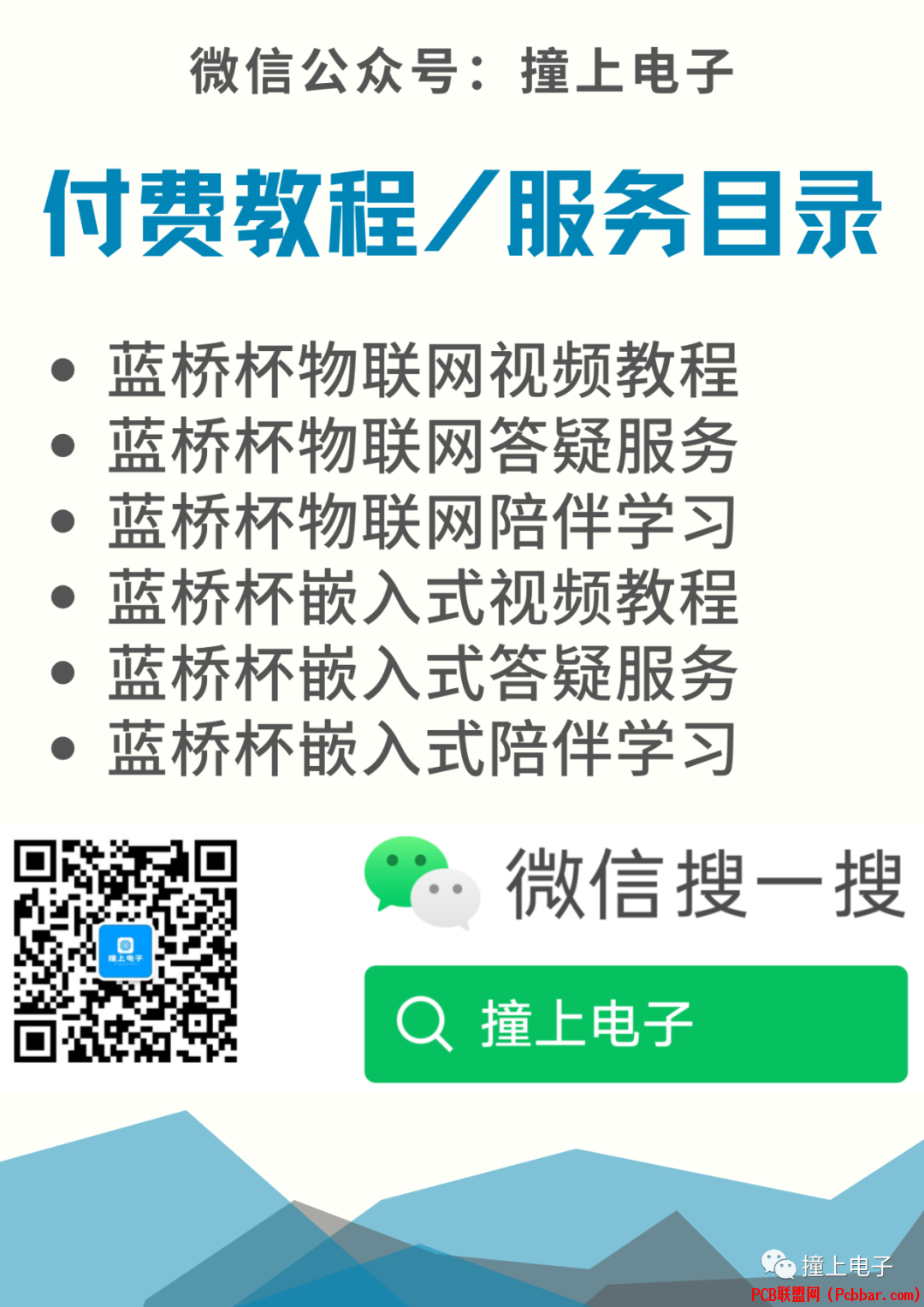

3、DMA寄存器列表; U6 F4 a* ]" ^

z132ed2owkd64029382233.png

/ r& W* `/ q) w( ` t① 中断类DMA_ISR:DMA中断状态寄存器DMA_IFCR:DMA中断标志位清除寄存器说明:DMA1、DMA2分别有一组寄存器。② 控制传输类DMA_CCRx:DMA通道x配置寄存器 DMA_CNDTRx:DMA通道x数据数量寄存器DMA_CPARx:DMA通道x外设地址寄存器DMA_CMARx:DMA通道x内存地址寄存器

' N1 i. }( x# A- [7 w* I* [. K/ X说明: 1> 每一个通道都有一组寄存器。2> DMA_CPARx、DMA_CMARx是没有差别的,它们都可以存放外设的地址、内存的地址。DMA_CPARx、DMA_CMARx只不过起得名字有差别而已。; y/ ]' j& B- W$ x. [6 s# y

4、STM32的DMA工作特点① DMA进行数据传输的必要条件剩余传输数据量大于0DMA通道传输使能通道上DMA数据传输有事件请求前两者都好理解,对于第三点确实需要详细的解释,请看下边的三条。( _4 S" o `4 j) g) T! r

② 外设到XX方向的传输假设是ADC到存储器的数据传输,显然ADC的DMA传输的源地址是ADC的数据寄存器。并不是说只要DMA通道传输使能后,就立即进行数据传输。只有当一次ADC转化完成,ADC的DMA通道的传输事件有效,DMA才会从ADC的数据寄存器读出数据,写入目的地址。当DMA在读取ADC的数据寄存器时,同时使ADC的DMA通道传输事件无效。显然,要等到下一次ADC转换完成后,才能启动再一次的数据传输。

5 k% a* [0 E8 U7 P. Q: m③存储器对XX的DMA传输因为数据是准备好的,不像ADC还需要等待数据到位。所以,不需要对应通道的事件。只要使能DMA数据传输就一直传输,直到达到设定的传输量。7 ]# g! i, p& K# r! q2 `

举个例子:1.内存到内存 DMA传输请求一直有效2.内存到串口 DMA传输请求一直有效一种解释: 存储器对存储器的置位,就相当于相应通道的事件有效。 对应通道的事件有效和存储器对存储器的置位,就是传输的触发位。每次传输的事件置位一次,完成一次传输。如果是由外设引发的DMA传输,则传输完成后,相应传输事件会置为无效,而存储器对存储器的传输,则一次传输完成后,相应事件一直有效,直至完成设定的传输量。④外设以DMA方式工作时,能否再以软件方式进行操作?有一点是肯定的,当外设以DMA方式正在数据传输时,不可能再相应CPU的软件控制命令,否则这不符合逻辑。

2 b+ p; ^$ V1 Q" g+ i但是,倘若外设仅仅配置成DMA工作方式,但是DMA请求并未产生,数据传输并没有进行。此时,软件控制命令仍然能够对外设进行控制。这是笔者在串口以DMA方式发送数据情形下,所得到的测试结论。

# G2 t+ _" _& ~: F% R1 n三、STM32的DMA软件编程1、“内存到内存”模式传输① 初始化配置/** * @brief USART1 TX DMA 配置,内存到内存 * @param 无 * @retval 无 */void DMA_Mem2Mem_Config(void){ DMA_InitTypeDef DMA_InitStructure; /*开启DMA时钟*/ RCC_AHBPeriphClockCmd(RCC_AHBPeriph_DMA1, ENABLE); /*设置DMA源地址*/ DMA_InitStructure.DMA_MemoryBaseAddr = (uint32_t)SendBuff;8 r& p% U8 b: `+ V" W& W0 r) M

/*设置DMA目的地址*/ DMA_InitStructure.DMA_PeripheralBaseAddr = (uint32_t)ReceiveBuff; 9 v' c3 t9 ^" p& u2 E8 j/ f! m

/*方向:从内存SendBuff到内存ReceiveBuff*/ DMA_InitStructure.DMA_DIR = DMA_DIR_PeripheralDST; /*传输大小DMA_BufferSize=SENDBUFF_SIZE*/ DMA_InitStructure.DMA_BufferSize = SENDBUFF_SIZE;) F9 {5 R! X1 H1 K7 U; X

/*ReceiveBuff地址自增*/ DMA_InitStructure.DMA_PeripheralInc = DMA_PeripheralInc_Enable;

5 ~: T8 s: t, i X+ U3 r /*SENDBUFF_SIZE地址自增*/ DMA_InitStructure.DMA_MemoryInc = DMA_MemoryInc_Enable; 5 Y7 ]( F W7 |- c

/*ReceiveBuff数据单位*/ DMA_InitStructure.DMA_PeripheralDataSize = DMA_PeripheralDataSize_Byte;

5 D, S# ?8 z8 l4 C /*SENDBUFF_SIZE数据单位*/ DMA_InitStructure.DMA_MemoryDataSize = DMA_MemoryDataSize_Byte; ; ~! f+ Q! Y4 z( s# m- n# q

/*DMA模式:正常模式*/ DMA_InitStructure.DMA_Mode = DMA_Mode_Normal ;( {7 C+ w& x s# F2 `. t0 V

/*优先级:中*/ DMA_InitStructure.DMA_Priority = DMA_Priority_Medium; ! |9 |+ G: L/ c0 ~

/*使能内存到内存的传输 */ DMA_InitStructure.DMA_M2M = DMA_M2M_Enable; /*配置DMA1的4通道*/ DMA_Init(DMA1_Channel4, &DMA_InitStructure); /*失能DMA1的4通道,一旦使能就开始传输*/ DMA_Cmd (DMA1_Channel4,DISABLE); }' r5 ?+ C# N) x; \9 r9 w3 ~# ?

② DMA中断配置/* * @brief DMA 中断配置 * @param 无 * @retval 无 */void DMA_NVIC_Configuration(void){ NVIC_InitTypeDef NVIC_InitStructure; /* 配置中断源 */ NVIC_InitStructure.NVIC_IRQChannel = DMA1_Channel4_IRQn; NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 1; NVIC_InitStructure.NVIC_IRQChannelSubPriority = 1; NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE; NVIC_Init(&NVIC_InitStructure); 4 I6 L ^6 A' m# J

/* 配置DMA发送完成后产生中断 */ DMA_ITConfig(DMA1_Channel4,DMA_IT_TC,ENABLE);}6 j( U& {. `' {9 s, }: E( A

③启动传输DMA_Cmd (DMA1_Channel4,ENABLE);

2 i% t2 \0 ] n2、利用DMA实现循环传输方法1:单次传输模式当传输结束时,触发DMA中断,在中断程序中首先失能DMA通道,然后修改该通道的传输数据量。最后重新使能DMA通道,注意只有失能的DMA通道才能成功修改传输数据量。

1 t" W& f b) c+ b, l& X方法2:循环传输模式当传输结束时,硬件自动会将传输数据量寄存器进行重装,进行下一轮的数据传输。7 D2 P! n: [: v E- D8 q

L& S& l9 t& X- y

四、再谈STM32的DMA传输是否影响CPU的运行速度声明:经过笔者测试,当DMA工作在内存到外设的传输和内存到内存的传输时,都不会影响CPU的运行速度。为了给这种现象一个合理的解释,笔者做以下猜测:

. c/ l; o; R0 S1 q, b6 ^3 S1、S3C2440的DMA传输S3C2440的SDRAM是外置的,并且SDRAM的数据线、地址线、控制线总共只有一组。假设DMA传输的方向是内存到外设,当DMA运作时,需要占用SDRAM的三类线才才能实现传输;而与此同时CPU也需要通过这三类线来访问SDRAM来读取程序、读写数据。/ o1 V; B/ |" ^8 Y# X I# R

显然,DMA的运行与CPU的运行有交叉点,DMA就会影响到CPU的运行。3 n( K N$ A$ [: i+ z

2、STM32的DMA传输 STM32与S3C2440的区别是很大的,S3C2440是微处理器,RAM外置且空间很大;STM32是微控制器,RAM片内集成且空间较小。此时,ST公司就有可能提升DMA的运作效率,使DMA的工作不影响到CPU的运行。 外设与外设之间的DMA传输,因为与CPU的运行没有交叉点(CPU的数据流注意是在Flash、内存、寄存器中传输),所以不会影响CPU的运行速度。唯一有可能影响的是外设与内存或者内存与内存之间的DMA传输。 倘若ST公司的SRAM是一个双口RAM,也就是同时可以由两组接口对RAM进行访问,就可以很好的解决速度影响问题。倘若CPU恒定占有一组接口,而另一组接口留给DMA控制器。那么当外设与内存或者内存与内存之间的DMA传输时,由于不与CPU的访问SRAM接口冲突,所以可以解决速度影响问题。 但其实偶尔还是会影响的,当CPU访问SRAM的空间和DMA访问SRAM的空间相同时,SRAM势必会对这种情况进行仲裁,这可能会影响到CPU的访问SRAM的速度。其实,这种情况的概率也是很小的,所以即使影响CPU的运行速度,也不会很大。% j/ O, g0 Y' y0 x8 r3 ^- W- b0 k

==========1 [( ~# `3 @' F' H

往期回顾:ADC的低功耗和阻抗问题7 R% P2 X4 O( I

利用STM32CubeMX解读时钟树

k) e A- l" ?- E* p2 e* x& r外部中断为什么会误触发?

/ o! q3 S& F# y) G! O读取STM32芯片温度与当前供电电压

1 _0 X0 t9 Z; @0 L有源晶振和无源晶振的区别==========原文来源:请点击阅读原文作者:鲸小鱼-平台:博客园7 M- H7 v0 f% U' P( G, b* N, x6 D

7 X' o- M! _1 P$ Z1 Q

dsctyde4gju64029382334.png

- u$ o: R& g( w7 d! Q" |

- u$ o: R& g( w7 d! Q" |

! A4 G" O6 w5 F8 w3 a, U/ r

zyrzxpwwxqe64029382434.png

2 q" M6 ~) ?& W2 b: b" l# b- N

1 E4 w j1 ~8 t& E/ q& U; h$ X

f5poruf522p64029382534.png

|