|

cyw2fzrbykz64087486542.png

4 F8 p! s W& j- z# t, O

4 F8 p! s W& j- z# t, O

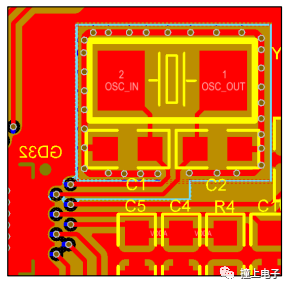

一,晶振. K# P# |: x; c; a

晶体要尽量靠近芯片Pin,远离诸如功率电感的磁感应器件与诸如天线的辐射器件,与同层其他信号走线利用GND铺铜及VIA隔离。晶体输入输出走线要尽可能短且少弯折,不可跨层或交叉走线。两边负载电容与晶体各自的GND和PAD可以相连,并摆放多个GND和VIA以提高散热保障。晶体下方尽量不走任何传输线,保留完整的GND铺铜。晶振电路走线以及匹配电容应该与晶振在同一侧,尽量不穿层。布局应该使晶振靠近MCU,晶振电路走线不能太长,不要超过12mm。在晶振同层以及下一层与其他电路间隔开,晶振电路周围也使用接地 VIA 形成保护环。

; H% J e/ i; A9 n. Q8 f& Z- k) i1 S$ u* U! A9 x3 T+ T

lqaoq03vzax64087486642.png

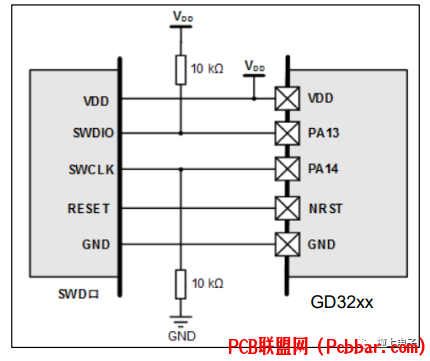

6 G: j* w9 C1 e二,下载口3 o( @. a" a4 |; M' x v- C) r: o

MCU的 SWD 烧录口走线应尽量短,远离板边 12mm。有以下几种方式可以提高SWD下载调试通信的可靠性,增强下载调试的抗干扰能力。缩 短SWD两个信号线长度,最好15cm以内;将SWD两根线和GND线编个麻花,缠在一 起;在SWD两根信号线对地各并几十pF小电容;SWD两根信号线任意IO串入100Ω~1KΩ 电阻。2 z+ x1 T* x' Y4 c, F+ g; ]

grk0fdtwtxr64087486742.png

( I: h2 `3 c. m4 I8 A

( I: h2 `3 c. m4 I8 A

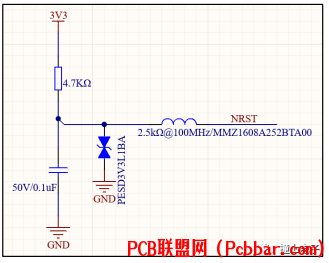

三,复位电路

P) V, F/ N1 l

cskfu0rvz1i64087486842.png

$ I+ {. C$ e- X& K: {! u1 x

$ I+ {. C$ e- X& K: {! u1 x

==========0 n" F8 Y, Y% u/ Z# {& U

往期回顾:单片机的RTC获取网络时间

9 }% d" c9 o, \- o ?. G& d. {我都不知道的PWM的很偏的问题

' K0 N1 y# N# x" Y8 \一个小细节,精度提供一大截

4 f4 w- j0 b; k* i嵌入式软件工程师常用的5 i3 {8 G9 \3 N$ l# \

==========

a' a, N0 N1 w6 _) O9 b! Y

xgduivugeld64087486942.png

0 M: ~: v2 j V9 h+ s. r/ ]

0 M: ~: v2 j V9 h+ s. r/ ]

vmdrv01h11r64087487042.png

; {2 B% b8 B2 d& G$ f) [2 I

; {2 B% b8 B2 d& G$ f) [2 I

ajlauv1pn5564087487143.png

|