|

pmm3l1y1xcw64028576422.gif

点击上方名片关注了解更多

什么是传输线阻抗

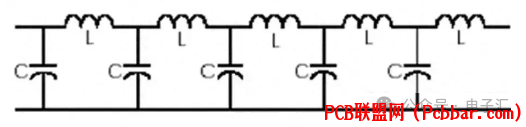

我们知道传输线理想简化模型如下图所示,这似乎跟导线电阻没半毛钱关系。从模型来看,的确跟导线电阻没有关系,但是该结构整体所体现出来对信号边沿的作用更像是一个电阻:呈现串联电阻(阻性)和延时的效果。

21nsisn3g2464028576522.png

传输线理想模型

如上图为无损传输线模型,以及在信号传输过程中的电流完整的流动过程,我们用L和C来描述传输线的回路电感和电容;

1. L指的是回路电感,这是一个等效电感:不是信号路径的局部电感,而是信号路径与回流路径构成的回路电感;所以该电感跟回流路径强相关。举个例子:当传输线信号路径不变,而回流路径不连续时(例如:信号线的参考GND层被分割,回流路径就要绕远路),传输线的电感就会增大;

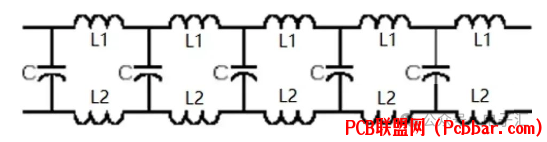

如之前所述传输线电感展开如下图:Lloop = L1+L2-2*L12;

djj4eg00zq464028576623.png

2. C在如上拓扑中,指的是信号路径相对于回流路径之间的电容。

举个例子:信号线与回流地之间的板间电容,其间距是PCB层间距,介电常数是FR-4材料的参数。

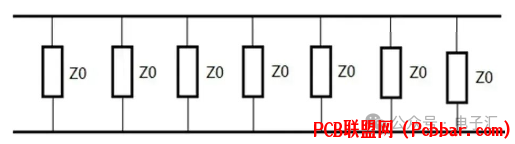

如此,我们知道无损传输线的阻抗模型等效为:很多组串联在信号路径上的L和并联在信号路径与回流路径之间的C组成;而且电流是从信号路径到回流路径的方向,由此得出:传输线的阻抗可以等效为搭接在信号路径与回流路径的一个电阻(并联电阻),如下图所示。搞错没得?这跟之前看到过的传输线等效模型完全不一样啊,明明记得之前看到的特征阻抗似乎是“串”在“导线”上的诶。

143koaist4364028576723.png

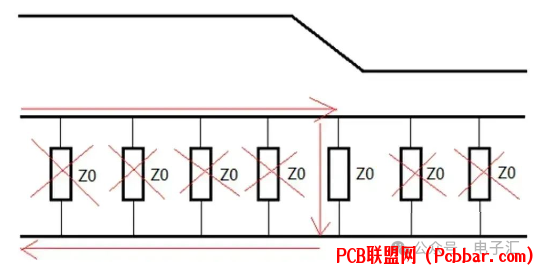

的确,这个并联的模型似乎有致命问题:如上图所示,如果传输线的阻抗是搭在信号路径与回流路径之间的电阻,那么这么多电阻并联后应该是Z0/n而不是Z0,假如有一根无线长的导线,那么特征阻抗就为0了么?这违反了常识和电路的基本原理啊。

挠了半天的头,还是先回到传输线的定义来看看:信号在传播过程中只有信号前沿的那部分导线才能看成是传输线。原来如此!如下图所示,在信号跳变的左侧是高电平(例如3.3V),右侧是低电平(0V),信号路径与回流路径上的电压差保持不变,没有发生充放电的动作,所以这些地方阻抗是无穷大(导线上的信号是固定电平,则信号路径和回流路径之间电压不会变化,此时电容不会进行充放电,所以电流I = 0;而Z =U/I = ∞,相当于断开);只有处于信号跳变处的信号路径与返回路径之间进行着充放电的动作,电容和电感才有了用武之地,成为传输线的“阻抗”:Z0。如下图所示。

isnymkeojws64028576823.png

那结论就出来了:传输线的阻抗是信号前沿(跳变)处所受到的阻抗,它是一个瞬时的阻抗。所以传输线阻抗也可以看成串接在信号路径上的一个电阻。

好,我们现在来总结传输线阻抗的描述:传输线阻抗是信号在传输过程中,信号前沿所受到的信号路径与回流路径之间瞬时阻抗。

如果传输线的瞬时阻抗在整条“导线”上都保持恒定(传输线瞬时阻抗保持一致),那么我们称之为:传输线的特征阻抗。传输线特征阻抗的特点是:它只与介质材料、传输线结构相关,与传输线长度无关。因为无论你在后面再加多长的50Ω阻抗的传输线,也只是向后再并联了50Ω阻抗,在跳变沿路过这段“导线”的瞬间才有用。所以阻抗是叠加不上去的。

硬件工程师及从业者都在关注我们

iqjjghjfnn164028576923.gif

iu020xtt5c564028577023.gif

wa4ohrnzkkl64028577123.gif

1yaiddmzf0564028577223.gif

wg45wmn21uq64028577323.gif

qeffcz34imv64028577423.gif

d01ynbxalqr64028577523.gif

w5xt1j4gutv64028577623.gif

fb5qajjtduh64028577723.gif

n1rl2orvhne64028577823.gif

jb5am14y0vg64028577923.gif

o4islveu1vb64028578023.gif

oac02glal3c64028578123.gif

1ouseesdeqv64028578223.gif

u2wh5xbefll64028578323.gif

声明:

声明:文章来源电子汇。本号对所有原创、转载文章的陈述与观点均保持中立,推送文章仅供读者学习和交流。文章、图片等版权归原作者享有,如有侵权,联系删除。投稿/招聘/推广/宣传 请加微信:woniu26a推荐阅读▼

电路设计-电路分析

emc相关文章

电子元器件

后台回复“加群”,管理员拉你加入同行技术交流群。 |  /1

/1