|

j0ffkrglt3j64011547321.gif

2 A+ ?* T$ `+ n* |* z3 A/ i% q% {9 V; o

2 A+ ?* T$ `+ n* |* z3 A/ i% q% {9 V; o

点击上方名片关注了解更多

+ {1 U9 c6 |( s8 w; c6 T" w. V4 c

1 D+ T( p7 w7 E5 |( v

; i! y( L g0 v' s7 o

大家好,我是王工。

* ^1 s& A L B0 x2 |

) I: n0 K# u7 w! P" G/ w7 u7 z" ~这是微信上一个兄弟找的我,说他电路调试时有问题,问我有没有可以解决的办法。下面是部分聊天截图。

, _2 r9 K5 R! @) v

lv14m4c2kg464011547421.jpg

# J$ ?$ i' [: ~+ Q+ O0 d, l! [% u( z0 W* f9 Q2 {2 m

通过交谈,我把他的需求梳理了一下:, U# [% H# j$ S" \

设备有两组供电电源,一组是主电源,另一组是辅助电源。

. Y# ?$ m: y2 [主电源和辅助电源同时供电,优先使用主电源,当主电源断电后,辅助电源无缝衔接给设备供电。' z" M3 x( P$ O

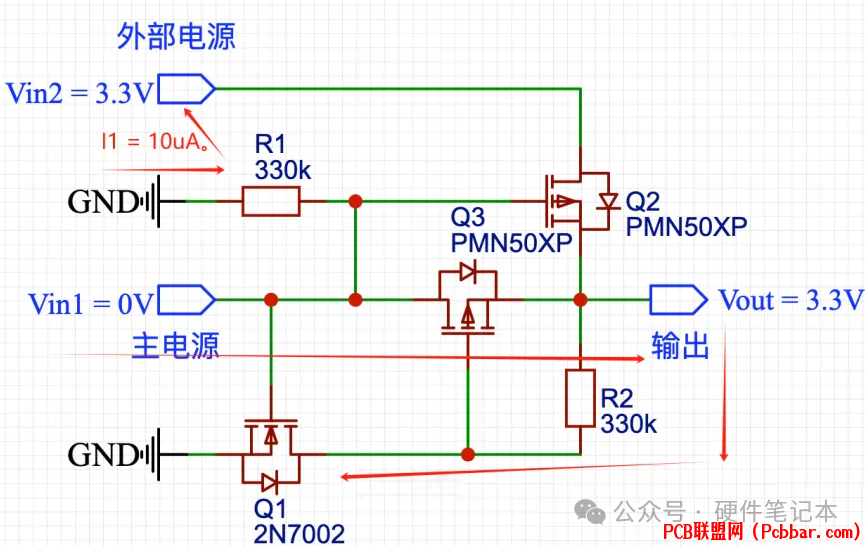

然后呢,网上有一个推荐电路如下图:这个电路是怎么工作的呢?

. U1 P8 y- Q+ n, J4 ~

mhawwc1z0rl64011547521.png

6 p- K$ l8 s8 E" _ j; D

6 p- K$ l8 s8 E" _ j; D

电路分析:

5 z& z4 w. |1 D' {1、当主电源Vin1为3.3V时,Q1的NMOS导通,然后Q3 PMOS的栅极被拉低, Q3 导通,Q2 MOS管关闭,外部电源Vin2断开,VOUT由Vin1进行供电。2、当主电源Vin1断开,Q1 NMOS截止,Q2 PMOS的栅极通过R1下拉,Q2导通,Q3 PMOS的栅极通过R2上拉,Q3截止。VOUT由外部电源Vin2供电。' H+ B9 Z1 Y, `; E, Z9 `5 b1 ]

通过分析看来,好像电路没什么问题,主备切换可行。但是在实际调试过程中发现主电源在下降的过程中,Q1和Q3不能及时断开,导致Q2只能通过体二极管导通,有0.5V的压降。Q3不能完全关断,而Q2就开始导通,外电源通过Q2、Q3形成通路,进一步阻止主电源的降低。相当于Q2永远不能导通,一直都是体二极管在导通。这就很严重了,相当于MOS管Q2一直没工作,整个电路就没啥用。- A6 k! y7 p [6 D

问题出来了,那是什么原因导致的呢?其实就是主电源在下降的过程中Q1,Q3没有及时关断导致出现一系列问题,那是什么原因导致这两个管子关闭这么慢呢?两种可能:

! ? k; o# S# N$ Y2 v7 {8 w) g1、主电源本身掉电比较慢,从而引起管子慢关断;% n0 N& W& O8 \/ Y/ F

2、MOS管选型不对,Ciss寄生电容太大(感觉又不大可能,现在管子寄生电容都做的很小,应该影响不大)。2 m" `8 v( b9 D! }+ ?

至于怎么优化电路,两种方法:

3 b" Y% ~$ O* }+ V4 {1、让主电源快速掉电;(怎么做到?)

& t+ H; u N$ Y, m. m3 l/ s$ ~2、让辅助电源慢速上电。(很难,而且不太好)

/ p6 M1 \) b! V" P) d& b1 m0 l% p0 }, N2 `6 q& g( h. Y8 S

这个例子也给大家提个醒:网上的电路不能随便拿来用,自己最好先验证一下再用。

) F7 c8 ^# Z R- i1 T& w5 f最后,这位兄弟板子已经打回来了,各位有比较好的优化建议,或者更好的电路分享,可以留言或加扫下方二维码,加微信告诉我,谢谢大家。

2 @: z+ N, A' e3 y$ x- d

dsqqx512gt364011547621.jpg

; Z$ p# `, `; b9 x ~- }: f

; Z$ p# `, `; b9 x ~- }: f

kn3tpfwkxjp64011547721.jpg

) u, [; T. O; X4 T6 l& @声明:

8 k3 Y6 G3 I* ?$ q6 }+ E$ L' n9 G, B声明:本号对所有原创、转载文章的陈述与观点均保持中立,推送文章仅供读者学习和交流。文章、图片等版权归原作者享有,如有侵权,联系删除。投稿/招聘/推广/宣传/技术咨询 请加微信:woniu26a推荐阅读▼

; @2 A8 i7 S& p. q9 m4 u电路设计-电路分析5 P7 A- @! ]% f

emc相关文章) `6 G$ N% u4 \) _$ P; Y& i7 {

电子元器件4 p' J5 E( e0 U. H

后台回复“加群”,管理员拉你加入同行技术交流群。 |