【摘要】! r: J( q3 N- w* x$ S

本文介绍了曾经趟过的那些坑之DCDC调试。在调试过程中,遇到的RT9018电源芯片的上电故障的分析、定位和解决方法,对产生的故障的原因和解决问题的思路做了简要介绍。

) f( s, \$ P/ K4 x- @7 l1、问题现象/ R e) e' |. A8 {+ Q) p# N5 U

oeqkuzeharx6403024306.png

8 ^( x" B( S; T5 ]5 E# s3 s

8 ^( x" B( S; T5 ]5 E# s3 s

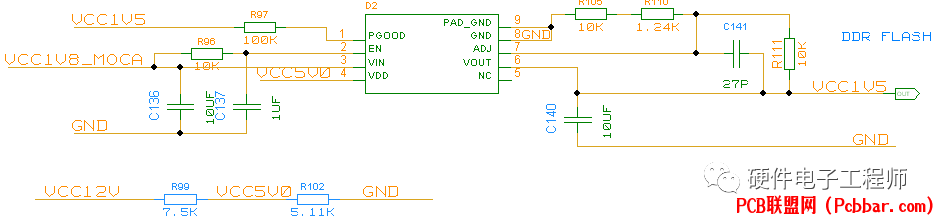

图1 RT9018及其外围电路

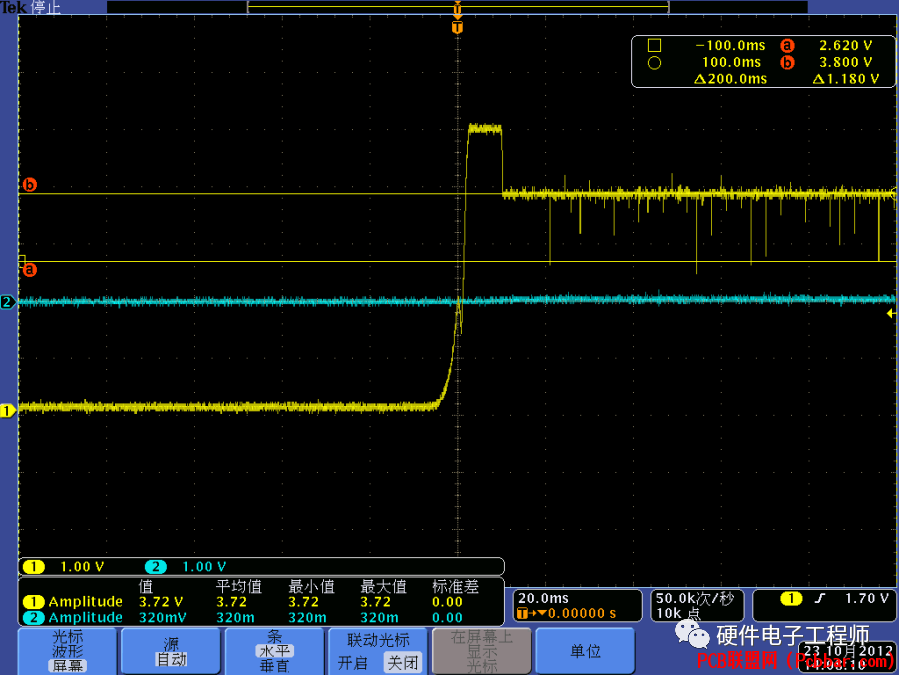

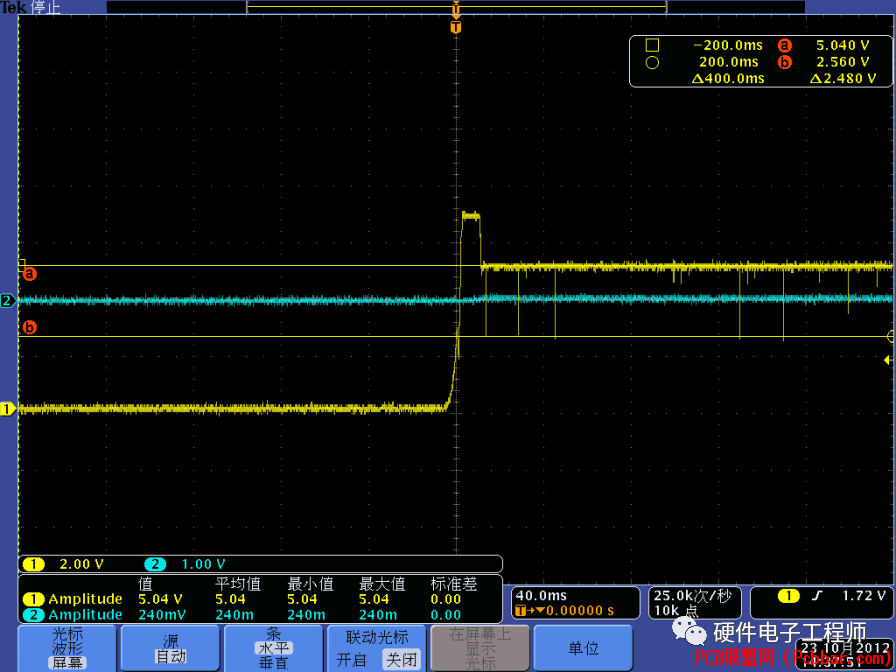

* Y+ t2 i. y1 k如图1所示为RT9018及其外围电路,在单板设计中,使用1.8V作为输入和使能信号,VDD是芯片内部控制电路的输入电压,采用两个分压电阻分压出5V输入到VDD。起初在设计时,没有考虑到RT9018芯片VDD引脚的对地阻抗,认为使用7.5K和5.11K电阻对12V分压即可产生5V电压。但是实际上RT9018启动之后,会在VDD拉取一定的电流,使得电位下降,如图2所示为VDD输入电压和输出电压的上电波形,可以看出,VDD上电过程中一个跌落,而且上电完成之后,分压只能达到3.72V,而且有明显的跌落,RT9018无输出。7 c) V& Y+ ~3 u" \

d23vprzzptj6403024406.png

5 d9 G2 l: [6 @% T0 |! |, O* l+ c% m0 \图2 RT9018上电波形(通道1-VDD,通道2VOUT)

: _8 S0 i: K7 ~% k/ f7 ]" Y2、问题分析

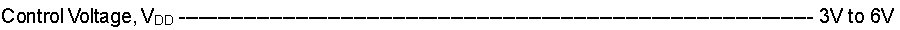

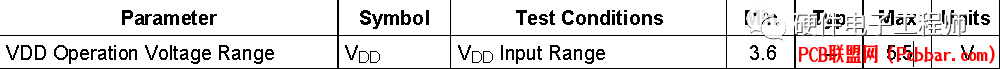

}. T* u- q- O1 m3 R# x查阅RT9018规格书,如图3所示为RT9018的内部逻辑框图,可以看出,VDD引脚的输入电压用于控制内部电路的POR,连接到内部的上电复位电路(Power On Reset),并为内部电路提供一定的电流。VDD引脚可以承受的电压范围在3~6V,正常条件下推荐的输入电压为3.6~5.5V。

( _1 I9 @7 W9 L9 u: B

ckcho4lh2lq6403024506.jpg

, R# c" k, s- H! z0 Z图3 RT9018的内部逻辑框图

( _5 B7 Q. D3 t4 X

xubriwzwdo36403024606.png

. U9 v5 ~6 r. Z2 k9 a* p1 [1 b. s) J, g/ c/ a. _8 X. b8 m

yzh4bnw42tr6403024706.png

2 e% Y% Q0 Z8 H; u/ G X图4 VDD输入电压要求4 B% V; O+ @. f* E

为了解决VDD分压输入不正确的问题,首先考虑调分压电阻,保持R99阻值7.5KΩ不变,将R102调整为9.5KΩ之后,如图5所示可以正常输出5V电压,但是有明显的跌落现象,从5V跌落到2.5V左右,而且RT9018仍然没有电压信号输出.: H+ F0 {; w5 d b( Y' X9 C1 p9 f/ f

30fi5mffymh6403024806.png

2 P: U" R, l! [6 s: j6 z

2 P: U" R, l! [6 s: j6 z

图5 RT9018上电波形(通道1-VDD,通道2VOUT)8 B/ E! S- T4 }" [1 k

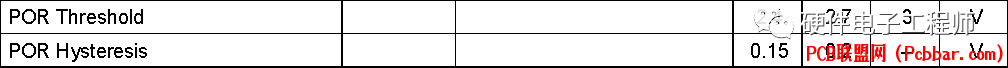

分析VDD跌落产生的原因:VDD输入电压为内部POR电路提供电流,根据分压电阻计算,VDD能提供的电流为12V/(7.5K+9.5K)=0.7mA,根据Richtek方面反馈,VDD正常工作需要的最大电流值为5mA,现在能提供的电流远小于正常工作需要的电流,当电流被内部电路抽走之后,在R102上的分压就会下跌,查阅规格书,如图6所示,POR开启电压的临界值为2.7V,迟滞电压为0.2V,也就是说VDD高于2.7V开始使能,但低于(2.7-0.2)=2.5V时,芯片开始关闭。所以在我们看到的波形里,当VDD因为POR电路抽走电流导致电压下跌,当下跌到2.5V时,POR开始关闭,然后VDD又回到预设的分压值5V,使POR电路重新打开,这种现象不断重复,具体表现就是如图2和图5中的情况。; W/ w7 H$ }& |: ~ r- o6 Z! z. [* T

c3m4qk4ilzz6403024906.png

# H, K3 A( l: x" z2 h& X

# H, K3 A( l: x" z2 h& X

图6 POR开启电压和迟滞电压$ c: x% G: h$ c5 `# z

分析VDD上电过冲产生的原因:因为采用R99=7.5KΩ和R102=9.5KΩ分压,所以VDD上获得的分压为12*9.5(7.5+9.5)=6.7V,在上电瞬间,RT9018还没开始工作,内部电路不需电流,VDD上的分压可以拉到6.7V,RT9018开始工作之后,内部开始拉取电流,产生的跌落现象就和图2是一样的,具体原因也是一样的。

) r8 `7 O: q- R f8 M( M+ n

u1lunljk50r6403025007.jpg

2 }$ s. d2 u9 d# m, e如图7所示为规格书中,VDD与VOUT之间的瞬变响应特性,左右分别为在负载电流0A和2A情况下,VOUT随VDD变化的动态响应特性,由图可知,在VDD瞬变过程中,VOUT会产生一定的跌落和毛刺。观察这个图,可以不难理解图2和图5中为什么没有电压输出了,在VDD获得分压5V的情况下,流经R99的电流为(12-5)V/7.5K=0.93mA,VDD从5V跌落到2.5V左右,由于VDD能提供的电流太低,动态响应能力太差,所以输出端无法正常输出1.5V电压。" W2 ~ V6 Z" G1 g

hisxsypptqx6403025107.png

% h( |2 `6 v' G图7 RT9018动态响应特性

+ |% r5 C. n4 c5 N3 r# W3、问题解决

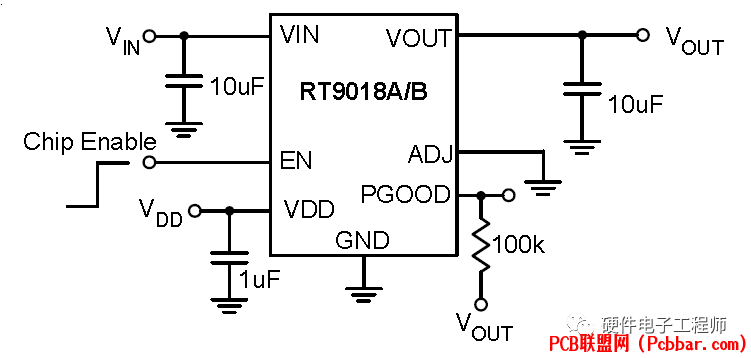

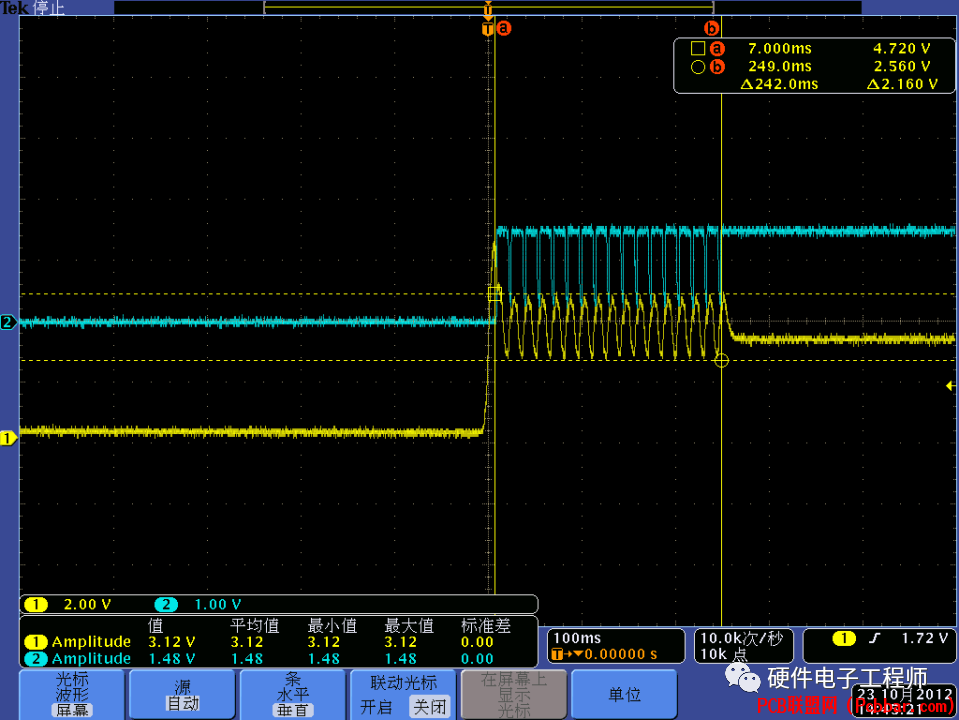

! y4 O1 S2 f. l后来发现在规格书,推荐的电路中,如图8所示,VDD输入端有一个接地的滤波电容,考虑到图2和图5中的VDD输入电压波形跌落是因为不能提供工作电流需要,而分压获得电流的续流能力不够,才导致跌落的,在这里接滤波电容的话,可以增强VDD输入端的续流能力。如图9所示,在VDD输入端焊接一个对地并联电容之后,VDD输入电压和RT9018的输出电压波形,可以看出,VDD在上电过程中有明显的震荡,但是因为电容的存在,这个跌落周期更缓慢,在大概240ms之后VDD上电波形趋于平稳,而且输出电压可以正常输出。" I) e" P0 m+ p. y6 f

motrpmqhpoe6403025207.png

9 O' ~% J2 m- I. C5 c图8 RT9018典型应用电路图+ G9 r$ }$ h; B6 s; Q# q

d05jdgkhxi56403025307.png

4 Q, l. }7 Y8 W( i3 ]图9 RT9018上电波形(通道1-VDD,通道2VOUT)

0 {- n" R2 F; [: n/ H分析震荡产生的原因:上电之后对电容充电,同时内部POR电路开始拉取电流,由于两个过程同时进行,电容一方面要充电另一方面还要为POR电路提供续流,而POR所需电流也不是一个稳定值,这样电容在开启阶段反复的充放电,具体表现就是一个震荡的波形。另外由于R102和1uF电容组成的回路要给POR电路提供续流,所以虽然分压电阻没变,相比没有滤波电容的情况,这里得到的分压也会相对更小。

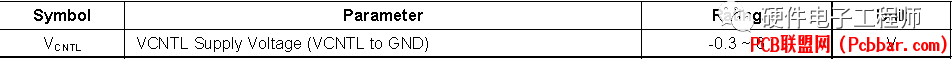

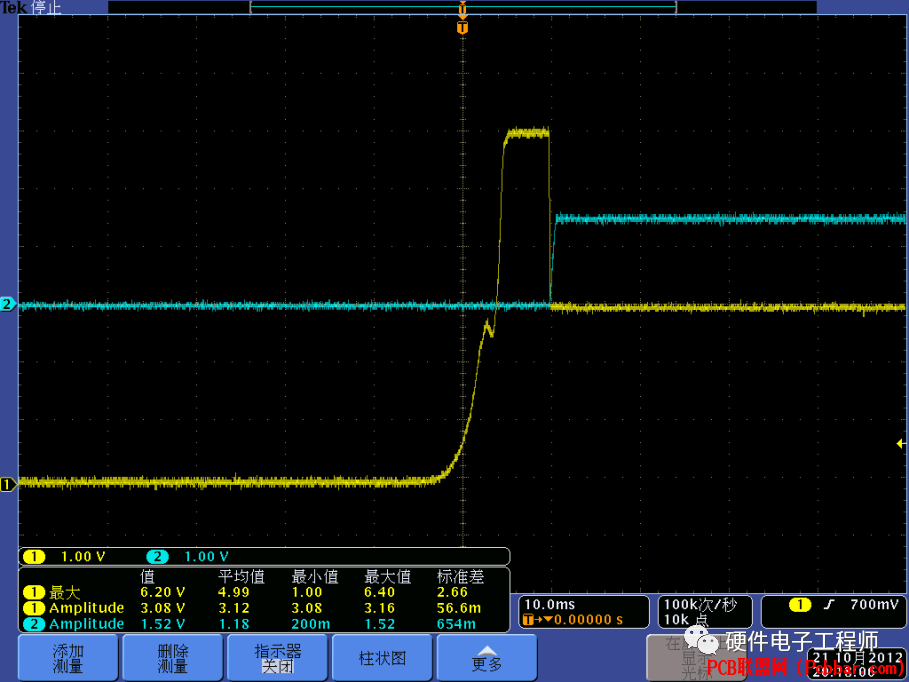

- r/ J/ f$ m7 b* B! u" G8 o在VDD输入端焊接滤波电容的话不仅上电波形不理想,而且需要改版,在不改版的前提下,我们找到了一个替代的方案。如图10所示为APL5910的典型应用电路,它的封装和RT9018是一模一样,其中VCNTL相当于RT9018的VDD引脚,为APL5910内部的控制电路提供电流。如图11所示,VCNTL可以承受的极限电压为-0.3~6V,正常工作电压为3.0~5.5V。

1 W. C* i3 u" ^, H

mcwjlrltbwu6403025407.jpg

! E5 W" J4 C5 @) a: o8 u& x, i图10 APL5910的典型应用电路

3 p( }! T# r& d6 X% P" m

uembbjryb0m6403025507.png

- ~: p* C( a/ y% r- }1 N

- ~: p* C( a/ y% r- }1 N

l7 c+ z. ?* a' V; g9 C, S

ikxzwqkgd1f6403025607.png

9 }/ h+ \( y# S5 ?+ H& Y

9 }/ h+ \( y# S5 ?+ H& Y

图11 VCNTL输入电压范围

) V+ l9 V5 F+ K3 k' m

+ y0 L5 w7 ^( }9 t; D X

5w2ltqdq0bj6403025707.png

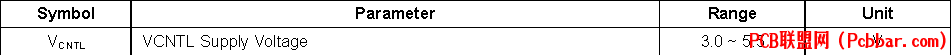

0 I$ T% {3 i/ ^) F图12 VCNTL电流需求

6 n$ y3 c* w0 s% c如图12所示为VCNTL正常工作下需要提供的电流典型值为1.0mA,在芯片关闭时需要提供的电流为20uA,按照单板原来的设计,VCNTL引脚是可以提供1mA的电流的。于是在原来的单板的基础上,取下RT9018,焊接APL5910,分压电阻R99阻值7.5KΩ,R102阻值9.09K欧姆,测量VCNTL输入电压和输出电压的波形如图13所示。APL5910输出端可以正常输出1.5V电压,但是问题是VCNTL的上电波形有一个很大的过冲,而且这个过冲已经超过VCNTL能承受的最大电压6V,长时间工作必然造成单板故障,为了解决这个问题,有两种设想:一是按照规格书的推荐,在VCNTL引脚加一个1uF的滤波电容,可以消除过冲。另一个方法就是调整分压电阻,在APL5910可以正常输出的前提下,如果过冲在可以接受的范围之内,可以保证不用改板。! A$ \7 V5 D1 Y. r5 L3 d

jebsmxq5b0u6403025807.png

/ I f$ u6 _3 A, t6 g* @

/ I f$ u6 _3 A, t6 g* @

图13 APL5910上电波形(通道1-VCNTL,通道2VOUT). T* n( `( S: f" X9 Y, T

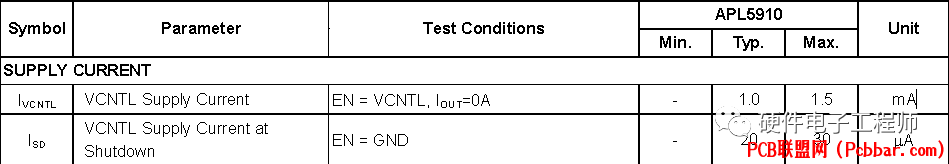

尝试将R102更换为更小阻值,如图14所示为R99阻值7.5KΩ,R102阻值7.5KΩ的情况下测量得到的上电波形。由图可知,VCNTL的上电过冲仍然存在,但是已经下降到6.2V,稳定后VCNTL的输出为3.08V,如果进一步减小R102的阻值的话,过冲会进一步减小,但同时VCNTL稳定后的电压也会减小,由图12可知VCNTL正常工作的电压范围在3-5.5V之间,为了不越出这个范围,分析过冲产生的原因:在上电瞬间,LDO还没有开始工作,VCNTL引脚对地阻抗很大,在LDO内部电路开始工作之后,VCNTL对地阻抗瞬间减小,流经分压电阻的电流增大,; I. j, e: d3 l+ J- m

ztuz0npkehx6403025908.png

' ?1 A. U5 O% C- H. P5 l, P# \

' ?1 A. U5 O% C- H. P5 l, P# \

图14 APL5910上电波形(通道1-VCNTL,通道2VOUT)

g" C# x b6 L如果将两个分压电阻阻值同步减小,流经R99的电流就会增大,在分电阻比值不变的情况下,流经R99的阻值越大,电流值越大,在R99电阻上的压降也就越大,由于上拉电压12V是一定的,那么R99的压降越大,那么VDD上的输入电压也就越小。从这个思路出发,调整减小R99和R102的阻值,当调整到R99=3.3KΩ,R102=2.2KΩ的时候,上电波形如图15所示,VDD上电时过冲最大值为5.0V,稳定后输出为3.2V,满足规格书中的设计要求,不会对芯片造成损坏。

B; o0 C f/ G- n! ]4 a$ n* A

enj3kvzz00x6403026008.png

" u; L( E+ B0 M3 ~4 ?% w0 G) j( U

" u; L( E+ B0 M3 ~4 ?% w0 G) j( U

图15 APL5910上电波形(通道1-VCNTL,通道2VOUT)! j$ _, v1 j: Z2 N/ h, k3 d! Q

分析过冲产生的原因:这里过冲产生的原因和RT9018是一样的,不同的是APL5910内部POR电路需要的最大电流为1.5mA ,所以没有产生跌落现象,开始上电之后POR启动之前,在VDD上获得分压为12V*(2.2 KΩ)/(2.2 KΩ+3.3 KΩ)=4.8V,内部POR电路启动之后,开始拉取电流,因为分压电路可以提供的最大电流为12V/(2.2 KΩ+3.3KΩ)=2.2mA,能完全满足POR电路的需求,但是在R102上的分压会减小,如图15所示只有3.72V,如果改版的话还是建议在R102处并联一个1uF的滤波电容。

- }+ `5 t5 Q; a- d. M

socwhaxt3fo6403026108.jpg

. p7 L- M* G% L5 H0 R0 C

. p7 L- M* G% L5 H0 R0 C

4、问题总结; Z* U! H8 w1 O. @( S" a" y& T

仅以该文致敬曾经趟过的那些坑,电路设计先吃透芯片手册。 |