|

|

半导体封装简介

# k7 H6 ^9 b0 e* P) b2 q+ ~, Q4 {

5 h$ @2 z1 p! N半导体封装是现代电子系统的核心环节,负责将芯片集成到功能系统中,同时保护其免受环境和机械应力的影响。封装的核心任务是将半导体器件(如CPU、GPU、存储器)连接到基板上,实现芯片与印刷电路板(PCB)之间的电气信号传输。传统封装以单芯片集成为主,但Chiplet(小芯片)与异构集成的兴起彻底改变了这一领域[1]。& ?2 t8 f' R# W) x0 u

V# E% r( ^) |

Chiplet是一种模块化半导体设计方法,将复杂系统拆分为多个可独立优化的功能块(如逻辑单元、I/O模块、存储器)。与传统的单片系统级芯片(SoC)不同,Chiplet允许采用不同制程节点和材料制造各模块。异构集成则通过先进基板将这些异构的Chiplet封装为单一系统,从而提升性能、降低成本并缩短上市时间。例如,AMD的Instinct MI250X计算加速器通过硅桥和扇出型再分布层(RDL)集成GPU与高带宽内存(HBM)。" n' @$ o) o4 g9 N* U% W7 d

基板技术的演进

* a7 L3 z$ Z& |+ ^( R4 v8 r/ K! o/ v; \! z; d; @7 m ^

为满足小型化、高互联密度和热管理的需求,基板技术经历了显著变革。7 p$ \4 D3 o( X7 `% y% @ I+ z' } I

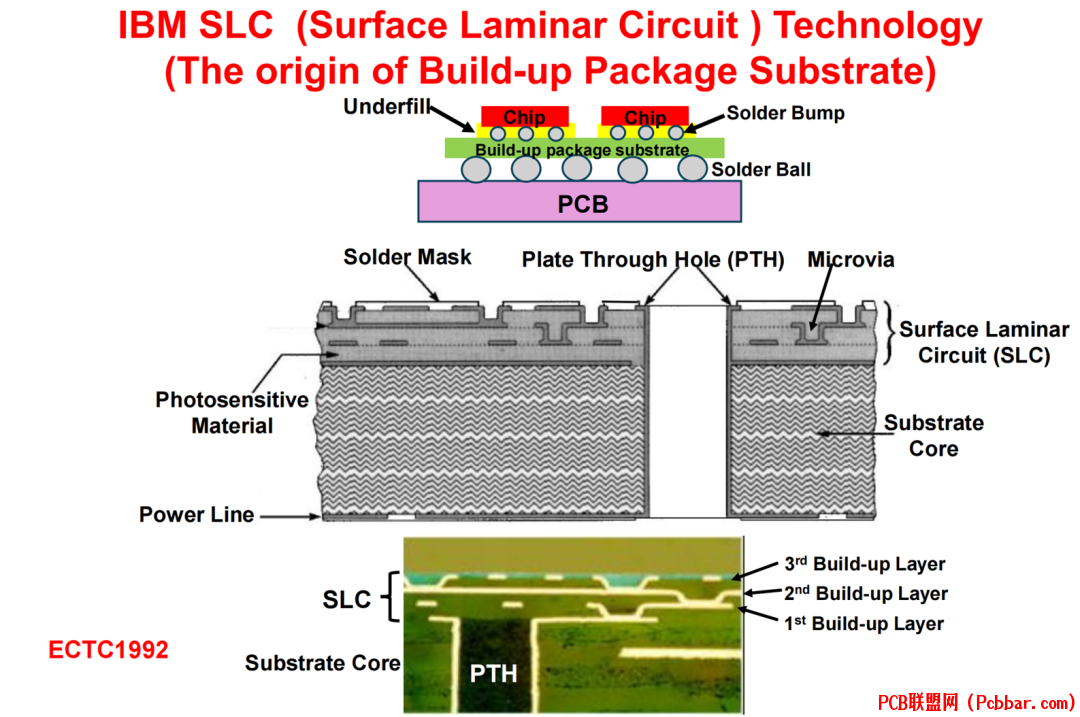

0 D# P4 ]4 `' F3 P早期基板:积层结构与扇出型RDL,多芯片模块(MCM)的早期基板采用有机核心上的积层结构IBM的表面层压电路(SLC)技术(图1)是这一领域的先驱,通过堆叠介电层和导电层实现高密度互连。积层基板因成本与性能的平衡至今仍广泛应用。0 J' L# F1 d0 [; S& B, U

zq4jgmzsiyb64035401218.png

8 T; l6 L0 F7 _

8 T; l6 L0 F7 _

图1: IBM的SLC技术,剖面图展示积层基板结构,包含微孔和用于连接PCB的焊球。9 Q# ?% S8 y0 M+ z2 g: l2 R9 A

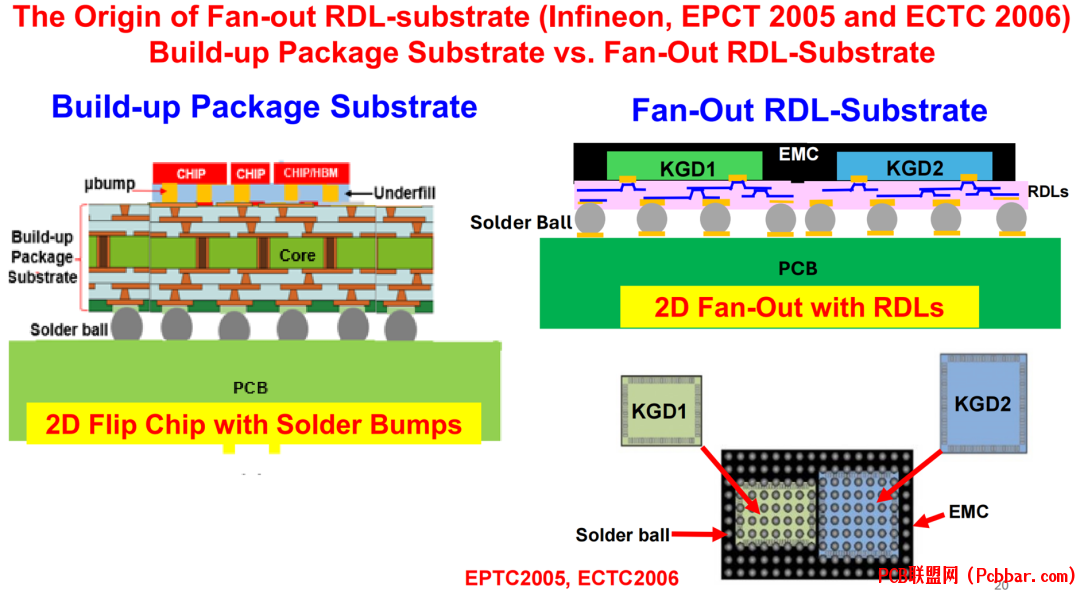

: N: B! i: x& [# h( n扇出型晶圆级封装(FOWLP)是一项突破性技术。与传统基板不同,FOWLP通过再分布层(RDL)在重构晶圆上重新布局连接,省去焊球和底部填充材料。英飞凌的早期研究(图2)展示了扇出型RDL如何实现更薄、更经济的封装,同时提升散热性能。苹果iPhone的A10处理器即采用FOWLP技术,以紧凑尺寸实现高性能。3 R) [$ n( x0 x! G- E

qhawasae0i564035401319.png

' o0 L4 b. y1 A7 U

' o0 L4 b. y1 A7 U

图2: 扇出型RDL基板与积层基板对比,英飞凌的扇出型RDL技术(右)省去了焊球与倒装焊步骤,相比传统积层基板(左)更简化。

/ d8 o4 \; ^: {# w7 N' c* O

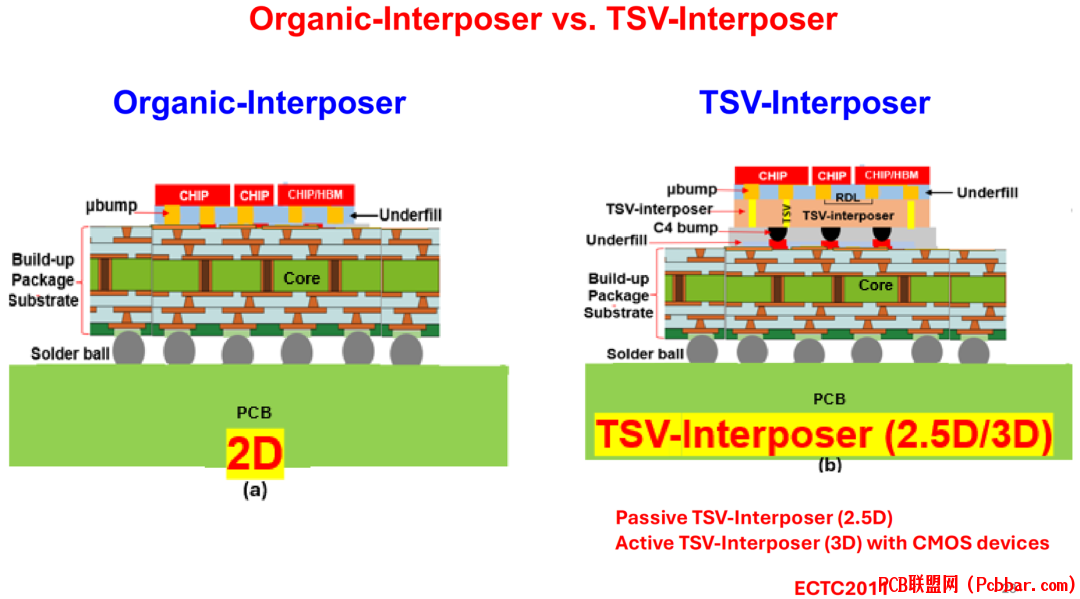

$ w( D2 r# h; m. t0 ]2.5D与3D集成:TSV中介层与混合键合,随着晶体管密度接近物理极限,2.5D集成应运而生。该技术利用硅通孔(TSV)中介层(图3)实现Chiplet的水平与垂直互连。TSV支持逻辑、存储器和I/O芯片间的高带宽通信,例如NVIDIA的H100 GPU通过TSV中介层连接逻辑芯片与HBM堆栈。1 L+ u3 A" o) e w/ s0 j

3lf2htnb1wf64035401419.png

5 R& ^$ l. I. q# p3 `: b( {7 m图3: TSV中介层与有机中介层对比,(a) 含硅通孔的TSV中介层;(b) 含嵌入式硅桥的有机中介层。

/ Q, d/ ^- V+ ~6 g1 F x% P8 ~5 f& {; T' N# }8 m$ N

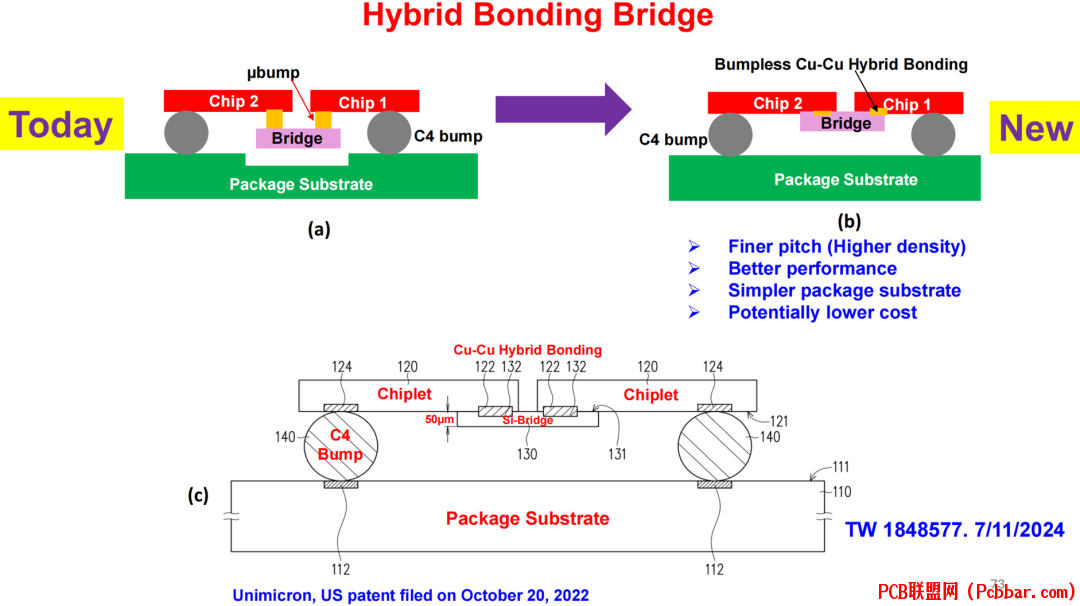

在3D堆叠中,混合键合(图4)以铜-铜直接键合取代焊球,降低延迟与功耗。英特尔的Foveros技术将计算单元堆叠在主动中介层上,而台积电的CoWoS-L通过硅桥实现超高密度互连。6 N- q3 x+ G* ^9 w

yqlst4rodl264035401519.png

1 C% l/ h G/ A图4: 混合键合桥接技术,无凸点铜-铜键合相比传统焊球实现更精细的互连间距与更简化的基板结构。# B& A3 \! `. @; \' ]7 N) \

先进基板的重要性

e u* e0 ~- W3 r# H' |! M- ?7 p7 N, H8 T

先进基板解决了性能、能效与可扩展性的关键瓶颈。

) t& Q/ E! p8 U7 v7 V! Q2 V1 Y: ]& G# m9 y4 r

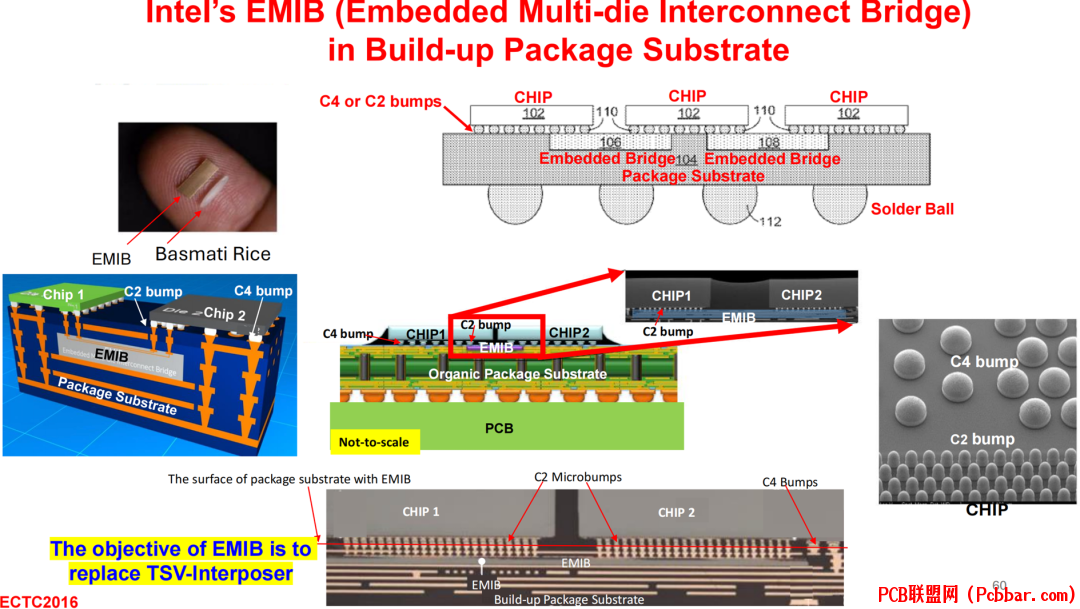

硅桥与有机桥接,英特尔嵌入式多芯片互连桥(EMIB)(图5)在有机基板中嵌入高密度互连,省去TSV中介层。EMIB在成本与带宽间取得平衡,例如英特尔Agilex FPGA通过微凸点连接FPGA与HBM。, I5 v3 Z8 |8 g0 H3 _3 ^, |, o

uwoe1kccvo264035401619.png

4 h5 P) }1 T% T图5: 英特尔EMIB结构,EMIB桥接(高亮部分)实现Chiplet间的局部高密度互连。

' A/ \( S- o3 T5 Y/ F9 ]& r, k" v% I ^6 C' D

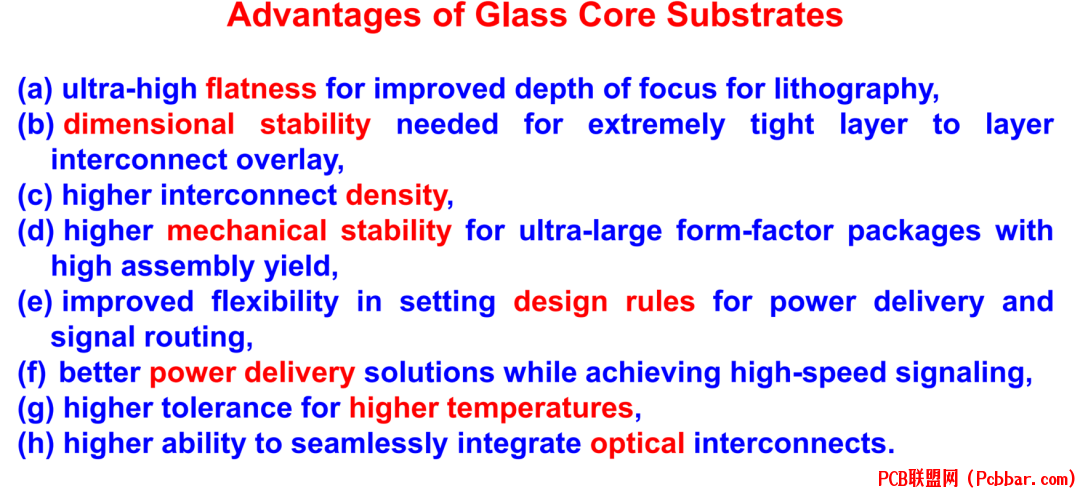

玻璃核心基板,英特尔的玻璃核心基板(图6)凭借超平整度、尺寸稳定性与10倍互联密度,成为AI与数据中心应用的理想选择。然而,玻璃与PCB的热膨胀系数(CTE)差异与初期高成本仍是挑战。; \& q" B, U8 C

apsbdfqsave64035401719.png

7 e7 ]/ h2 C4 C5 |* O n图6: 玻璃核心基板优势,核心优势包括机械稳定性、耐高温性及与光电子技术的兼容性。! e4 s; W* c, b/ C

2 [6 F) w" P, Y) }% R2 ~

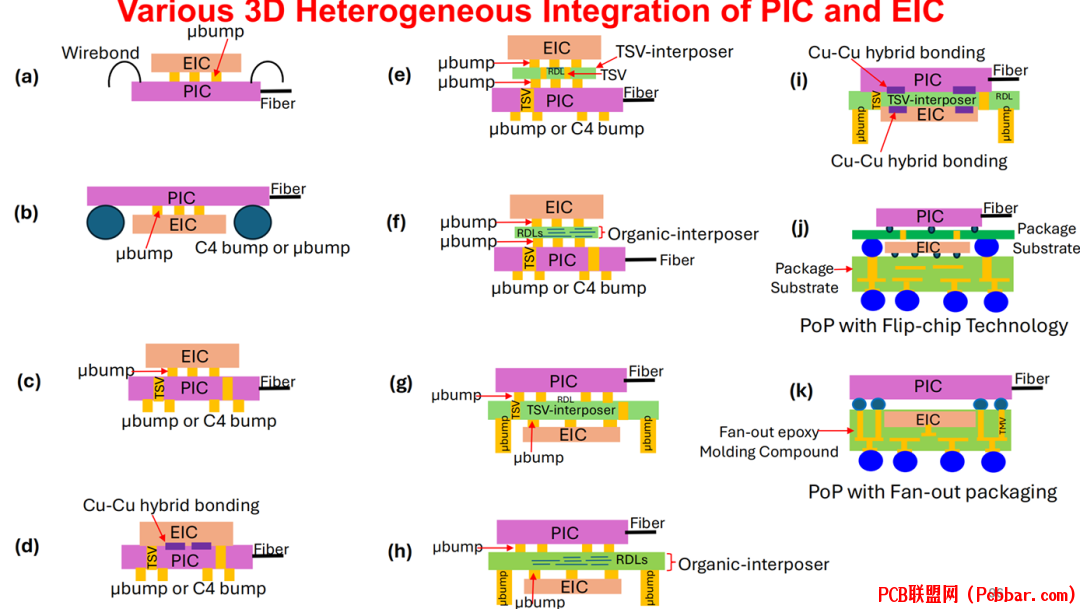

光电共封装(CPO),光电共封装(图7)将光电子集成芯片(PIC)与电子芯片(EIC)集成于同一基板,以光纤替代铜互连。思科的3D异构集成方案在玻璃中介层中嵌入激光器与波导,实现低功耗太比特级数据传输。

, J* a; Q& b! o6 v! }

kqa0ekvfha364035401819.png

) L8 i2 T! A; O' g9 e) T" q" U

) L8 i2 T! A; O' g9 e) T" q" U

图7: PIC与EIC的3D异构集成方案,多种配置展示光电子与电子组件的集成方式,包括TSV中介层与混合键合。

. r d" `: j) @6 e# Y: |8 a传统封装的当前挑战2 n2 E+ N, \, r4 i; D- m2 F# J

`9 p+ @, `" u0 @尽管技术进步,传统基板仍面临以下限制:- I% o& y Y$ e/ p& w( s( V

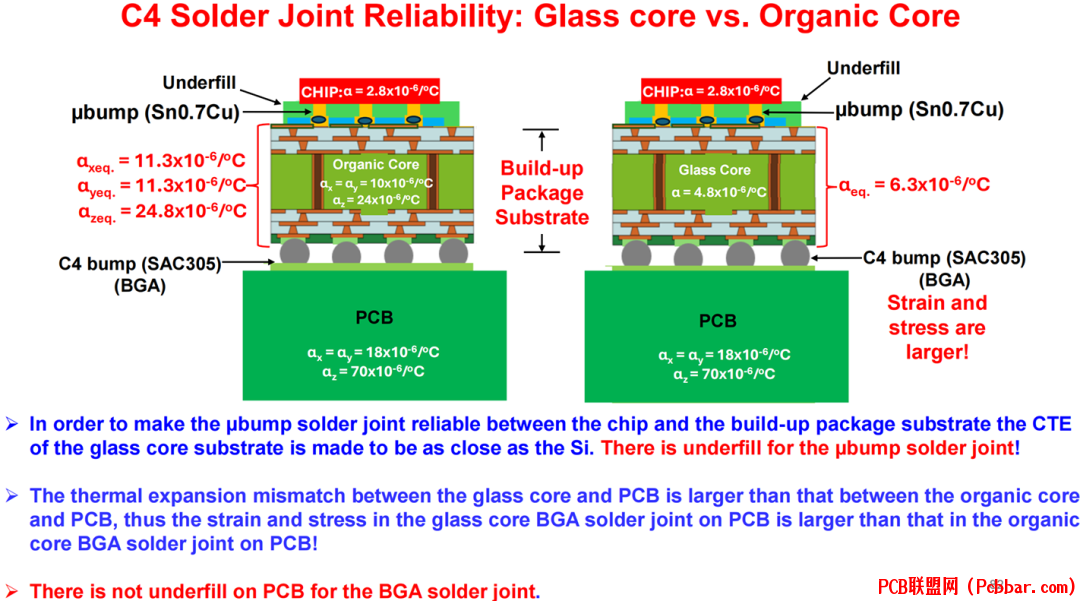

3 ]& z5 K6 y: ~热应力与机械应力,材料间的热膨胀系数(CTE)差异导致焊点失效。例如,有机基板(CTE约24 ppm/°C)比硅(2.8 ppm/°C)膨胀更剧烈,造成微凸点应力(图8)。玻璃基板(4.8 ppm/°C)虽缓解芯片级应力,但因刚性在PCB界面产生新问题。

" y9 n! W; {4 |% H x0 o! ?

o4m0p5kr42c64035401919.png

8 g0 J3 l( M2 ?" {8 Y# J0 d图8: C4焊点可靠性对比:玻璃与有机核心,热应变对比凸显芯片与PCB级可靠性的权衡。% n. e( u9 n6 `$ v E% v

9 M9 _4 p4 A+ t, Z, z/ K, l

良率与成本问题,TSV中介层与混合键合等技术初期良率较低。玻璃基板虽前景广阔,但需构建全新制造生态,初期成本与良率问题显著。7 g) |" M' x {0 _6 @) f, y

# S/ o; s' {2 L

设计复杂度,集成多厂商Chiplet需统一接口标准(如UCIe)。异构系统还需先进散热方案,例如AMD的3.5D Instinct MI300采用液冷应对堆叠芯片的热管理。: a" b* p F; J2 ?) Y. Z/ |& _

总结

0 n4 k. a$ U3 X/ q

) n; H O5 m# R1 W, T先进基板技术是延续摩尔定律、满足AI与高性能计算需求的关键。从TSV中介层到玻璃核心,这些技术解决了带宽、功耗与散热难题。然而,克服成本、良率与标准化障碍仍需产业链协作。英特尔玻璃基板与台积电CoWoS-L路线图表明,未来封装技术将依赖材料创新与系统级协同设计。$ K' V( ~ _0 t1 _2 o) `7 E8 A

参考文献3 X4 A- |' }/ `

5 A) @ h+ h) Y8 M# A

[1] J. H. Lau, "Advanced Substrates for Chiplets and Heterogeneous Integration," presented at the IEEE/EPS Distinguished Lecture, School of Integrated Circuit, Tsinghua University, Beijing, China, Jan. 22, 2025.( @9 \6 R3 H3 x! i: c

END

+ Z) e ]" G" }2 Z7 k1 o$ r2 j3 J+ a软件试用申请欢迎光电子芯片研发人员申请试用PIC Studio,其中包含:代码绘版软件PhotoCAD,DRC软件pVerify,片上链路仿真软件pSim,光纤系统仿真软件pSim+等。更多新功能和新软件将于近期发布,敬请期待!

5 I- S3 H3 D! l1 Z; G! s+ b点击左下角"阅读原文"马上申请

: j4 r7 q j2 M2 S* }

/ I1 r, t6 k6 ]1 c; N/ m欢迎转载

; j2 ~; U/ m% g* I$ w) J0 Z- m+ D9 L0 |' P8 @1 R: w0 _7 m7 i

转载请注明出处,请勿修改内容和删除作者信息!! Z% K0 j% ^+ l9 N: p( D

- Z; I/ j& \% ?( }, S( W+ z# w; \! }. y+ g |# }. J+ Y

5 e0 G9 w- m2 s! Z, d8 _

i03xutnow3a64035402019.gif

- `( h' l; i, q) Q8 Y5 X7 L: q7 | |: d" O3 d$ c! P

关注我们

y. e+ c$ q/ k3 c0 M1 }: j, _' K

# y' ?3 U( g( m7 w I4 W E! }0 Y" @% y

omh34fuenyy64035402119.png

. c( T3 J4 O( y+ C: B7 V( a |

8 u* ?0 M, ~2 I! Y0 S9 X. z

qjxspceenpn64035402219.png

. t2 E5 H- [1 G, G: \( K# T

. t2 E5 H- [1 G, G: \( K# T

|

( w/ S+ l) m" c9 R6 C* q# ^* @# F

i3y2ny4wj5c64035402319.png

$ M; f/ p! P" x& e/ K1 K4 Q) h |

, [) y+ ]9 Y3 e/ O( u* W

3 K$ u" N% d9 c. P) b) ?

( n* }% r% x$ x# u$ O2 p' L% \3 D | a6 ?. Q

关于我们:8 X& T7 ?- _; B3 b

深圳逍遥科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。& Z& O* I* \5 g$ }& M; I

! ~; ?( {* Y: r5 P1 {9 Dhttp://www.latitudeda.com/

" o) Z. q+ e" \3 z' u9 C5 E% z# x; Z(点击上方名片关注我们,发现更多精彩内容) |

|

/1

/1