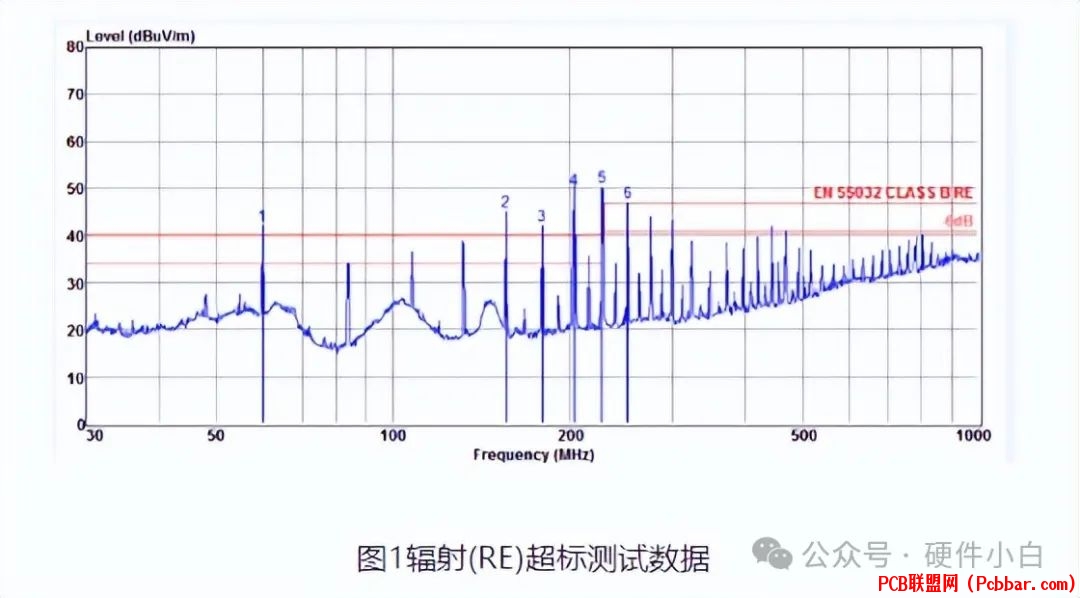

某音响产品的空间辐射(RE)测试不通过整改案例分析,下图-1是产品的空间辐射(RE)测试数据,产品在空间辐射测试时150MHZ~300MHz频段有较多的谐波干扰数据超标,导致产品emc空间辐射测试不通过,如下图1,这是一个典型的时钟电路干扰波型: W0 n$ b2 D$ G9 p/ \5 d" g- }

* t& ~$ X$ Y6 G

fnyrnnfh24b6408177230.jpg

9 S1 z& R, M w; Y1 z. i R干扰机制及原因分析

' { C9 o7 R( [% V结合以上测试数据分析,导致辐射测试不通过的主要原因可能是产品电路设计中晶振或时钟信号之间的通信形成的干扰,在电路设计中晶振和时钟信号之间都要有匹配电路等措施;在电路中晶振及其相应时钟信号由于其周期特性,会因时钟边沿速率过快引起信号完整性和电磁兼容等问题,成为PCB的主要骚扰源,并产生较多谐波干扰,导致空间辐射测试超标。通常情况下,当PCB电路设计中有品振及时钟信号电路时,晶振线路布线设计时是否增加匹配电阻和去耦电容,或只加了去耦电容未加匹配电阻,以及时钟信号线上是否有增加匹配电阳及去耦电容对产生EMC河题,造成EMI干扰会很大,对EMI测试结果也有很大的影响。匹配电阻在电路设计中作用有阻抗匹配和减缓信号上升沿的作用。阻抗匹配因PCB上的布线都有一定阻抗,会因布线问题产生阻抗失配,引发信号的完整性产生电磁干扰即一般会采用源端串联一个电阻的方式进行匹配来保证信号的质量。减缓信号上升沿匹配电阻与电容的低通滤波电路,为反映信号响应速度,从而影响高频干扰,匹配电阻的取值最好在20~100Q之间,也可在确保信号质量的前提下其值越大越好。去耦电容主要应用于信号电路设计中,完成去耦、振荡/同步及时间常数的作用,振荡/同步:包括RC、LC振荡器及晶体的负载电容都属于振荡/同步。在PCB布局设计时,若要保证时钟电路有足够的去耦电容,就必须保证去耦电容的选取要满足预期的应用。自谐振频率需要考虑抑制时钟的谐波,通常我们都要考虑原始时钟频率的五次谐波。同时在高频电路中会因回路电感的影响,需要在PCB上放置有效容性的去耦电容来达到良好的去耦效果。在实际应用中通常采用大电容滤低频,小电容滤高频的原则来选取去耦电容值。

3 ~2 m# w: { P0 e6 Z2 @解决思路分析

3 Q$ C: P4 G7 I6 @5 O+ y* U结合以上原因根据测试数据和产品设计分析,可能是功放MCLK时钟信号干扰,我们整改时先将功放的MCLK时钟信号断开,测试时干扰仍然存在,测试数据变化不大,可以判断跟MCLK时钟信号关系不大;再次查看原理图,发现产品的是12.288MHz有源晶振,如上所述,有源晶振在没有匹配电路的情况下很有可能产生干扰,成为干扰源,于是怀疑是该晶振干扰,将晶振电源断开,150Mhz~300Mhz时钟干扰频点现象消失,基本可以确定是该有源晶振造成谐波干扰。在对该晶振部分电路进行近一步检查分析,发现该晶振下方没有铺地,附近的地面积也较少,这样该有源晶振本体产生谐波频率干扰,在没有相应的匹配电路和地回路的情况下,无法通过匹配是电路和大面积的地回路进行有效的去耦和滤波,导致造成EMC测试严重的谐波频率干扰,空间辐射测试不通过。3 z5 y% f8 D7 X1 `) e% J6 N

整改方法及对策8 _! J& \ S' _

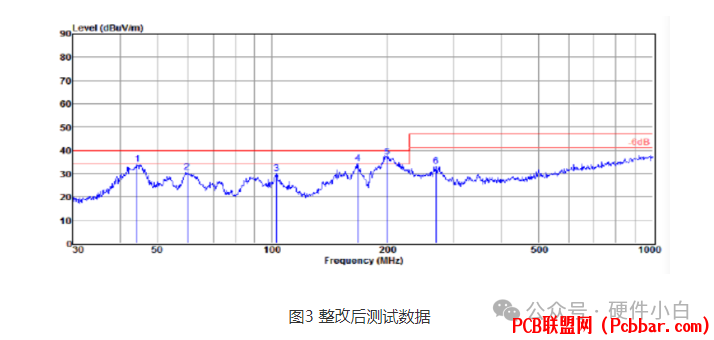

经以上分析,于是我们增加了如下对策后测试通过,整改对策如下图2,整改后测试数据如下图3所示:3 M8 T! {7 T( `9 B

1.在X1有源晶振外壳与周边增加接地连接;! W& j3 b5 J3 }) e! z5 ?

2.C31位置滤波电容增加接地连接,15pF改为33pF电容;:

1 F. e; q7 C/ E. A4 w' j3.将功放I2C MCLK时钟信号R3位置电阻33Ω电阻改为100Q磁珠,靠近X1晶振位置12C MCLK信号引脚串600Q磁珠。 u( W7 K1 e' R; s9 A# @$ i5 ^

/ G7 ^$ F9 U ?( Z; s! Y

; A, F$ g0 |$ Z6 Q1 V% Q' ~& f6 F

longf2z2ltc6408177331.jpg

2 |9 u9 X* T5 _$ h/ K4 a8 u' U; ]4 h0 K9 _3 C

1 F5 p. L/ b* @5 c0 m5 w

0yjbnhyb2k06408177431.png

A3 {* t2 Q# r l. U! n( y) @4 _+ h" p2 q: ^( O F# o( {- O

3 a" L A3 N$ v0 t( i

4 M: U. T! i! z/ [* z/ ~1 D1 z }

8 Z7 G: ^. V* c总结- o2 Q3 D7 [, r7 W/ M

对于这种典型的有源晶振、时钟信号整改,我们需要先了解其干扰机制和原理,定位其干扰路径、分析其受干扰电路或模块,找到问题原因所在,才是解决问题的关键。一般的处理方法如屏蔽、接地、旁路、去耦、阻抗调整、电容滤波等都是解决有源晶振、时钟信号谐波干扰的有效手段。往往我们在整改过程中,只有找到干扰途径和干扰源,才能采用最简单的方法、最低廉的成本来达到最有效的测试结果,通常情况下使用的整改方案越简单,实现起来就越容易,也越容易达成解决问题、降低成本的目的。 |