1. 差分放大器结构# Q7 S9 I/ r) X2 j @6 f0 Z

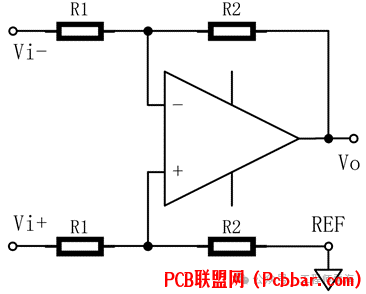

. p& g$ W8 V, O0 H. \7 m话不多说,直接干货,图1是差分放大电路的基本结构,由一个运算放大器和4个外围匹配电阻组成,常用来进行电流检测或差分信号放大,差分放大器有几个固有的弊端,如果不了解这些弊端,将影响我们的电路设计,看看这些弊端,你知道几个?* E. a& z, l6 y% M* D0 |6 \5 V% J

& u: W5 v& ~( T7 j+ D

v3gwpggp5tf64078816037.png

. s1 E2 H# h- X9 J4 @; G9 {+ J图1 差分放大电路

% ~2 Q2 |2 _8 |: @! Q* M* ^- {7 q* a- r& Y

2. 差分放大器弊端一:输入阻抗低) V) H, h3 \6 j7 }- y* ^

差分放大器的输入阻抗非常低,这与它的匹配电阻相关,而且差分放大器两个输入端的阻抗并不对称。怎么计算两个输入端的输入阻抗呢?% x! J( \7 w+ ]# A2 S( n

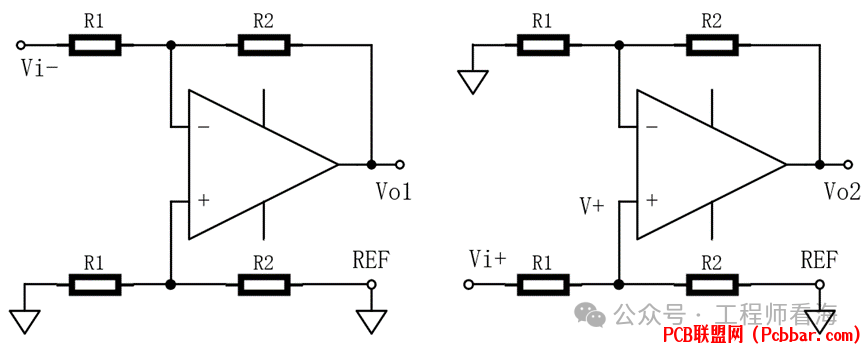

如图1 中,计算Vi-的输入阻抗时,我们只看Vi-,忽略Vi+,参考图2 左图。此时的电路是一个反相放大的结构,由《运放秘籍》可知,反相放大电路的输入阻抗就约等于输入电阻R1。! a/ U1 Y, N- w" P

* V n7 Q$ F, G$ E( {: Q0 \

cs2r2rokjoo64078816137.png

. I5 a$ r( N# K8 \$ c" I3 \4 O图2 差分放大输入阻抗计算8 b: c4 i, D9 s# G. Y' L2 z! _

% t" O3 h. @ _- }' Q( w$ w计算Vi+的输入阻抗时,我们只看Vi+,忽略Vi-,参考图2 右图。此时的电路类似一个同相放大的结构,Vi+是被R1和R2分压后再被同相放大的,Vi+经过R1和R2到地,因此,Vi+的输入阻抗大约是电阻(R1+R2)的值。/ Q6 b% b2 \7 u2 [0 G6 Y, I) f

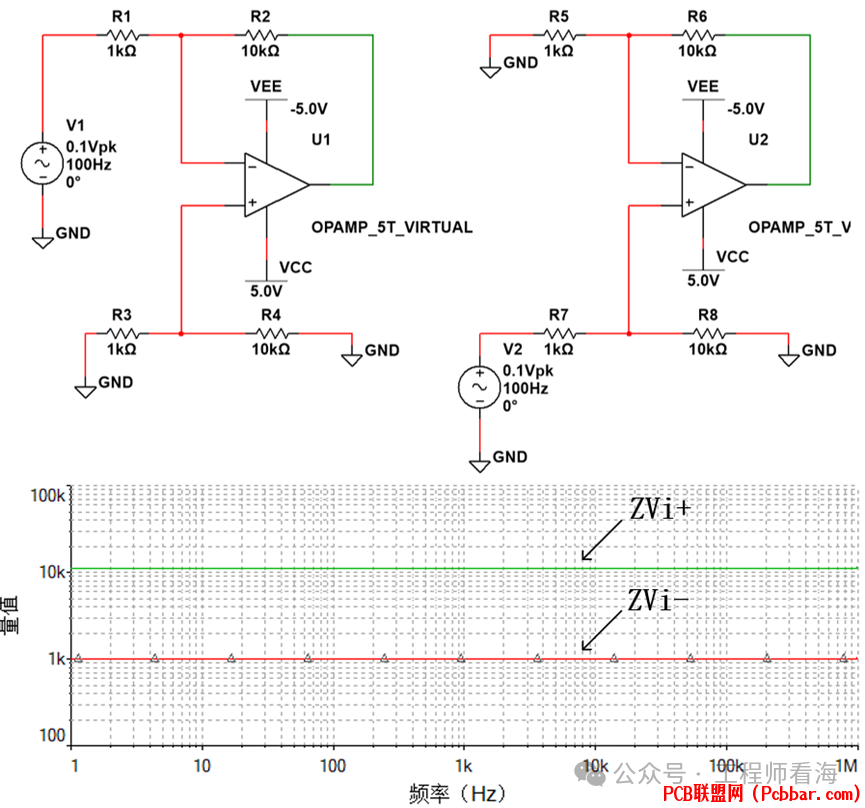

我们做下输入阻抗的仿真,见图3 ,Vi-的输入阻抗是1KΩ,Vi+的输入阻抗是11KΩ,与我们前文分析的一致。+ D5 u1 u4 l7 x+ c8 L

# x) R: J0 Y7 K/ W. [8 m/ S8 y- x

esiht4f5abi64078816237.png

1 F! D( O9 Z; r5 d4 J! n3 g

1 F! D( O9 Z; r5 d4 J! n3 g

图3 差分放大输入阻抗仿真4 U0 }" B* z8 Z

; U, o m, U. u [ H差分放大器的输入阻抗不但低,而且两个输入端的阻抗并不对称,如果连接到差分放大器的信号源的两个引脚源阻抗不匹配,也会降低CMRR,这就是差分放大电路的二:共模抑制比低。9 p) o, z! W/ Z0 j

/ R9 b( K: ?+ p3. 差分放大器弊端二:共模抑制比低

9 d) q& Y6 e. |/ p& L差分放大器最完美的状态是图1电路中的两个R1完全相等、两个R2完全相等,然而,我们无法找到两个阻值一模一样的电阻,常见的电阻也有1%的误差。这会使得电阻失配,将大大降低共模抑制比CMRR。

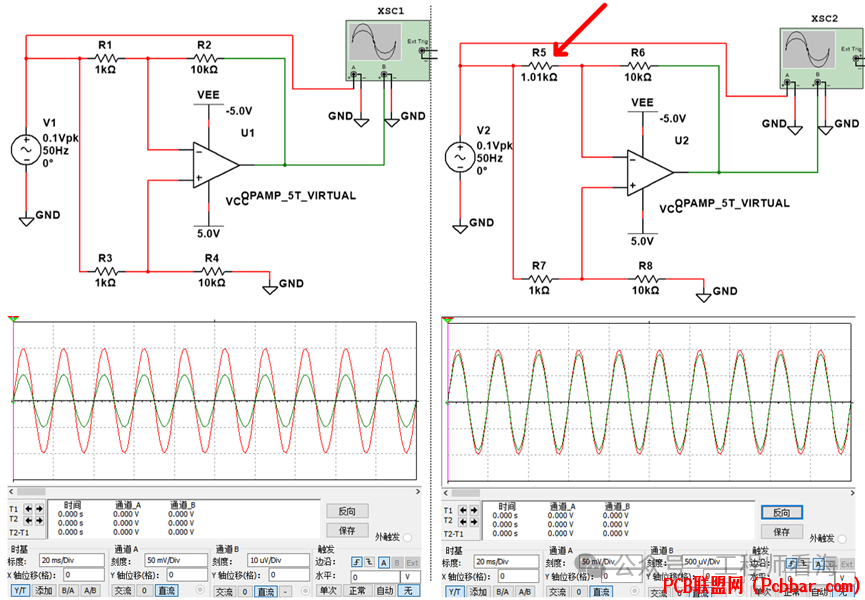

9 j. s8 _# o# M1 ]2 G图4 中,我们简单体会下差分放大器的CMRR,左边仿真图中,电阻是完全匹配的,输入的共模信号是0.1V@50Hz,此时输出是10uV,也就是说0.1V的共模输入信号被转换成了10uV的输出信号(虚拟运放模型的CMRR是100dB),换句话说就是,在外围电阻完全匹配的情况下,差分放大器的CMRR并不是无穷大,这受限于运算放大器。6 Y: G% L6 K# n

) c2 {$ v! {* N6 }

45313pbivmm64078816337.png

( i" u' ]6 G9 s$ n1 L/ ?

( i" u' ]6 G9 s$ n1 L/ ?

图4 差分放大CMRR与电阻失配- X X8 D4 f$ F3 V1 W: X5 `# J( w

( K1 b5 J( r$ k1 \6 h P( ~

而图4右图中,我们只把其中的一个电阻,按照最大误差1%从1KΩ改成了1.01KΩ,则在相同共模输入的情况下,输出变成了大约1000uV,是左图的10uV的100倍。这就是电阻失配,将降低共模抑制比,使得抑制共模干扰的能力大大降低。

$ y2 f# F! n$ B- _# N3 J6 O能不能增加差分放大电路的输入阻抗和共模抑制比?于是,就有了经典的3运放仪表放大器。 |