|

|

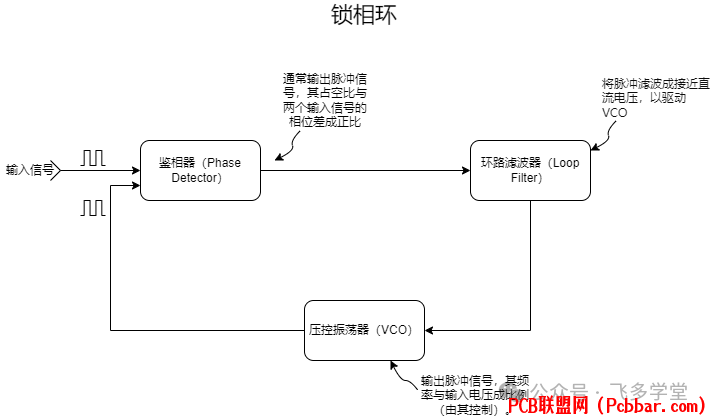

1、锁相环锁相环电路(PLL)是一种利用反馈控制原理实现频率和相位同步的电路。它广泛应用于通信、计算机、仪器仪表等领域。

F: I. @9 }% L9 o# J6 i2 Z

! }8 b0 i( ~1 d4 s9 u4 _锁相环电路的基本原理:

; m+ m9 z. h9 f7 C" Q锁相环电路由三个基本部分组成:鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)。- h+ m" M7 N4 `3 k3 a) X, O, f

. B7 j+ l% O- b

p52of45voph64059201936.png

V* K/ |7 t9 t+ z# c! j- O

V* K/ |7 t9 t+ z# c! j- O

如果是在手机上阅读本文,点击图片可放大。

5 P. W: i7 W. b$ |

! t: T" q5 c/ J; o$ c2 C锁相环的工作原理是:鉴相器如果检测到两个输入之间的相位差,鉴相器将输出与相位差成比例的脉冲信号,这些脉冲信号将被滤波成 VCO 的输入电压,该电压将调整 VCO 的输出信号频率和相位,并试图消除鉴相器两个输入信号之间的相位差。

# w2 m) j1 O( f1 N* A上面的工作原理和负反馈运放差不多,运放在负反馈时总是竭尽所能试图消除其两个输入引脚之间的压差。% ^/ f% D% s2 V% L7 p1 u \) L* _+ r; A

在许多情况下,环路滤波器实际上不过是一个简单的低通滤波器,可能是一个简单的RC滤波器。其主要任务就是从相位检测器中取出脉冲,并将它们转换成一个控制电压,用于控制 VCO。

' m& ^7 Z8 ^" r; ?. E/ o

j9 ^# b/ `" ?! q' S8 d锁相环电路的应用:

3 ?) z0 h8 [: A+ b4 g. P频率合成:锁相环电路可以用于频率合成,即利用一个基准频率产生多个不同频率的信号。频率同步:锁相环电路可以用于频率同步,即将两个或多个频率不同的信号同步到同一个频率。调制解调:锁相环电路可以用于调制解调,即将信息调制到载波信号上,或从载波信号中解调出信息。信号恢复:锁相环电路可以用于信号恢复,即从一个噪声污染的信号中恢复出原始信号。

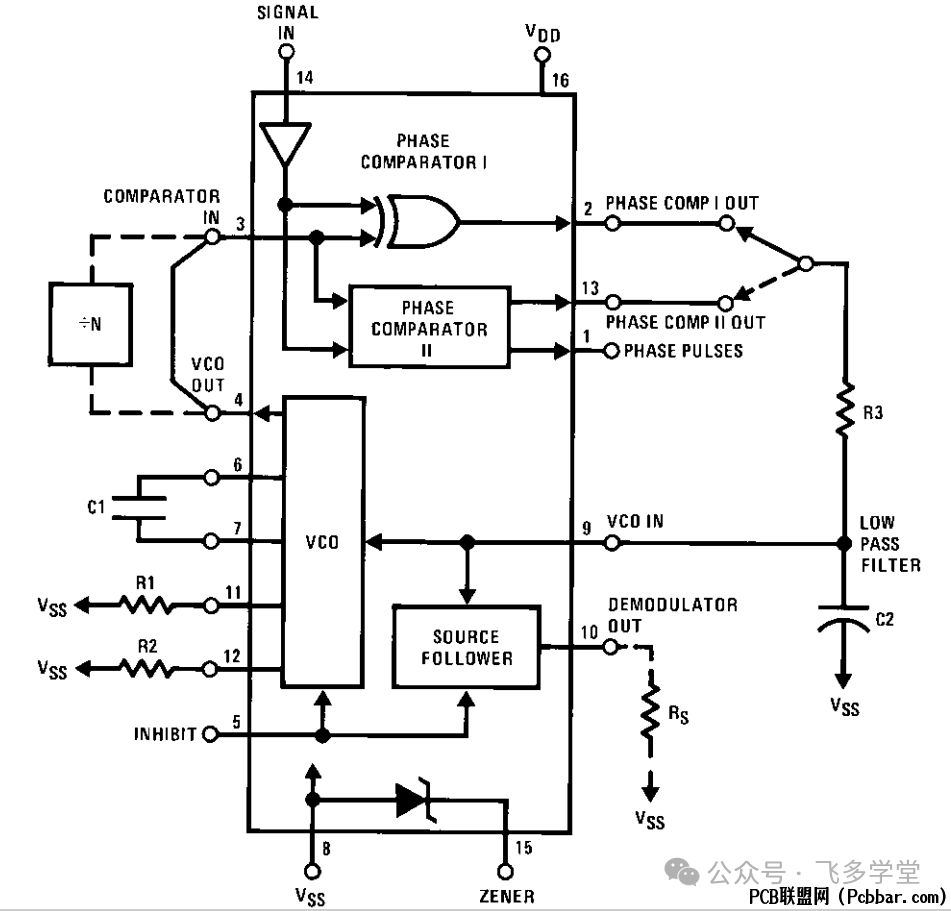

& H E5 H2 k: z; q# o2、CD4046CD4046 芯片是一种由 CMOS 工艺制造的锁相环 (PLL) 集成电路。它具有以下特点:

! Y% T1 L3 u0 @; Z. B电源电压范围宽: 3V 至 18V输入阻抗高: 约 100MΩ功耗低: 在中心频率为 10kHz 时,功耗仅为 600μW

0 v+ r/ i) _/ a0 I! S3 n* B0 dCD4046 芯片内部包含以下功能模块:

! Q& T0 l0 J1 p9 C( _" K鉴相器: 比较两个输入信号的相位差,并产生一个与相位差成比例的误差电压。环路滤波器: 滤除误差电压中的高频噪声,并将其输出给压控振荡器。压控振荡器: 根据环路滤波器的输出电压调整其输出频率和相位。1 E+ }4 {: f. o; J

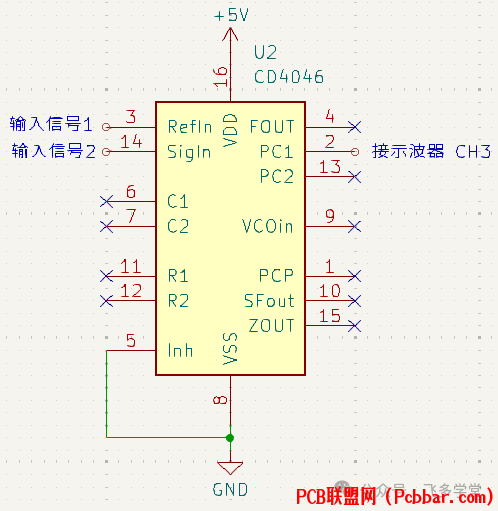

CD4046 的框图如下:

5 P u( C- m( Q( l4 h& I

; I5 z. h/ }, [$ }- J" @7 K r8 g Y

zgreqgxwaog64059202036.png

/ r! J& {% F4 c4 D/ u2 d8 T5 u

! `. `4 f/ X( r% ^8 WCD4046采用的是 RC 型压控振荡器,必须外接电阻电容作为充放电元件,上图中外接电阻 R1 和 电容 C1 决定了 VCO 的振荡频率。

' J m% j; ^- ]外接电阻 R2 电阻决定控制电压为零时的最低振荡频率。

' Z7 x0 P; p8 o2 |0 F- j8 j- O9 o1 Y3 A' S' a1 ~

/ b) C4 H, M' K& S. k. Z' ~

引脚定义如下:" X3 v1 X6 D3 l1 ^

1 引脚:鉴相器 2 相位输出端,环路锁定时为高电平,环路解锁时为低电平. O% I! d- \2 U# q- V' A+ v0 O$ ]% X

2 引脚:鉴相器 1 的输出端" _) Q h. R- k% p; a

3 引脚:比较信号输入端, p; d1 w2 e2 W" f) u

4 引脚:VCO 的输出端

' Y/ g+ U; O2 Z j9 O9 r5 引脚:禁止使能。高电平禁止,低电平允许工作

3 y. C- l$ J& ^, \# Q( r8 \8 _6 引脚:接外部振荡电容# S8 s1 _& P- ~$ n8 r

7 引脚:接外部振荡电容, N( c2 y9 J; C0 O

8 引脚:电源负极

5 j! l/ l& c2 b9 引脚:VCO 控制电压输入

- y$ [7 y( P# ~8 n- ?/ X10 引脚:解调输出端,用于调频解调8 c; w* X- S8 U2 p x

11 引脚:接外部振荡电阻

! L) |* L [4 A# m: _/ S+ _12 引脚:接外部振荡电阻

% U: n$ H2 N2 ^14 引脚:信号输入端

2 e: M0 W8 d7 n4 m: l) _. W15 引脚:内部独立的齐纳稳压二极管负极

# a& f+ i7 K$ B: c% |5 O16引脚:电源正极

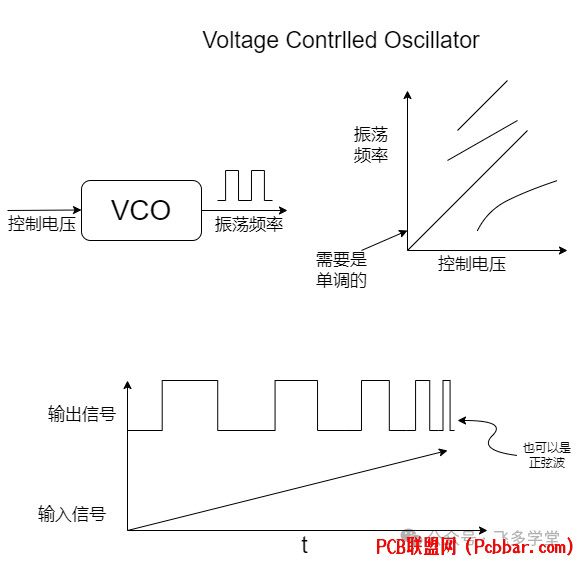

) R+ S$ T" C. Z7 R$ Y6 B3 VCO 原理和实验VCO(电压控制振荡器)实际上就是一个振荡器,其频率可以通过外部电压来改变。控制电压和输出频率的关系基本上是线性的,它可能有一些偏移,甚至可能有一些曲线。在使用范围内它需要是单调的(monotonic ),意味着斜率始终必须为正。否则会影响反馈,导致环路无法工作。8 F; x# q* V4 p# k Q7 [" M' W

" ^: K8 I; h' d# G

uqblyc1gx2r64059202136.png

1 q( [' a; @! |* A2 ^- x) \% q5 V) F9 }

3 J# H+ o" P# o! R7 ^8 Y9 o从上图中可以看到,如果输入的控制电压随时间线性增加,输出频率会随时间增加得越来越快。

: ~# l6 f6 }5 O, y5 Z2 M* QCD4046 内部集成了一个 VCO, 我们使用它学习和观察 VCO。CD4046 采用的是 RC 型压控振荡器,必须外接电容C1和电阻R1作为充放电元件。当PLL对跟踪的输入信号的频率宽度有要求时还需要外接电阻R2。由于VCO是一个电压控制振荡器,对定时电容C1的充电电流与从9脚输入的控制电压成正比,使VCO的振荡频率亦正比于该控制电压。当VCO控制电压为0时,其输出频率最低;当输入控制电压等于电源电压VDD时,输出频率则线性地增大到最高输出频率。VCO振荡频率的范围由R1、R2和C1决定。由于它的充电和放电都由同一个电容C1完成,故它的输出波形是对称方波。

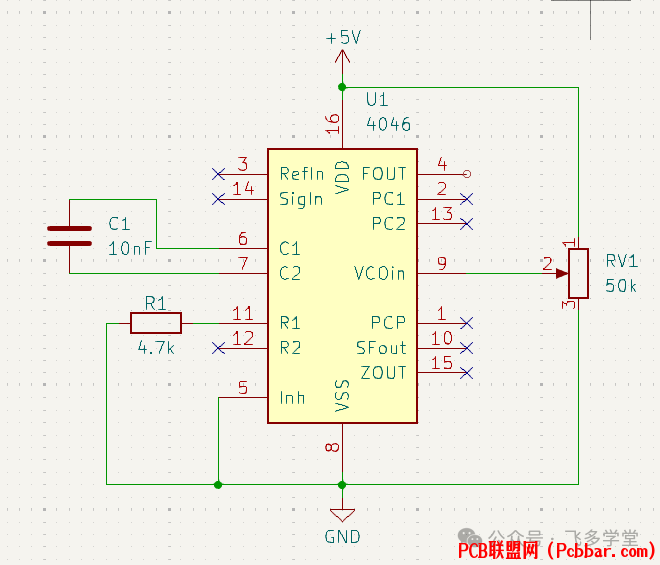

3 ]5 q% {' H% y& h( @0 w0 N我们给芯片使用 5V 供电,11脚接 4.7k 电阻,6脚和7脚之间接 10nF 电容,9脚上接 50k 电阻,用于改变 VCO 控制电压,其余引脚悬空。

% x& _, c( _7 P( p O

2 k' l" H7 |9 {VCO 实验电路如下:

- G1 U. s2 c" |' D

2 F2 |' g4 _! Y* n s! a+ h

j2rminxmcpc64059202236.png

7 t! a! C. X* O# D7 t# {

7 t! a! C. X* O# D7 t# {

3 A& b' n7 O& S5 h& P) u

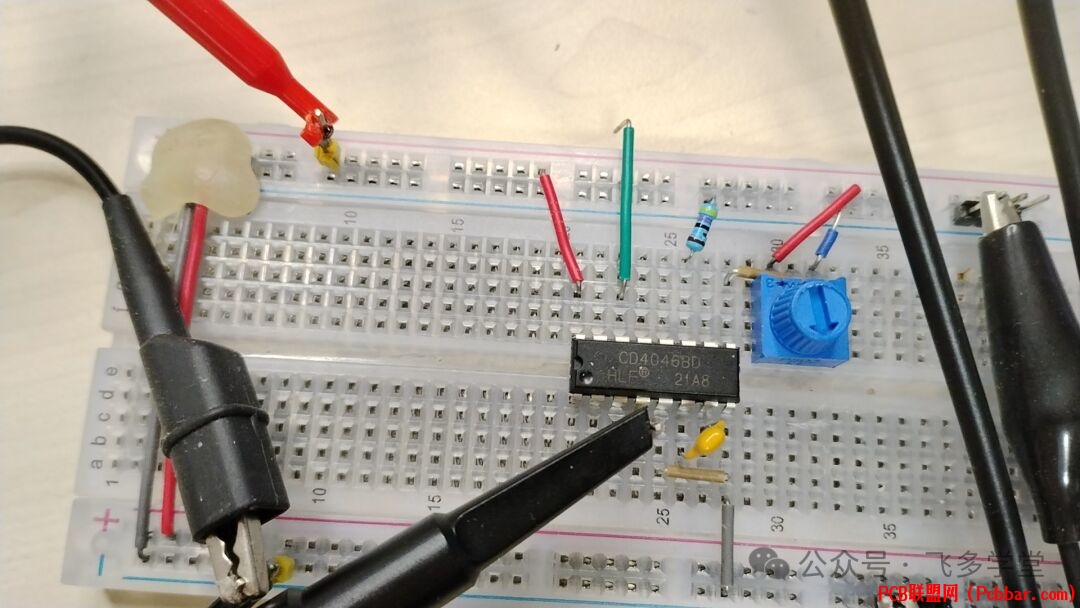

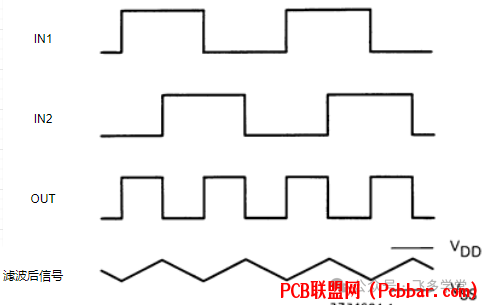

面包板上搭建好的实验电路如下:* }6 L+ s! y- \' f% ^1 x6 q+ f) t/ }

6 n1 M+ |3 L% }/ V# N

211hekw00in64059202336.jpg

+ Y8 U M, K7 w% S, g0 K O9 i* o# n1 v Q: ^' A2 U: ?. f* f; N

示波器通道1探头接 VCO 输出引脚4,当我调节可调电阻,使 9脚 VCO 控制电压不断增大时, 4脚 VCO 输出频率不断随之变大:

% l5 v6 ]: W9 Y1 f* v* `) l, W& H6 w0 q

ll3l1w1xzhi64059202436.gif

4 v) q+ w7 @+ |6 Y! E0 u

4 v) q+ w7 @+ |6 Y! E0 u

4 Ⅰ型鉴相器原理和实验CD4046 内部集成了两种类型的可单独使用的鉴相器。) ]2 t4 @7 s( K7 n( f5 D

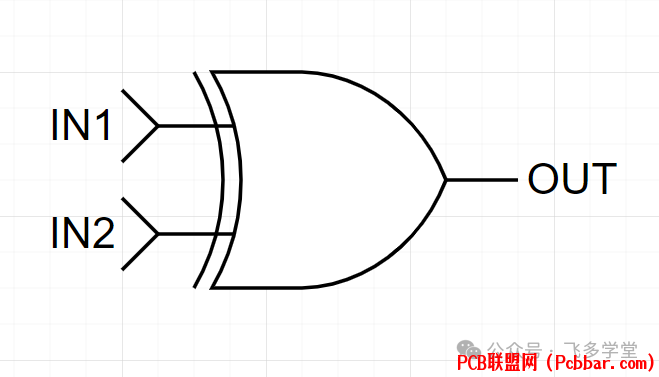

Ⅰ型鉴相器是一个异或门,当两个输入端信号的电平状态相异时(即一个为高, 一个为低电平),输出端信号为高电平;反之,两个输入信号均为高,或均为低电平时, 输出为低电平。

3 t& P( k' Y, @ i% p' @+ c/ q/ E

syjfevgdctv64059202536.png

2 d# _ W7 g# j a9 z

2 d# _ W7 g# j a9 z

% T0 Q3 }4 H. h$ \" W/ \下图是从比较器Ⅰ的输入和输出信号的波形:

. R9 R4 k3 S% j. | }3 _: ^' q1 W& `/ L( \4 Q

pwe1jhg0jmd64059202636.png

- f3 x7 e. Y/ K; G" d" j

- f3 x7 e. Y/ K; G" d" j

1 t, |' d: x1 `/ d# V, m* d

Ⅰ型鉴相器优点:/ r: l4 h: ]# C# T: y

当输入信号有噪音时表现良好简单易用

7 }& E: s: ~; r

2 O3 n$ p. ?9 ~" sⅠ型鉴相器缺点:: u3 X8 ^1 x4 B1 u

可能会锁定到谐波锁定时的相位可能是 0-180°输入应该具有 50% 的占空比没有真正的频率检测& [" w3 P* O; S; o6 Z

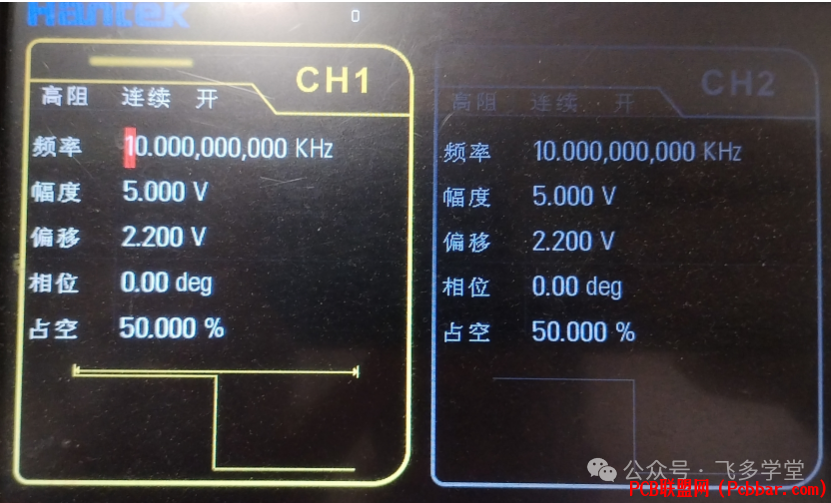

8 d/ }4 J" r+ ]4 V# h/ Q) y) l0 h7 F6 FⅠ型鉴相器实验电路如下:

+ T; R% J& C+ o7 N

T* J5 Q! ?2 l7 r2 G

41iv3xosbc564059202736.png

+ }, S5 c& q4 j7 G/ G# N' z6 H7 r7 f: E. m

我们将鉴相器的两个输入引脚分别接入一路由信号源产生的信号,Ⅰ型鉴相器输出引脚接示波器 CH3 探头。

/ ]; j7 T$ W3 ]9 s6 u- H信号源设置如下:3 G* w- E: [* K7 r1 L; u/ C

7 T5 b; \5 J a8 h; g

iseqxrbmnmy64059202837.png

# `( L$ x2 v8 ]- [9 E' I X( }( _7 j" J

信号源设置两路信号没有相位差时,即鉴相器两路输入信号相位相同时波形如下:7 @) [, y: ?1 m- ]0 _- J4 N

( O& u3 v$ ^+ S1 f- ^

4ytvf041oyd64059202937.jpg

+ a% d$ @6 h) L2 [0 s

+ a% d$ @6 h) L2 [0 s

如果是在手机上阅读本文,点击图片可放大。

9 U# c" I# h4 f D/ BCH1(黄色)接鉴相器输入引脚 14

/ S n q) @" g/ h6 uCH2(青色)接鉴相器输入引脚 33 Q6 M0 w- d% Q5 p# _0 S4 W6 G1 V5 @) M

CH3(紫色)接Ⅰ型鉴相器结果输出引脚 2 Z4 X. v* l% A# o

通过 CH3 看一看到一根根细小的针,说明鉴相器是很灵敏的,检测到了两路信号之间的微小相位差异。) q' b/ i" U. ]( r; ]# _. N# {0 S7 Y6 M

逐渐增大两路信号的相位差至45°波形变化如下:; C* j1 {1 A/ i" y. b

8 f3 K5 b. r9 A9 ]$ W" w' T2 M

0e43jxxl3cw64059203037.gif

( i/ S+ j# a9 S! [

0 w: t# b& A+ s4 r% {6 M信号源逐渐增大 CH2 信号相位至 45° 波形如下:/ _- i* C; c' |0 F) R$ {

$ P: a. V4 V/ V& b' X$ @# F

w3uiihehrwl64059203137.gif

( B1 t; u5 C* T

( B1 t; u5 C* T

I 型鉴相器有一个缺点:无法分辨两路输入信号那个相位在前哪个在后。5 Ⅱ型鉴相器原理和实验Ⅱ型鉴相器也被称为鉴相鉴频器。对应英文是 Phase Frequency Detector, 缩写是 PFD。

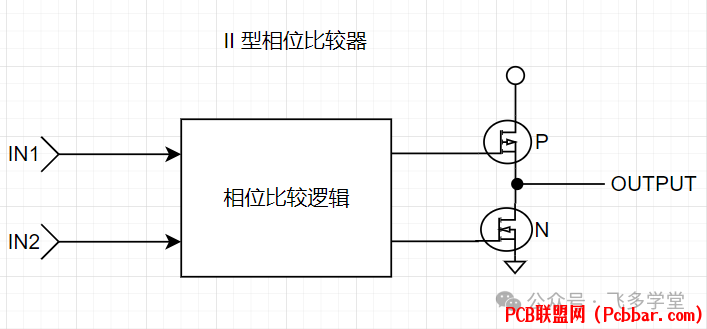

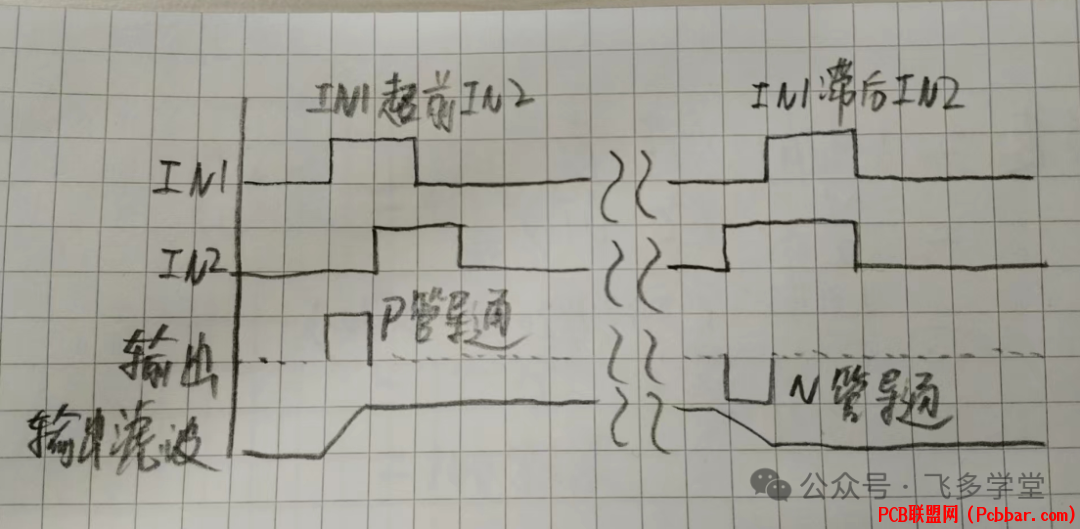

( Z: x2 c# q+ h) M" YⅡ型鉴相器基本电路图如下:& A8 U$ i2 E/ ]; @

ufayigodlgu64059203237.png

' v) u% U7 w. }. j0 i) E

% `0 u5 N% \. H7 {; |0 h相位比较器II是一个边沿控制的数字存储网络。当P-MOS或N-MOS驱动器打开时,它们分别将输出拉高到VDD或拉低到VSS。这种类型的相位比较器只在输入信号的上升沿时进行比较(两路输入信号中的任意一路,以先出现为准),信号(14脚)和比较器输入(3脚)的占空比并不重要。如果两个信号输入频率不同,而N和P驱动器都处于关闭状态(三态),相位比较逻辑会调整其内部电路直至两路输入信号频率相同。8 w: q: _# W! Q' C

如果信号(14脚)和比较器输入(3脚)频率相同,但信号输入滞后于比较器输入相位,那么N型输出驱动器将保持打开状态,时间与相位差相对应。如果信号和比较器输入频率相同,但比较器输入滞后于信号相位,那么P型输出驱动器将保持打开状态,时间与相位差相对应。随后,调整连接到该相位比较器的低通滤波器的电容电压,直到信号和比较器输入在相位和频率上相等。在这个稳定点,N型和P型输出驱动器都保持关闭状态,因此相位比较器输出变成了开路输出,并保持低通滤波器的电容电压恒定。此外,“相位脉冲”输出引脚 1 处的信号为高电平,可用于指示已锁定的状态。因此,对于相位比较器 II,在整个VCO频率范围内,信号和比较器输入之间不存在相位差。此外,当使用此类型的相位比较器时,由于大部分信号输入周期中P型和N型输出驱动器都处于关闭状态,低通滤波器的功耗降低。值得注意的是,对于这种类型的相位比较器,PLL锁定范围等于捕获范围,与低通滤波器无关。在信号输入处没有信号时,相位比较器II将VCO调整到其最低频率。6 J5 x& F4 U2 s4 i

# E" M I3 W; X x9 F

gje0020zncj64059203337.png

: P% E0 x2 g6 W

: P% E0 x2 g6 W

3 r( s9 j6 O7 [# S8 F0 q

Ⅱ型鉴相器 优点:# M7 J6 z2 W, Q) B1 W) A1 d

良好的频率检测不会锁定到谐波输入信号不必具有 50% 的占空比可以在 0° 相位锁定

) G4 C9 X) V1 V, M0 u' B缺点:4 V0 L. S; {( {& ?0 S7 A

更复杂在输入信号有噪音时表现不良9 d8 L& l) `+ w* n& A1 J1 s

5 l3 m! L2 G& ^

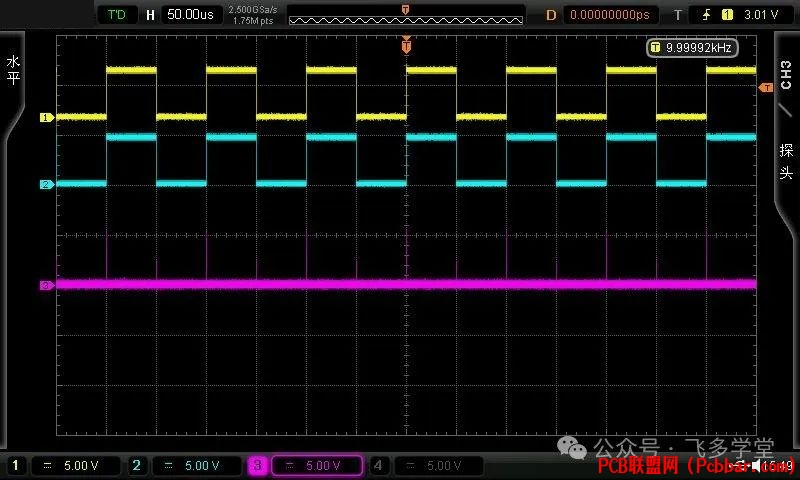

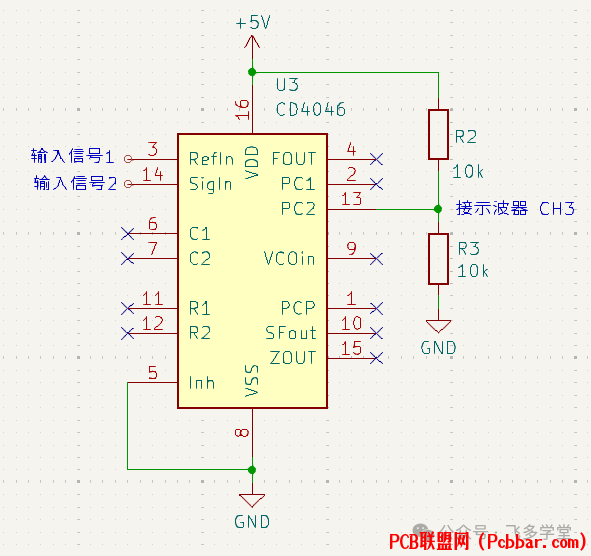

Ⅱ型鉴相器实验电路如下:6 l8 }! e$ A3 X5 A1 b5 g* W0 Y

$ ?: Y; h7 D* A, A7 v! i i

0itikszuxav64059203437.png

) q7 k' I# O4 G, p' @2 U# \8 C7 ^7 h: M$ H4 p6 Y9 N$ M# i

我们在Ⅱ型鉴相器结果输出引脚 13 接了上下拉电阻,因为当两个信号处于同相时,此处为开路,我们通过上下拉电阻给了一个确定的电压。3 u3 t& ` u( o/ l

当两个输入信号同相时波形如下:! r4 ~4 s3 K/ G9 N! L2 g7 Y% b

" z) o+ J9 n& _+ n f8 h

vvnhm301ozq64059203537.jpg

2 | M4 | y# ~6 `1 d0 N6 U; e9 i: J6 p) x7 q* Y

逐渐增大信号源 CH1 使其相位至45°时波形如下:

, ^( c5 `' X# K9 J

~3 ?1 W4 \. @- a( D! t

hu5szr5usi064059203638.gif

5 \0 F5 q9 h/ U! O3 H" }; l# i( g/ @; L6 B

逐渐增大信号源 CH2 使其相位至45°时波形如下:

% O6 V. u9 ?7 }) h1 L' d4 ]3 S, j$ ^* N

qycxkwpoi2564059203738.gif

# R0 X) H* V6 M; t/ a! R/ l! Z

* i. h8 M# e* i2 H3 {! \可以看到,随着相位超前的信号不同,比较结果波形中会对应出现正脉冲和负脉冲,可以籍此判断哪一个信号超前。Ⅰ型鉴相器则只能鉴别出差异,区分不出哪个超前哪个滞后。* G" ]/ f/ W/ Q! e

5 u1 K7 T% w4 W7 D8 T

6 PLL 实验PLL 各部分实验已经完成,我们把闭合整个环路进行实验。

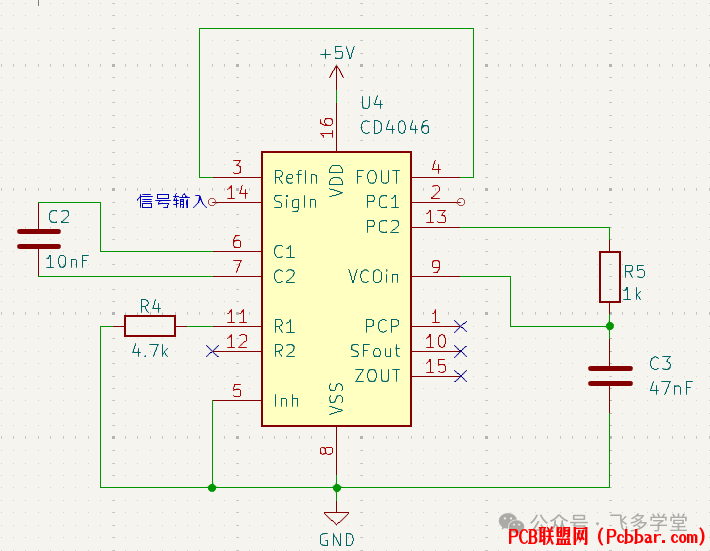

2 | l( N5 x! a/ k3 E- H0 p1 uPLL 环路实验电路图如下:

+ k: J9 ?, J* V: Y& f0 W& ^2 B6 y6 j \7 |" D) z

xuky3kadbou64059203838.png

& m9 [ @# v' E# }7 x

& m9 [ @# v' E# }7 x

9 ]6 B4 b' l& K# e% l鉴相器需要两路输入信号以进行比较。我们使用外部信号源的方波信号作为一路输入信号,接到14脚上。我们把 4 脚 VCO 的输出的脉冲信号接到鉴相器的另一路输入 3 脚上。我们使用13 脚输出的 II 型鉴相器比较结果经低通滤波后驱动 VCO。

& T7 a4 j9 O$ K5 f4 h! h我们 使用 1k 电阻加 47nF 电容组成低通滤波器对鉴相器输出脉冲信号进行滤波,其截止频率为 3.4kHz。) C; l( y/ G0 M2 {

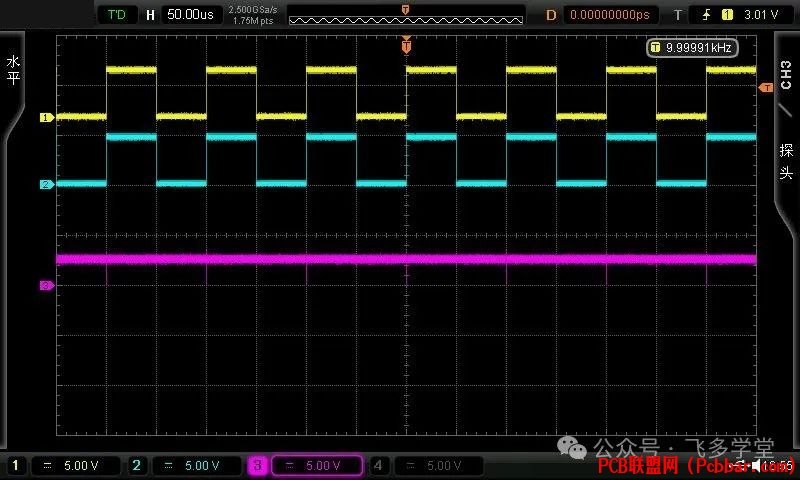

14脚输入 10kHz 波形如下:

1 s* N0 t# h$ w- k7 j1 X0 Z' Z% A& s# i' K6 V! ?& ^& a

1 A$ V" t1 f# K4 P* F8 U- U; _ 1 A$ V" t1 f# K4 P* F8 U- U; _

3 ^) w0 c3 F# t6 Y3 N& Q3 l1 g' K

CH1(黄色)测量的是输入信号,探头接引脚 14。: x2 a; C5 u* O1 S, G* e6 E5 _

CH2(青色)测量的是 VCO 输出信号,探头接引脚 4。

6 j5 _/ V" X" v# K+ X4 {CH3(紫色)测量的是 II 型鉴相器比较结果,探头接引脚 13。, b( ?9 g# y! F8 a! Y( Y

CH4(蓝色)测量的是 I 型鉴相器比较结果,探头接引脚 2。/ s* }' p" M' B( D& c/ M

CH2 是VCO的输出波形,完美的实现了 对 CH1 输入信号的复现和锁定。2 i$ F5 }! j2 z7 u' u: v& w

CH3 波形是 II 型鉴相器比较结果,你可以看到一点点轻微的向上或向下的脉冲。, }4 d5 E$ X& A. g8 q

CH4 波形是 I 型鉴相器的比较结果,我们没有在环路中使用它,放在这里是为了和 II 型鉴相器的结果进行参考。$ W. c1 \2 s9 {1 [

如果我把信号源输入信号频率改为 8kHz 和 13kHz 时, 整个环路依然能够闭合:

; `7 g! |! d) w; j4 E) Q/ W

& i0 M$ X* j3 Q0 m

6 T0 c% Y* @ w& q

. F. g* O0 G( I1 q7 H v, ^5 h6 c 9 ]$ M( }5 i: J 9 ]$ M( }5 i: J

如果是在手机上阅读本文,点击图片可放大。% [$ _. {7 E- y% s. g7 u7 M

输入信号从 8kHz 到 13kHz 范围变化时的波形如下图:5 K" y1 w$ K" w( O

7 A& U3 Z+ q a

+ o& {" y7 p; c4 |. m/ c6 E

9 d6 a" c4 a& s, h# m在 8kHz 到 13kHz 范围内,VCO 输出的脉冲(CH2)始终能和输入信号保持同步,很神奇。+ Z' c% n, V1 |

实验到这里,我们再看一遍如同天书的锁相环定义:9 ^* G' v4 O& C. O

锁相环是利用反馈控制原理实现的频率及相位的控制系统,其作用是将电路输出的信号与其外部的参考信号保持同步,当参考信号的频率或相位发生改变时,锁相环会检测到这种变化,并且通过其内部的反馈系统来调节输出频率,直到两者重新同步,这种同步又称为“锁相”(Phase-locked)。$ F3 P$ ?# w2 [- j

或许会理解这段初看味同嚼蜡的话是什么意思。' L& |5 _' @; W& Q

模拟电路一定要理论和实践相结合,初学理论可能不大理解,放下执念,放下对自己智商的怀疑,做个实验回头再看理论就会好理解很多。3 I( ^' S% k, t6 }% o& w% i

% l, h! E7 A( y7 t4 ]' Y, |8 B! N

% M3 b* I% S& N* L. U$ r- c7 倍频和降频锁相环的一个常见应用是频率合成(Frequency Synthesis)。你可以通过对进入相位检测器的信号进行一些调整来实现这一点,例如,如果在VCO输出和相位检测器之间放一个除以2的分频器:* O( C4 Z" I! n- B; z+ a X* Z

/ G! W+ V9 y# u

$ I- ?& o7 s, t: p/ [2 N7 n. ^- P+ Q

那意味着相位检测器会希望其输入的两个信号在频率和相位上匹配,所以现在如果我们在其输入端从外部输入一个 10 kHz 的信号,那么它希望在其另一个输入端也看到一个 10 kHz 的信号,为了实现这一点,环路中的 VCO 将不得不生成 20kHz 的信号。所以通过简单地进行 2 分频,我们实际上现在创建了一个与该输入信号锁相的信号,但其频率是该输入信号的两倍。: z: o% t* F# j/ E+ B- L& l

我们通过在 VCO 和鉴相器之间加一个分频器,来“欺骗” VCO, 让其输出信号倍频。3 ^% r1 U0 T8 F

如果我们在外部输入信号后面加一个分频器,那将会产生降频的效果,所以如果我将外部参考信号进行分频,那么这将导致VCO的输出电压降低,进而其输出的振荡信号频率降低:

' P% N# J) w% \ F; m' v9 p$ h( H

+ t5 R: `# B. {) y! d - U- g w8 h- O4 {% n" S - U- g w8 h- O4 {% n" S

# D' s8 g: P4 I% {, }$ t4 g倍频实验电路图如下:0 U, |6 N3 y# j: K6 p

7 f- F% m+ u4 V/ B. Q; J1 c

4 e, X! W+ i. [+ d% s2 u" v; M- X: [ 4 e, X! W+ i. [+ d% s2 u" v; M- X: [

% r) H2 J) T+ D3 O$ c. ^

我们使用 CD4013 双 D 触发器芯片进行二分频,把分频后的信号输入到Ⅱ型鉴相器输入引脚3。VCO 的输出接到触发器的输入引脚 3。+ G4 ~! e4 O5 K0 d, j

面包板上安装好的电路如下:- M4 f2 j$ W) o0 e

. k# ]" c# j2 P$ m& f

' b0 {8 i5 \7 |! n# e( e: g" m3 z" M

3 @8 R1 h8 z. O9 c4 f14脚输入 9kHz 频率信号波形如下:$ k: ^! N! p; V

8 ^8 m5 L+ K2 ^/ I0 ] , s: B2 u; |! @* V0 O# w , s: B2 u; |! @* V0 O# w

9 }8 t: _# `; n- Z0 Q/ r

CH1(黄色)测量的是输入信号,探头接引脚 14。

+ Z# c; p E" z& s- ^- M9 g& zCH2(青色)测量的是 VCO 输出信号,探头接引脚 4。

" u/ R7 d& d# d2 bCH3(紫色)测量的是 II 型鉴相器比较结果,探头接引脚 13。

0 A$ i0 |" f( Y5 ]1 ]1 H P$ n. cCH4(蓝色)测量的是 I 型鉴相器比较结果,探头接引脚 2。

' C4 Y# W) ]6 I9 s9 E. }' m输入 9kHz 信号(右上角测出的频率为硬件实现,准确些),VCO 倍频后使用示波器自带的自动测量功能(软件实现)频率为 18.18kHz,不是期望的 18kHz, 可能是测量不准或其他原因导致,本文不做探究。% w9 i) }" [9 u* m: L

8 总结本文介绍了锁相环电路和频率合成的基础知识。锁相环电路可以将两个信号在频率和相位上锁定在一起,用于调频、调幅、频率合成等多种用途。通过实验演示了锁相环电路的工作原理,以及如何通过调节输入信号和反馈信号来实现频率合成。 |

|