高速先生成员--黄刚

对于高速差分信号到底需要控制多少欧姆的阻抗,高速先生相信大部分工程师首先都会看下例如信号的协议文档或者芯片的文档,看看里面有没有推荐的控制阻抗值。例如像PCIE信号,在4.0之后的阻抗会明确要求按照85欧姆来控制,USB阻抗会要求控制90欧姆等。除了这一部分有明确的阻抗要求外,其他没明确要求的高速信号你们会控多少欧姆阻抗呢?就好像为什么PCB的单端走线要控制50欧姆一样,差分走线如果没有明确协议规定,那就按100欧姆来控制。很多工程师其实都不一定很清楚的知道内在的理论和原因,但是也会潜意识的控制100欧姆,可见100欧姆差分线这个观念是多么的深入人心!

/ n: v3 h1 }+ @$ ^* O! N- f4 I

! y+ n) B) O0 M: @4 E$ U4 H

! y+ n) B) O0 M: @4 E$ U4 H但是,深入人心归深入人心,本文想探究的是:100欧姆真的是在任何产品中最好的阻抗选择吗?当然,从反射的理论来说,如果从收发芯片的负载到PCB的每个地方链路的阻抗都完美的做到100欧姆的话,那高速线控100欧姆肯定是最好的选择啦!意味着链路上的任何地方阻抗都匹配,完全没有反射的存在,这还能不好吗?

; n7 }* i% q i' _

; n7 }* i% q i' _

& E9 q" p! `. c _" _

& E9 q" p! `. c _" _

真实情况会怎么样呢?为了能有说服力,本文举2个真实项目的仿真案例,大家一起细品细品哈!

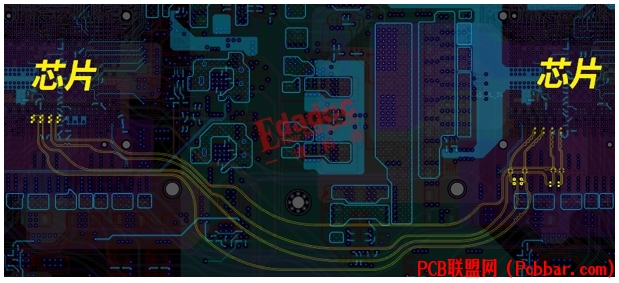

案例一:板内芯片到芯片的25G信号仿真案例

, \$ m) W8 L+ N+ C5 t, j, c

3 O7 b7 f' I) B2 U7 C" l! V+ s. q

3 O7 b7 f' I) B2 U7 C" l! V+ s. q在芯片到芯片的PCB链路中,除了PCB走线外,一定会存在一些阻抗不连续的结构,如上面的案例中,BGA两端会存在过孔,接收端一般还会有交流耦合电容。有一定仿真经验的小伙伴们都知道,像BGA的过孔,电容这个位置的阻抗一般来说都很难做到100欧姆,大部分的case无论怎么优化,都会低于100欧姆。这个时候我们来验证如果这几个阻抗不连续点的阻抗达不到100欧姆,例如做到比较理想的95欧姆左右的情况下,PCB走线分别按照100和降低到95欧姆控制时的无源仿真性能对比。

) H* f& V9 F8 g4 P7 g7 N! A0 d: t

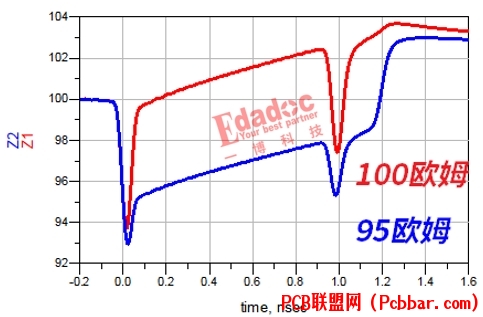

首先我们来看看芯片到芯片链路**R阻抗的对比,也就是PCB走线选择默认的100欧姆和降低到95欧姆来控制时的差异。

, v; k' N) O) @9 ?9 Z

, v; k' N) O) @9 ?9 Z

& [9 S- G, T+ j* I

& [9 S- G, T+ j* I当然从**R阻抗来看,不能很直观的看到差异,于是我们来看另外两个更关键的指标,那就是插损和回损的指标。

( A" j! ~! W/ V" b( p

5 T- K# S( @9 H8 V

5 T- K# S( @9 H8 V

从插损的指标看,在优化好几个不连续点后,虽然100欧姆走线的仿真性能也就很不错了,但是从仿真结果能看到,95欧姆PCB走线的结果更有优势,无论是从回损还是插损的角度看,都是性能更好的一方。

案例二:经过背板连接器的芯片到芯片的25G信号仿真案例

另外一个案例就是跨版的25G信号的case了,整个系统的连接关系如下所示:

, F( B8 {3 l6 y( d$ ~6 r Y

, Y- A# S, p+ I9 c0 |- o

, Y- A# S, p+ I9 c0 |- o前面单板上的BGA过孔的阻抗就不再叙述了,这里要关注的是跨版连接的高速连接器这个地方。本案例中用到的这款高速背板连接器是某知名厂家的产品,是一款在这个速率下很通用,得到有效验证的连接器。

. Z/ R+ a0 W" j/ A( j$ B! _

2 d4 i9 n( U7 a9 b' m

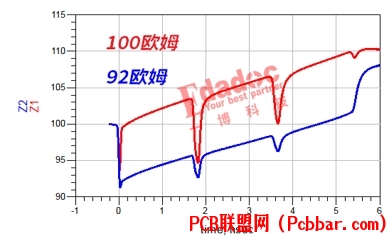

2 d4 i9 n( U7 a9 b' m这款连接器厂家的标称阻抗是多少呢?92欧姆,不是你们想象中的100欧姆哦。我们拿到其中的一对连接器信号的阻抗来看,的确也差不多。90欧姆出头的样子。

. g! o+ b6 O3 |( Z: u) `! \

. g! o+ b6 O3 |( Z: u) `! \

1 Z* N! L' u& n& i0 B

1 Z* N! L' u& n& i0 B

那我们还是一样,这个系统的三块互连的板子,我们分别把高速走线的阻抗按照100欧姆和降低到92欧姆来控制,看看性能的对比。

) Y6 N/ ~1 p6 \, h; K! n

首先我们还是看看整个链路的**R阻抗的对比,能明显看到两个连接器的低点,如下所示:

9 z; J# L# ~: h E

9 z; J# L# ~: h E

' A6 t% Y9 s4 b7 B4 w X

' A6 t% Y9 s4 b7 B4 w X

那么插损和回损的性能对比又是怎么样的呢?还是让大家失望了,三块板子控制92欧姆的走线还是会比100欧姆走线的性能来得好。

( q8 [+ c6 `+ _- E. n* R$ M/ F% u

1 A8 k- s1 d$ [; g- w

1 A8 k- s1 d$ [; g- w当然,这中的理论有点复杂,这里就不展开来分析了。从设计的角度来看,如果没明确的要求,硬件工程师或者设计工程师按照100欧姆来控制高速走线本身也没太大的问题,我们很多case按照100欧姆的差分信号设计也是完全没有问题。本文更多的可能是给大家一种另类的思路,去寻找一些更优的设计方案。但是还是要弱弱的告示下哈,如果不经过比较精确的仿真,还是不要随便去尝试,因为你并不知道多少才是好,只有仿真才能很好的把链路的性能给量化出来,设计的朋友请谨慎使用这招,用得不好还是很容易翻车的哦!

4 ?2 ^- e2 x6 c

4 ?2 ^- e2 x6 c

: Q. h6 v5 o* o. i7 W2 v% A

: Q. h6 v5 o* o. i7 W2 v% A

问题来了:

列举下大家的产品在pcb设计中常见的阻抗不连续的地方,并简单描述下你们的设计优化方法?