|

|

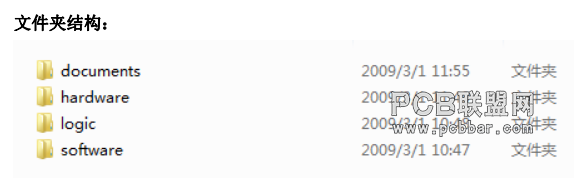

 Documents 文件夹下是项目相关的文档 原理图+PCB PCB封装库+ 软件一起打包分享

 Hardware 文件夹下是项目的硬件设计文件,其中包括 PROTEL99SE 版本和后来转换生

成的 AD6.7 版本,以及智能 PDF 文档。

 Logic 文件夹下是 CPLD 中的逻辑,使用的是 QUARTUS7

 Software 文件夹下是 DSP 中运行的工程及原码。 appnote final.zip 文件中是 MT9V032 数

字 CMOS 采集和验证的程序,运行良好。 SEEDVPM642_loop3.zip 文件中是模拟视频输

入和网络传输的程序,因为时间间隔太久,最近又没有时间验证,所以不能确认功能是

不是完整。但这里依然共享给大家,即便有问题也可为大家提供一些参考。

注:

这是我 08 年做的一个设计,因为当时时间比较短,而且水平有限,所以设计中有好多不严谨的地方。 NAND FLASH 存储这块功能因为当时没有用到,所以还没有调。其他模块功能验证过没有问题。SRAM 布线好多朋友对没有做等长存在疑问。这里我解释一下。 PCB 信号传输表层速度为 120-180ps/inch, 即便差 2.54cm 也就是 130ps 的延时差, 对 133M 的信号而言影响很少,除非自身 PCB 设计有其他重大缺陷。如果非要做等长就要增加板面积或增加层数,加大成本。而且等长后会导致好多短线长度增大,带来的串扰和辐射等问题可能会比不等长更严重。这个 SRAM 布线已经在我设计过的好多产品里做过应用,生产过上万套可稳定工作,大家可以放心。

把它共享出来主要是供大家学习参考用,另外为做类似开发的朋友提供一个用于修改或裁减的基础,希望其中的库及 SDRAM 等布线可以为大家提供便捷。几年前我共享过一个 JD642 的硬件设计,但因为没有逻辑和软件,所以大家在学习和制作过程中遇到问题难以定位,最后无果而终。 DSP 硬件开发需要一定的基础,并不是随便拿来原理图和 PCB 就可以仿制,这个设计可以拿来一时应急,但如果大家对硬件设计感兴趣还是要在空闲的时候多补一些基础知识。

设计不是简单的照抄,而是靠平时的知识积累和经验积累,这个设计中的一些因素旨在为大家提供一个学习的素材,细心消化可以转化为自己的经验,多参考别人的设计有助于自

己水平提升,但如果只是单纯的抄,只会让自己变得更懒,并最终失去对研发的兴趣。希望这份设计能起到积极的作用

|

|

/1

/1